# Parallel Layout Engines: Synthesis and Optimization of Tree Traversals

Leo Meyerovich

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2013-242 http://www.eecs.berkeley.edu/Pubs/TechRpts/2013/EECS-2013-242.html

December 20, 2013

Copyright © 2013, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Parallel Layout Engines: Synthesis and Optimization of Tree Traversals

by

Leo Alexander Meyerovich

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Rastislav Bodík, Chair Professor George Necula Professor David Wessel

Fall 2013

#### Parallel Layout Engines: Synthesis and Optimization of Tree Traversals

$\begin{array}{c} \text{Copyright 2013} \\ \text{by} \\ \text{Leo Alexander Meyerovich} \end{array}$

#### Abstract

Parallel Layout Engines: Synthesis and Optimization of Tree Traversals

by

Leo Alexander Meyerovich

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Rastislav Bodík, Chair

Mobile web browsers and data visualization tools require a performance boost. Parallelization poses an opportunity because commodity computers feature fast and energy-efficient multicore, subword-SIMD, and GPU hardware. However, layout engines in both browsers and visualizations have resisted parallelization thus far. This thesis introduces techniques for parallel computing over trees and applies them to generating layout engines.

Our solution is twofold. First, we show how to specify layout languages in the attribute grammar model of constraints over trees. Second, we address outstanding challenges in parallelizing attribute grammars and computations over trees. Our resulting attribute grammar compiler generates layout engines for various layout languages and parallel hardware.

We provide several individual contributions:

- 1. We specify the functional and parallel behavior of common layout language primitives.

- 2. We present a language for scheduling parallel tree traversals and a static verifier for ensuring a schedule will solve the attributes of an arbitrary layout in a safe order.

- 3. We introduce a parallel programming model where programmers may partially specify the parallel schedule and call an optimizing synthesizer to complete the schedule.

- 4. We design a scheduling algorithm that is fast and modular over scheduling constructs.

- 5. We optimize tree traversals for SIMD hardware by automatically staging dynamic memory allocation and clustering diverging tasks.

- 6. We optimize parallel tree traversals for MIMD architectures through a load-balancing heuristic that approximates work stealing.

To evaluate our approach, we present two case studies. First, we generated the first parallel webpage layout engine that can for the most part render complex sites such as Wikipedia. Second, we generated interactive data visualizations that support up to 1,000,000 data points in real-time. Both case studies have been further validated industrially.

"The Hitchhiker's Guide to the Galaxy has this to say on the subject of flying. There is an art, it says, or rather a knack to flying. The knack lies in learning how to throw yourself at the ground and miss. Pick a nice day, it suggests, and try it. The first part is easy. All it requires is simply the ability to throw yourself forward with all your weight, and the willingness not to mind that it's going to hurt. That is, it's going to hurt if you fail to miss the ground. Most people fail to miss the ground, and if they are really trying properly, the likelihood is that they will fail to miss it fairly hard. Clearly, it's the second point, the missing, which presents the difficulties."

Life, the Universe, and Everything - Douglas Adams

## Contents

| Contents                  |                                               | ii                                                                                                                                                                                                                |                                        |

|---------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| $\mathbf{L}_{\mathbf{i}}$ | st of                                         | Figures                                                                                                                                                                                                           | iv                                     |

| Li                        | st of                                         | Tables                                                                                                                                                                                                            | vii                                    |

| 1                         | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5       | Dissertation Overview  Motivating Example  Mechanizing Layout Languages as Sugared Attribute Grammars  Parallel Layout with Checkable Static Tree Traversal Schedules  Parallel Schedule Synthesis                | 1<br>2<br>3<br>7<br>8<br>11            |

|                           | 1.6<br>1.7                                    | Optimizing Parallel Tree Traversals for MIMD and SIMD                                                                                                                                                             | 13<br>14                               |

| 2                         | <b>Me</b> e 2.1                               | chanizing Layout Languages with Extended Attribute Grammars  Motivation and Approach                                                                                                                              | 15<br>15                               |

|                           | 2.1<br>2.2<br>2.3<br>2.4<br>2.5               | Background: Layout with Classical Attribute Grammar  Desugaring Loops and Other Modern Constructs  Evaluation: Mechanized Layout Features  Related Work                                                           | 17<br>21<br>28<br>38                   |

| 3                         | Par                                           | callel Layout with Checkable Static Tree Traversal Schedules                                                                                                                                                      | 40                                     |

|                           | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Design Goals  Language of Static Schedules  Desugaring Loops  Verification  Case Study: Automatically Staging Memory Allocation for SIMD Rendering Evaluation: Layout as Structured Parallel Visits  Related Work | 40<br>41<br>49<br>55<br>59<br>63<br>66 |

| 4                         |                                               | eallel Schedule Synthesis                                                                                                                                                                                         | 70                                     |

|                           | 4.1                                           | Computer-Aided Programming with Schedule Sketching                                                                                                                                                                | 71                                     |

|              | 4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Generalizing Holes to Syntactic Unification  Fast Algorithm for Schedule Synthesis  Schedule Enumeration  Evaluation  Related Work |     |

|--------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5            | Opt                             | timizing Parallel Tree Traversals for MIMD and SIMD                                                                                | 83  |

|              | $5.\overline{1}$                | MIMD: Semi-static Work Stealing                                                                                                    | 84  |

|              | 5.2                             | SIMD Background: Level-Synchronous Breadth-First Tree Traversal                                                                    | 90  |

|              | 5.3                             | Input-dependent Clustering for SIMD Evaluation                                                                                     | 93  |

|              | 5.4                             | Evaluation                                                                                                                         | 97  |

|              | 5.5                             | Related Work                                                                                                                       | 105 |

| 6            | Con                             | nclusion                                                                                                                           | 108 |

| Bi           | bliog                           | graphy                                                                                                                             | 109 |

| $\mathbf{A}$ | Lay                             | out Grammars                                                                                                                       | 115 |

|              | A.1                             | Sunburst                                                                                                                           | 115 |

|              | A.2                             | Table Layout                                                                                                                       |     |

|              | A.3                             | Multiple Time Series                                                                                                               |     |

|              | A.4                             | <del>-</del>                                                                                                                       |     |

|              |                                 | Box Model                                                                                                                          | 133 |

## List of Figures

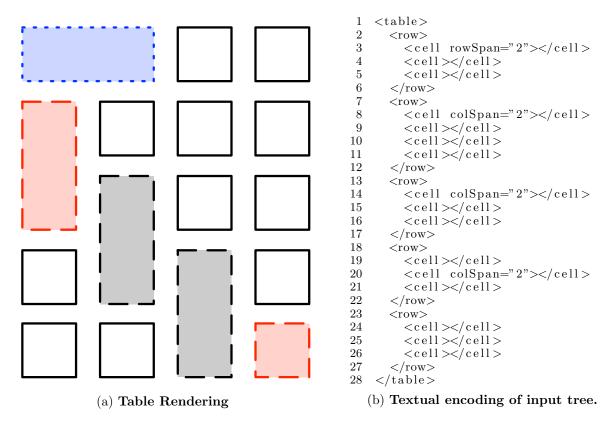

| 1.1  | Layout language of horizontal boxes. Input layout tree, solved output, and                                                                                                                                                                             |            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1 0  | parts of a statically scheduled and sequential layout engine                                                                                                                                                                                           | 4          |

| 1.2  | Attribute grammar defining a layout language of horizontal boxes                                                                                                                                                                                       | 1          |

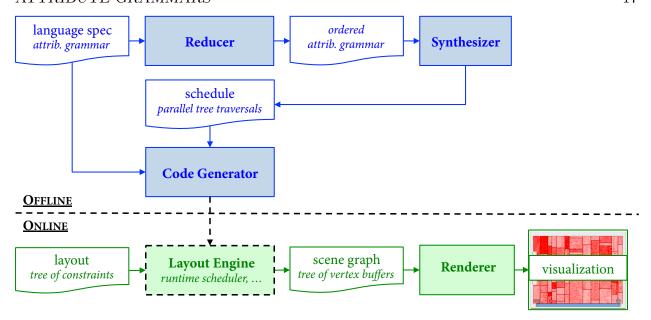

| 2.1  | Layout engine architecture.                                                                                                                                                                                                                            | 17         |

| 2.2  | For a language of horizontal boxes: (a) visualized solution, (b) input tree to solve, and (c) attribute grammar specifying the layout language. Specification language of attribute grammars shown in (c). The language of attribute grammars is shown | 10         |

| 9 g  | in (d)                                                                                                                                                                                                                                                 | 18         |

| 2.3  | straint tree in Figure 2.2 (a). Circles denote attributes, with black circles denot-                                                                                                                                                                   |            |

|      | ing attributes whose dependencies are all resolved, such as input() invocations.                                                                                                                                                                       |            |

|      | Thin lines depict data dependencies and thick lines show production derivations.                                                                                                                                                                       |            |

|      | Chart (b) shows the dependency graph resulting from evaluating all source nodes                                                                                                                                                                        |            |

|      | and treating them as resolved                                                                                                                                                                                                                          | 20         |

| 2.4  | Dynamic attribute grammar evaluator. It selects attributes in a safe order                                                                                                                                                                             |            |

|      | by dynamically removing dependency edges as they are resolved                                                                                                                                                                                          | 20         |

| 2.5  | EBNF syntax for key forms of the functional specification language in                                                                                                                                                                                  |            |

|      | Section 2.3. We omit semicolons and other decorations; see the examples for                                                                                                                                                                            | 21         |

| 2.6  | more detailed forms                                                                                                                                                                                                                                    | <i>Z</i> J |

| 2.0  | production right-hand sides, an encoding that uses a Box non-terminal for indi-                                                                                                                                                                        |            |

|      | rection, and the high-level encoding using interfaces and classes                                                                                                                                                                                      | 23         |

| 2.7  | Input tree as a graph with labeled nodes and edges. Specified in the                                                                                                                                                                                   |            |

|      | JSON notation                                                                                                                                                                                                                                          | 24         |

| 2.8  | Input tree as graph with labeled nodes and edges. Specified in the JSON                                                                                                                                                                                |            |

|      | notation                                                                                                                                                                                                                                               | 25         |

| 2.9  | Trait construct. Adds shared rendering code to the HBox class                                                                                                                                                                                          | 26         |

| 2.10 | Input tree as graph with labeled nodes and edges. Specified in the JSON                                                                                                                                                                                | _          |

|      | notation                                                                                                                                                                                                                                               | 26         |

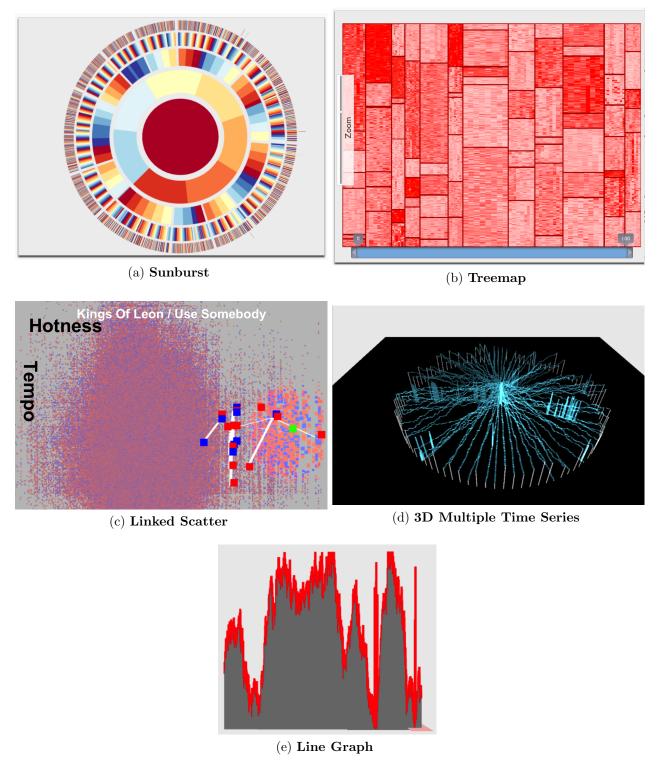

| 2.12<br>2.13 | Visualization screenshots. All except are interactive or animated. Each one was declaratively specified with our extended form of attribute grammars and automatically parallelized. Labels describe whether GPU or multicore code generation was used.  Document layout screenshots.  Document layout screenshots.  Specifying dynamic dependencies. | 29<br>30<br>34<br>35 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

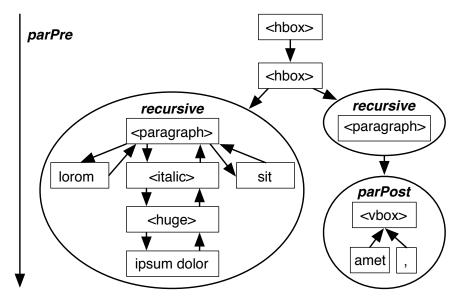

| 3.1<br>3.2   | Sequentially scheduled and compiled layout engine for H-AG Nested traversal for line breaking. The two paragraphs are traversed in parallel as part of a preorder traversal. A sequential recursive traversal places the words within a paragraph. Circles denote nested regions and arrows show data                                                 | 43                   |

| 3.3<br>3.4   | dependencies between nodes and/or regions                                                                                                                                                                                                                                                                                                             | 45<br>46             |

| 3.5          | second for the following traversal                                                                                                                                                                                                                                                                                                                    | 47                   |

|              | attributes a and b are available ahead of time                                                                                                                                                                                                                                                                                                        | 50                   |

| 3.6          | Rewrite rules for loop reduction. Cases of $[\cdot]$ that simply recur are elided.                                                                                                                                                                                                                                                                    | 52                   |

| 3.7          | Correctness axioms for checking a schedule                                                                                                                                                                                                                                                                                                            | 56                   |

| 3.8<br>3.9   | Inter- and intra-region checkers for parPre                                                                                                                                                                                                                                                                                                           | 57                   |

|              | into parallelizable stages                                                                                                                                                                                                                                                                                                                            | 60                   |

| 3.10         | Use of dynamic memory allocation in a grammar for rendering two circles.                                                                                                                                                                                                                                                                              | 61                   |

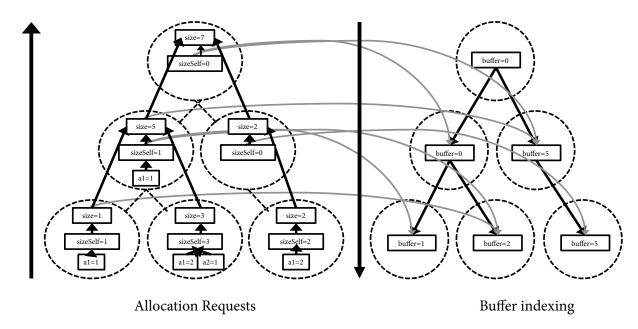

| 3.11         | Staged parallel memory allocation as two tree traversals. The first pass is a parallel bottom-up traversal that computes the sum of allocation requests, and the second pass is a parallel top-down traversal that computes buffer indices. Lines with arrows indicate dynamic data dependencies                                                      | 62                   |

| 4.1          | Trace of synthesizing schedules for H-AG. Note that scheduling of "  " does                                                                                                                                                                                                                                                                           | 75                   |

| 4.2          | not use the optional greedy heuristic                                                                                                                                                                                                                                                                                                                 | 75                   |

| 4.3          | dependencies                                                                                                                                                                                                                                                                                                                                          | 78<br>79             |

|              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                 |                      |

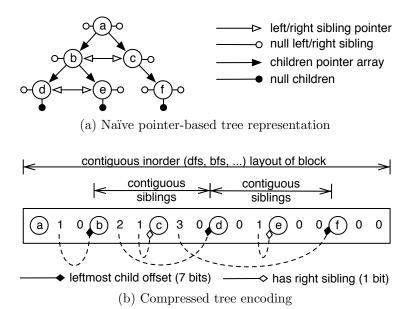

| 5.1  | Two representations of the same tree: Naive pointer-based and optimized. The optimized version employs packing, breadth-first layout, and pointer |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | compression via relative indexing                                                                                                                 | 84  |

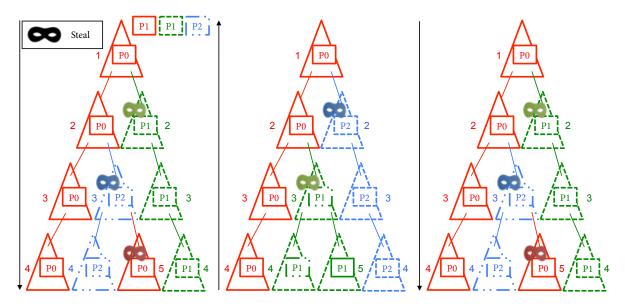

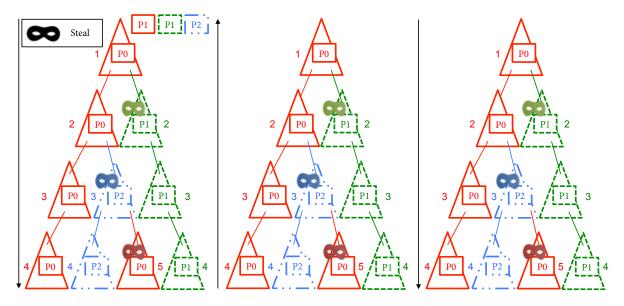

| 5.2  | Simulation of work stealing. Top-down simulated tree traversal of a tiled tree                                                                    |     |

|      | by three processors in three steps                                                                                                                | 86  |

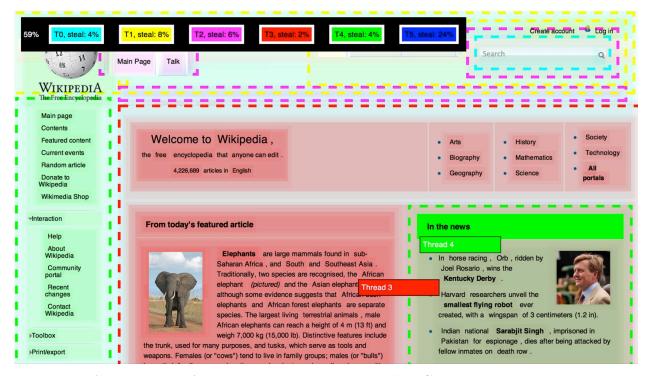

| 5.3  | Simulation of work stealing on Wikipedia. Colors depict claiming pro-                                                                             |     |

|      | cessor and dotted boundaries indict subtree steals. Top-left boxes measure the                                                                    |     |

|      | percentage of steps an individual processor spent stealing rather than computing.                                                                 | 87  |

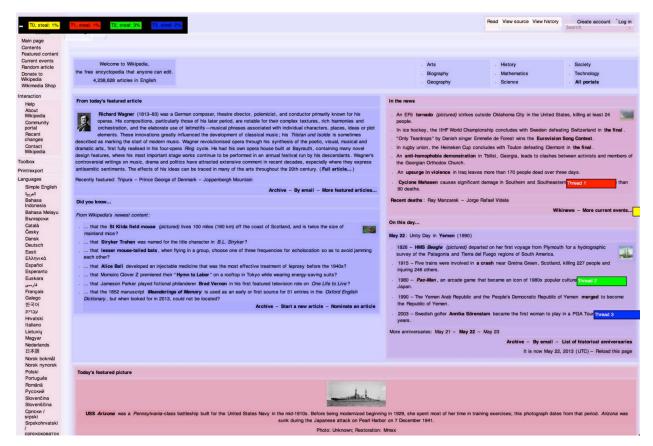

| 5.4  | Temporal cache misses for simulated work stealing over multiple traver-                                                                           |     |

|      | sals. Simulation of four threads on Wikipedia. Blue shade represents a hit and                                                                    |     |

|      | red a miss. 67% of the nodes were misses. Top-left boxes the percent of steps                                                                     |     |

|      | different processors spent stealing                                                                                                               | 88  |

| 5.5  | Dynamic work stealing for three traversals. Tiles are claimed by different                                                                        | 0.0 |

| 5.6  | processors in different traversals                                                                                                                | 89  |

| 5.0  | subsequent ones                                                                                                                                   | 89  |

| 5.7  | SIMD tree traversal as level-synchronous breadth-first iteration with                                                                             | 03  |

| 0.1  | corresponding structure-split data representation                                                                                                 | 91  |

| 5.8  | Simulated vectorization speedup for different schedules. Successive dia-                                                                          | 0 1 |

|      | grams increase the number of vector lanes by a power of two                                                                                       | 94  |

| 5.9  | Clustered parallel preorder traversal.                                                                                                            | 95  |

| 5.10 | Loop transformations to exploit clustering for vectorization                                                                                      | 95  |

| 5.11 | Sequential and parallel benefits of breadth-first layout and staged allo-                                                                         |     |

|      | cation. Allocation is merged into the 4th stage and buffer indexing and tessel-                                                                   |     |

|      | lation form the rendering pass. JavaScript variants use HTML5 canvas drawing                                                                      |     |

|      | primitives while WebCL does not include WebGL painting time (< 5ms). Thin                                                                         |     |

|      | vertical bars indicate standard deviation and horizontal bars show deadlines for                                                                  |     |

| F 10 | animation and hand-eye interaction.                                                                                                               | 99  |

| 5.12 | Multicore versus GPU acceleration of layout. Benchmark on an early                                                                                | 101 |

| 5 12 | version of the treemap visualization and does not include rendering pass Compression ratio for different CSS clusterings. Bars depict compression | 101 |

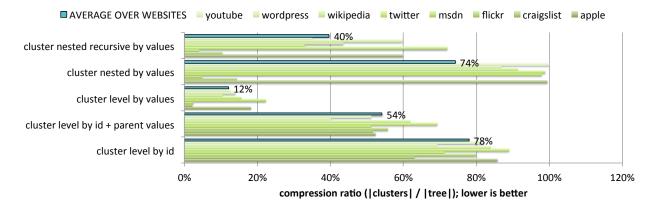

| 0.10 | ratio (number of clusters over number of nodes). Recursive clustering is for the                                                                  |     |

|      | reduce pattern, level-only for the map pattern. ID is an identifier set by the                                                                    |     |

|      | C3 browser for nodes sharing the same style parse information while value is by                                                                   |     |

|      | clustering on actual style field values                                                                                                           | 101 |

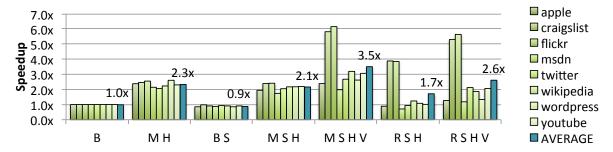

| 5.14 | Speedups from clustering on webpage layout. Run on a 2.66GHz Intel Core                                                                           | 101 |

|      | i7 (GCC 4.5.3 with flags -O3 -combine -msse4.2) and does not preprocessing time.                                                                  | 103 |

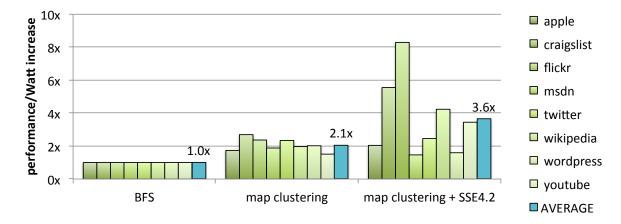

| 5.15 | Performance/Watt increase for clustered webpage layout                                                                                            | 104 |

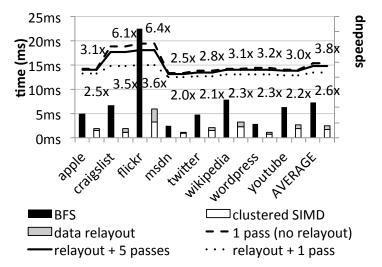

|      | Impact of data relayout time on total CSS speedup. Bars depict layout                                                                             |     |

|      | pass times. Speedup lines show the impact of including clustering preprocessing                                                                   |     |

|      | time                                                                                                                                              | 105 |

## List of Tables

| 3.1 | Lines of code before/after invoking the "@" macro                                  | 65 |

|-----|------------------------------------------------------------------------------------|----|

| 5.1 | Speedups and strong scaling across different schedulers and hardware.              |    |

|     | Baseline is a sequential traversal with no data layout optimizations. FTL is our   |    |

|     | multicore tree traversal library. Left columns show total speedup (including data  |    |

|     | layout optimizations by our code generator) and right columns show just parallel   |    |

|     | speedup. Server = Opteron 2356, laptop = Intel Core i7, mobile = Atom 330. $\cdot$ | 98 |

| 5.2 | Parallel CSS layout engine. Run on a 2356 Opteron                                  | 98 |

#### Acknowledgments

When we first started, most people thought that parallelizing the browser was an impossible idea. That sounded like an idea that should be proven wrong, and I've been lucky to work with mentors who could keep such research paths clear: Ras Bodik and Shriram Krishnamurthi, and over several eye-opening summers, Roger Webster, Ben Livshits, Todd Mytkowicz, Wolfram Schulte, and Herman Venter.

All of the best work was achieved through close collaboration with others: Ari Rabkin, Raluca Sauciuc, and our ever-wonderful research assistants, Matthew Torok and Eric Atkinson. I hope to have been even a small fraction as helpful to the students in the Berkeley Parallelism Lab and the Open Source Quality group as they were to me. Our industrial collaborators were key to navigating the mysteries of browser internals and parallel architectures: the Mozilla team including Rob O'Callahan, Dave Herman, Brendan Eich, Boris Zbarsky, Intel researchers including Moh Haghighat and Gans Srinivasa, Nokia researchers such as Kimmo Kuusilinna and Per Ljung, and Samsung researchers including Tasneem Brutch, and Steven Eliuk. And, of course, thank you to the committee for bearing through this process with continued enthusiasm: George Necula, Krste Asanovic, and David Wessel.

Finally, to my family and Julie, Jono, and Lee: thank you for having traveled with me this far, and I'm excited to see what happens next!

### Chapter 1

### Introduction

At the most practical level, this thesis examines how to parallelize a language for laying out visualizations. By specifying important subsets of layout languages with a restricted form of constraints over trees, we find we can abstract the problem to automatically parallelizing systems of constraints. Our solution combines language design, program synthesis, and high-performance algorithms. We introduce innovatations in each of these areas in order to build our end-to-end system.

Two important applications of parallel layout guide our work. First, mobile web browsers need more efficient layout engines. Power and energy constraints prevent browsers from running on increasingly small devices but with the performance expected on today's bigger form factors. Second, as part of the rise of data science, interactive visualizations need to support magnitudes bigger datasets. We reduce the challenge behind both case studies to that of parallelization. For future small devices, strongly scaling parallelization provides a power- and energy-efficient way to exploit increasing processor capabilities (Asanovic et al., 2006; Jones et al., 2009). For scaling visualizations to bigger datasets, weakly scaling parallelization enables the visualizable dataset size to increase with the number of parallel processors.

Parallelizing layout faces a variety of technical challenges. First, correctly implementing even a sequential layout language already challenges developers. Second, performance concerns about runtime overheads, task scheduling, and data representation requires optimizing parallel tree traversals for different parallel hardware architectures. Third, our optimizations, in turn, impact the form of parallelism that our system must support reasoning about. Finally, in building our system, we needed to optimize the performance of the schedule synthesis algorithm. Prominently, we needed to extend the synthesizer to support different types of parallelism.

Our solution is a synthesizer that statically schedules an attribute grammar as a composition of parallel tree traversals. In the context of a web browser, the input to the synthesizer is the CSS layout language's semantics. The synthesizer generates a sequence of parallel tree traversals such that, given any syntactically well-formed tree with some attributes on nodes already defined, running the fixed schedule will solve all the remaining attributes according to CSS's attribute grammar. A compiler then takes the schedule and code generates a

layout engine that implements it with algorithms optimized for different parallel hardware architectures.

In contrast to our approach, current industrial systems rely upon natural language specifications and reference implementations. Informal specifications suffer from ambiguous and conflicting definitions. Reference implementations often require reverse engineering to understand. Relying upon informal specifications and general reference implementations presents challenges in extending, reimplementing, and aggressively optimizing a layout language.

Achieving automatic parallelization for our applications required novel techniques. First, our language of tree traversal schedules had to be flexible enough to describe useful parallelism in layout language constructs yet restricted enough to facilitate optimization. Second, we needed to create an algorithm to assist in verifying and even inferring the parallel schedule for an attribute grammar. Furthermore, as specifications grew in size, we needed new linguistic constructs to combine manual and automatic scheduling.

Finally, we had to optimize the data representation and runtime schedule of tree traversals in order to see significant speedups from parallelization. For SIMD architectures, we created new staged dynamic memory allocation and divergent task clustering techniques. We optimized for MIMD architectures by designing a semi-static scheduler that combines the low overheads and temporal data locality of static scheduling with the load balancing benefits of dynamic scheduling.

#### 1.1 Dissertation Overview

The remainder of this chapter presents an example of how to build a layout language using existing techniques and then demonstrates how to improve the process with the contributions of each chapter. First, we outline the sequence of improvements.

Chapter 2: Mechanizing Layout Languages with Extended Attribute Grammars. Chapter 2 overviews the attribute grammar formalism and describes how we use it to address the question of how to specify the functional behavior of common layout language constructs. We found attribute grammars to be inexpressive, e.g., lacking facilities for loops and code sharing; therefore, Chapter 2 also introduces expressive extensions to attribute grammars and how we reduce reasoning about the extensions to reasoning about more canonical attribute grammars.

Chapter 3: Parallel Layout with Checkable Static Tree Traversal Schedules. Chapter 3 examines the structure of parallelism latent within layout solving. To express the parallelism, we augmented the attribute grammar formalism with a language for scheduling parallel tree traversals. Whereas an attribute grammar defines attribute values as a system of directed constraints, the scheduling language defines the order to execute those constraints. Using the scheduling language, Chapter 3 identifies and formalizes latent parallelism within common layout language primitives. Finally, in the spirit of the usual attribute grammar verification procedure, Chapter 3 introduces a static schedule verifier that verifies that solving any layout according to a parallel schedule will solve all of the layout attributes without races.

Chapter 4: Parallel Schedule Synthesis. Manually designing parallel schedules for our layout languages proved difficult. Small changes in an attribute grammar may require large changes in the schedule. These changes are non-obvious, tedious, and can even introduce critical performance bugs. Chapter 4 presents a new parallel programming model to address these problems and a schedule synthesis algorithm to perform the underlying automation. Programmers partially specify parts of the parallelization scheme that concerns them and then call an optimizing synthesizer to schedule the remainder. For example, the programmer may choose to specify that the first tree traversal iterates top-down and in parallel over the tree and that the last traversal is sequential and in order, and then rely upon the synthesizer to schedule the remaining traversals and what node attributes to compute within each traversal. The synthesizer will find a correct and optimized completion of the schedule. If it cannot, the synthesizer either signals the presence of potential logical bugs in the functional specification, e.g., missing definitions, or details the unorderable data dependencies in the partial schedule, e.g., cycles.

Chapter 5: Optimizing Parallel Tree Traversals for SIMD and MIMD. The last chapter examines how to optimize parallel tree traversals for SIMD and MIMD hardware. Applying preexisting techniques yielded few speedups and even slowdowns. For both types of hardware, we found the need to optimize the data representation of the tree and the order of nodes within one traversal. For SIMD architectures, we stage parallel memory allocation (Chapter 3) and, in this chapter, show how to cluster tasks that would otherwise diverge based on input. For MIMD architectures, we show how to combine the load balancing benefits of dynamic scheduling with the low-overheads and temporal locality of static scheduling. Our MIMD approach is semi-static. It partitions the tree into tiles and schedules the traversal over tiles with a heuristic that approximates work stealing.

#### 1.2 Motivating Example

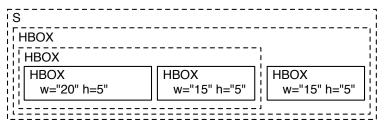

We present most of our techniques in terms of implementing H-AG, a simple layout language for positioning nested horizontal boxes. Figure 1.1 shows key concepts for a layout language. A layout engine implements a layout language and takes as input an attributed tree. For example, leaf nodes may be letters, images, or other media. Leaf nodes likely explicitly define their width and height attributes, but leave their position implicit. An intermediate box would leave both its size and position implicit. Figure 1.1a shows such a partially attributed tree. By defining the intermediate nodes to be horizontal boxes, the designer implicitly constrains their children to be positioned side-by-side, and their width to be the sum of their children widths. Different layout languages support different types of nodes.

The job of the layout engine is to compute all of the undefined attribute values (Figure 1.1b). The input format is typically more sophisticated, e.g., allows percentages rather than just absolute values. Likewise, the solution may solve for more than just the above attributes, e.g., by solving details about borders, margins, and how to render graphics. Because attribute values may depend upon one another, the challenge is to determine a correct

```

<S>

1

1

2

<HBox>

2

<HBox w=50 h=7 x=0 v=0>

<HBox>

<HBox w=35 h=7 x=0 v=0>

<Leaf w=20 h=5/>

<Leaf w=20 h=5 x =0 y=0/>

<Leaf w=15 h=7/>

5

<Leaf w=15 h=7 x=20 y=0/>

5

6

</HBox>

6

<Leaf w=15 h=5/>

<Leaf w=15 h=5 x=35 y=0/>

7

</{\rm HBox}>

8

</HBox>

9

9

(a) Input tree.

(b) Output tree.

annotateSizes(tree.root);

annotatePositions(tree.root);

(c) Schedule of traversals.

def annotatePositions (v):

def annotateSizes (v):

if v.type == HBox:

v.child[0].x = v.x

if v.type == HBox:

3

annotateSizes (v. child [0])

v. child [1].x = v.x + v. child [0].w

4

v.child[0].y = 0

annotateSizes (v. child [1])

4

5

v\,.w\,=\,v\,.\,c\,h\,i\,l\,d\,\left[\,0\,\right].\,w\,+\,v\,.\,c\,h\,i\,l\,d\,\left[\,1\,\right].\,w

v.child[1].y = 0

5

6

6

v.h = max(v.child[0].h, v.child[1].h)

7

annotatePositions (v. child [0])

7

elif v.type == S:

8

annotatePositions (v. child [1])

annotateSizes (v. child [0])

9

8

elif v.type == S:

v.child[0].x = 0

9

v.w = v. child [0].w

10

10

v.h = v. child [0].h

v. child [0]. y = 0

11

annotatePositions (v. child [0])

12

(d) Traversal 1 (bottom-up).

(e) Traversal 2 (top-down).

```

Figure 1.1: Layout language of horizontal boxes. Input layout tree, solved output, and parts of a statically scheduled and sequential layout engine.

order for solving the different attributes.

Figures 1.1c—e provide intuition for the implementation of a typical layout engine. Given any tree of horizontal boxes to lay out, the layout engine solves all the attributes in two traversals (Figure 1.1c). The first traversal computes all of the size attributes (Figure 1.1d); the second computes all of the positions (Figure 1.1e). The second traversals requires size information to compute the positions. Therefore, sequentially sequencing the traversals guarantees that all of the sizes are available before the second traversal runs. The first traversal recursively iterates over the tree to assign all of the width and height attributes based on neighboring attributes (Figure 1.1d). Due to data dependencies between attributes, the traversal only computes the attributes during the bottom-up phase of the recursion.

We call the combination of traversals and the order of attributes to compute within a traversal the *schedule*. A *dynamic* scheduler makes the decisions at runtime. Language implementors avoid dynamic scheduling due to high overheads from tracking every instance of every attribute and when individual data dependencies between attributes are satisfied. Our example uses the more common and efficient *static* scheduling approach, where the relative order of node traversals and attribute computations are fixed at compile time. Note

that because the input tree is not known statically, a static schedule must be correct for all possible input trees. Finally, as schedules such as H-AG's typically require multiple traversals, we further define a *visit's schedule* as the schedule for one tree traversal: the order of node access within the traversal and the order that node attributes are computed within a visit to the node.

Much of our work is in determining how to find efficient schedules and optimize their implementation. Optimizing implementations requires determining how to represent a tree in memory and the order to traverse different nodes on different parallel architectures.

#### Why Parallelization

Layout engine developers, who have already optimized the low-hanging fruit, face diminishing returns from optimization efforts. This thesis explore a new direction by exploiting the shift to parallel architectures in commodity hardware. We explore two forms of parallelization: weak scaling and strong scaling. To optimize for the increasing workload sizes (weak scaling), we must identify significant amounts of concurrency. To optimize for more processors (strong scaling), we need to better utilize modern hardware. We briefly explain these points in turn.

Commodity parallel hardware is already available; it is generally more efficient then sequential alternatives. First, instead of using sequential optimizations with diminishing returns, parallel hardware duplicates simple designs for more linear scaling. For example, if the number of available transistors doubles, a sequential optimization might apply the extra transistors towards an additional 10% realizable performance improvement through a more clever instruction scheduler. The parallel architecture, however, would achieve a 2X improvement by doubling the number of processors. Second, data parallel architectures improve power and energy efficiency for repeated operations. For example, when adding two lists, the computer can fetch data in contiguous segments; instead of decoding a plus instruction for each pairwise sum, it need only decode a single vector addition instruction. We thus focused on exploiting parallelism, and, when possible, data parallelism in particular.

Achieving weak and strong scaling is critical for optimizing the performance of web browsers and data visualization:

- 1. Weak scaling. Layout engines should support bigger input trees. Consider data visualization, where data scientists analyze increasingly large datasets. They need interactive visualizations to likewise scale, which corresponds to handling bigger input trees in our system. Weak scaling fixes the workload size per processor and measures the performance for different workload sizes. Our challenge for achieving weak scaling was to identify significant sources of parallelism that relate to the workload size: data parallelism.

- 2. **Strong scaling.** Existing layouts require better performance. For example, we want to run today's webpages on smaller devices with lower power budgets. Strong scaling fixes the workload and measures the performance for different numbers of processors.

Thus, in addition to identifying parallelism in layout, we must also achieve an efficient implementation.

In summary, hardware trends increasingly point towards parallel architectures, and layout engines require both strong and weak scaling.

#### Why Schedule Synthesis

Schedule synthesis addresses several challenges in parallel programming of layout. Parallel layout was previously proposed by others, such as Brown (1988), but never fully implemented and adopted. This is not for lack of interest. Our proposals for parallelizing components upstream and downstream from the layout solver (Jones et al., 2009; Meyerovich and Bodík, 2010) are being pursued by commercial browser vendors. We have created a schedule synthesizer to solve several problems that have arisen:

- 1. Reasoning about data dependencies. Manually editing both the functional specification and the parallel schedule requires non-trivial reasoning. A small localized change to H-AG's semantics may add a single local data dependency, e.g., an element's height depending on a width, but for an approximation of the global dependency graph, the change may cascade into adding many non-local transitive edges. In turn, the parallel schedule may require many global refactorings, e.g., separating width and height computations into separate traversals. Manually reasoning about and applying schedule changes induced by data dependency modifications is non-trivial.

- 2. Aggressive low-level optimization. Manually implementing a parallel schedule is difficult even if the schedule is fixed. Parallelization is key as a means to improving performance, so a parallel implementation should be faster than existing sequentially-optimized traversals. We found three key classes of optimizations to support: task scheduling, data representation, and existing sequential optimizations. Synthesis is attractive even for sequential tree traversals because manually writing aggressive optimizations requires many man-years of engineering effort.

- 3. Reasoning about parallel schedules. We often guided our automatic parallelizer in what schedule to select. For example, when extending a language with an additional construct, we generally wanted to verify that the previously accepted schedule could still be used. Likewise, for constructs with subtle data dependencies, we would have high-level ideas for how to schedule attributes and then verified our intuition. In both cases, we provided scheduling constraints to the automatic parallelizer.

Exacerbating the above problems is that browser layout engines span hundreds of thousands of lines of code, and for cases of requiring new kinds of data visualizations, we needed designers to build them, even though most designers are not trained in low-level programming.

```

S \rightarrow HBOX

\{ HBOX.x = 0; HBOX.y = 0 \}

HBOX \rightarrow \epsilon

\{ HBOX.w = input_w(); HBOX.h = input_h() \}

HBOX_0 \rightarrow HBOX_1 HBOX_2

\{ HBOX_1.x = HBOX_0.x;

HBOX_2.x = HBOX_0.x + HBOX_1.w;

HBOX_1.y = HBOX_0.y;

HBOX_2.y = HBOX_0.y;

HBOX_0.h = max(HBOX_1.h, HBOX_2.h);

HBOX_0.w = HBOX_1.w + HBOX_2.w \}

```

Figure 1.2: Attribute grammar defining a layout language of horizontal boxes.

## 1.3 Mechanizing Layout Languages as Sugared Attribute Grammars

Chapter 2 presents how we functionally specify layout languages. To aid in this process, it also introduces carefully restricted expressive extensions to the attribute grammar formalism.

Figure 1.2 shows how to declaratively define H-AG as an attribute grammar. It only specifies the functional behavior, such as the width of intermediate nodes being the sum of the widths of their children. In contrast, it does not specify how to schedule the computation as traversals over the tree.

To support automatic compilation into an executable implementation and various forms of program analysis, attribute grammars restrict specifications in three key ways (Kastens, 1980):

- 1. Single assignment. Every node attribute, such as  $HBOX_2.x$ , is defined exactly once. The assignment occurs either in one production where the attribute is attached to the node on the left-hand side of a production  $HBOX \rightarrow Y$ , or on every production where HBOX occurs on the right-hand side. Other languages have similar restrictions, e.g., for functional programming, directed constraints, and dataflow variables.

- 2. Local reads and writes. A node may only access its own attributes or those of neighboring nodes. Our tools use this restriction to combine local reasoning into a global analysis.

- 3. **Pure functions.** Constraints may invoke arbitrary functions such as max as long as they cause no side effects.

In all cases, the restrictions are designed to reason about local and global data dependencies between attributes. With such understanding, attribute grammar tools can answer questions such as whether all attributes are unambiguously defined, and perform optimizations such as finding a safe parallel schedule for computing them.

In order to express common layout language constructs, we had to design expressive extensions to the attribute grammar formalism. For example, in the case of H-AG, our example shows how to compute over binary trees, but popular layout systems use n-ary trees. Many linguistic constructs exist for looping, so our design challenge was to restrict the loop construct enough such that our tree traversal scheduler could analyze uses of it. At the same time, the construct needed to be flexible enough so that we could perform computations such as reductions. For another example, to support designing increasingly large specifications, we needed to introduce constructs for code sharing and information hiding. We show that many of these constructs can be desugared into attribute grammars that resemble the above examples and thus not significantly impact our tool's ability to analyze specifications.

We evaluated our formalism by using it to specify a variety of layout language constructs (Figure 2.11 and Figure 2.13). The include charts, like tree maps, sunbursts, and line graphs, and document layouts, such as grids and nested text with word-wrapping. Finally, we show how to declarative specify rendering, animation, and 3D layouts. Closest to our work, Saraiva and Swierstra (2003) have demonstrated that *fixed* HTML table layouts can be expressed by attribute grammars. However, it is not clear whether (a) their approach expresses the more common and expressive *automatic* HTML table layout algorithm, and (b) if their higher-order attribute grammar formalism is restricted enough for performing our parallelization techniques.

#### 1.4 Parallel Layout with Checkable Static Tree Traversal Schedules

Chapter 3 investigates parallelism latent within common layout language constructs and introduces our scheduling language. We restrict the scheduling language to parallel tree traversals in order to ensure that program analysis, transformation, and optimization is tractable. For example, this chapter shows how to statically verify whether following a particular schedule on an arbitrary input tree will always solve all of the node attributes. Chapters 4 and 5 further exploit the scheduling language restrictions in order to optimize the schedule selection and implementation.

#### Scheduling Language

Identifying the structure of parallelism within a layout language has been an on-going research challenge. For example, consider the proposal by Brown (1988) to parallelize document layout by computing over each page in a different process. The approach does not

work for LaTeXnor webpages due to word-wrapping, variably sized text, and complex figures introducing data dependencies that cross page boundaries. In H-AG, for example, the horizontal offset of a node depends on the sum of the widths of all of the preceding elements: any partitioning of the tree would cut across this transitive data dependency. Finally, even if some elements are known to be isolated from others, such as a frame in a webpage, our solver would have to identify enough isolated computations to saturate the available processors.

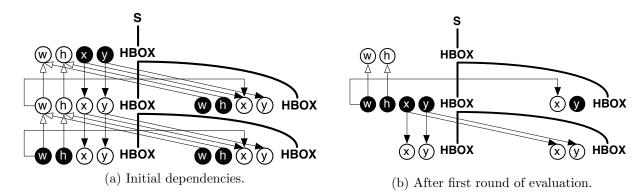

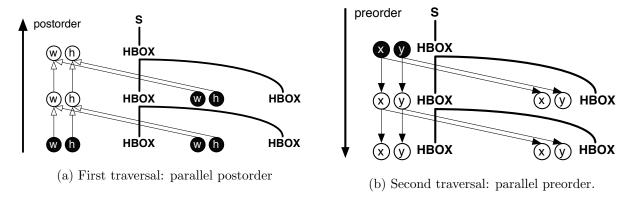

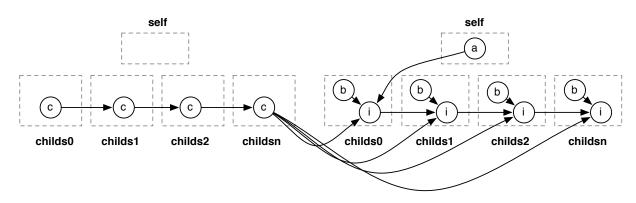

Instead, we split the computation into multiple tree traversals and exploit parallelism within and across traversals. For H-AG, the first traversal computes all the widths, which enables the second traversal to compute all of the horizontal positions in parallel using a top-down (preorder) traversal (Figure 1.1e). As soon as the position of an element and its children widths are known, all of its subtrees may be positioned independently of one another. Figure 3.4b shows the structure of the data dependencies for this second traversal.

We introduced a language for specifying parallel schedules that is orthogonal from the functional specification. For example, the following schedule shows how to parallelize H-AG:

```

1 postorder

2 HBOX<sub>0</sub> \rightarrow HBOX<sub>1</sub> HBOX<sub>2</sub> { HBOX<sub>0</sub>.w HBOX<sub>0</sub>.h }

3 HBOX \rightarrow \epsilon { HBOX.w HBOX.h }

4 ;

5 parPre

6 S \rightarrow HBOX { HBOX.x HBOX.y }

7 HBOX<sub>0</sub> \rightarrow HBOX<sub>1</sub> HBOX<sub>2</sub> { HBOX<sub>1</sub>.x HBOX<sub>2</sub>.x HBOX<sub>1</sub>.y HBOX<sub>2</sub>.y }

```

The schedule specifies the overall parallel structure as a sequence (";") of two types of parallel traversals (postorder and parallel preorder). Within each traversal, it defines the sequence of attributes to evaluate when the traversal reaches a particular type of node (a *production* such as  $S \to HBOX$ ).

Separating H-AG's specification into an attribute grammar for functional behavior and the above schedule enables refactoring one part and then using our automation tools to check or even update the other. Consider the different types of edits in turn:

- Schedule refactoring. An enterprising developer might notice (correctly) that H-AG's computation of y positions may be fused into the first traversal and move it. Our verifier would check that no assignments were lost in the refactoring. Furthermore, if the developer assumes (erroneously) that the x position computations may be scheduled for earlier as well, our schedule verifier would throw an error that the computation of a node's x attribute fails due to a read-before-write on its parent node's x attribute.

- Attribute grammar refactoring. Layout languages evolve so their designers must reason about changes to implicit data dependencies. For example, extending H-AG with vertical boxes (swapping width computations with height ones and x computations for y ones) introduces a dependency between height and y attributes. In the original H-AG language, y attribute computations could be scheduled in the first traversal, but with the extension, they should be computed in the second traversal after heights are computed in the first (Figure 3.4b). Our verifier would check whether H-AG's extension

can be computed under H-AG's original parallel schedule. As part of addressing performance overheads explored in later chapters, we also use the verifier to ensure that extensions to the attribute grammar do not require adding expensive tree traversals.

In both cases, we find that local changes to one specification may globally impact the other. By separating the schedule from the functional specification and restricting both formalisms, we automate manual global reasoning and refactoring (Chapters 3 and 4).

#### **Schedule Verification**

To verify a schedule against an attribute grammar, we show a simple axiomatic system. Every scheduling construct corresponds to a logical judgment. For example, the following rule checks uses of operator ";" for sequencing some traversal p and then traversal q. In particular, it determines whether attributes C will be computed afterwards as long as attributes A are ready beforehand:

$$\frac{\{A\} \ p \ \{B\}}{\{A\} \ p \ ; \ q \ \{C\}} \qquad (seq)$$

It recursively performs the check by invoking two more: it checks p computes attributes B and, given attributes B, that q computes C. An important result of the axiomatic formulation is the use of modular reasoning. While theoretically simple, this avoids implementation difficulties we encountered in trying to extend the analyses proposed by others (Kastens, 1980). To update our verifier to analyze an extension of our scheduling language, we generally only had to add or modify the corresponding judgment. Chapter 4 shows how to reformulate the verifier as a synthesizer, which similarly benefited our synthesizer.

Verification is  $O(A\log A)$  in the number of attributes. The intuition is that an individual axiom check is linear in the number of attributes written, and every schedule AST node corresponds to a check. Intermediate schedule AST nodes partition the set of attributes so that every tree level checks all the attributes, and there are only  $\log A$  levels.

#### **Evaluation on Tricky Schedules**

We conclude Chapter 3 by showing static parallel schedules for common layout language constructs. Some schedules were simply lengthy, but others required non-obvious designs; in several cases, this meant increasing the expressive power of our scheduling language.

As an example, supporting word-wrapped text led to introducing a scheduling construct for describing a restricted form of nested parallelism. Word wrapping places each word to the right of the previous one, except when doing so would overflow a paragraph's boundary, the word goes on the next line instead. The position of each word depends on the position of the previous one, which makes word wrapping a sequential traversal over words.

In general, a document contains many small paragraphs of text that are isolated from one another. Our approach is to sequentially lay out an individual paragraph but to compute

over different paragraphs in parallel. The nested traversal scheduling construct generalizes this approach to embedding one type of traversal within another. It consists of an overall traversal, such as parallel preorder, and when the outer traversal reaches a statically-defined contiguous subtree (e.g., a table consisting of row, column, and cell nodes), a region-specific traversal occurs for that region. When the region traversal terminates, the overall traversal continues for the remainder of the tree.

Two other examples in Chapter 3 include supporting dynamic memory allocation and automatic table layout. We vectorize dynamic memory allocations by grouping them into a prefix sum traversal. Unfortunately, a table forms a DAG rather than a tree, which we address by viewing a table as two minimum spanning trees: one where the parent of a cell is its row, and another where the parent is its column.

#### 1.5 Parallel Schedule Synthesis

Designing a parallel schedule requires enough low-level and global reasoning that we explored automatic scheduling. Chapter 4 shows our solution of generalizing our schedule verifier into a synthesizer. Synthesis further enables us to introduce the new parallel programming abstraction of a *schedule hole* (a form of syntactic unification) and the optimization of schedule autotuning. Finally, we present an optimized synthesis algorithm that avoids exponential explosions.

#### Schedule holes

Programmers specify relaxed schedules by leaving *holes* (Solar-Lezama et al., 2006) for arbitrary terms in the schedule. For example, a programmer may choose to only *sketch* the parallel traversals for H-AG:

```

parPost ?hole1; parPre ?hole2

```

The synthesizer is responsible for determining correct values for  $?hole_1$  and  $?hole_2$ , which are the schedule terms defining the order of attributes for every type of node within the traversals. Leaving a hole for the entire schedule would correspond to fully automatic parallelization.

We generalized schedule holes to syntactic unification. For example, supporting membership queries enables specifying that the synthesizer may pick any type of traversal for each pass as long as it is parallel:

```

Sched = ?hole<sub>1</sub> ?hole<sub>2</sub>; ?hole<sub>3</sub> ?hole<sub>4</sub>,

member(?hole<sub>1</sub>, {parPre, parPost}),

member(?hole<sub>3</sub>, {parPre, parPost})

```

We implemented our scheduling language as an embedded DSL in Prolog, and thereby generalized schedule synthesis to the full power of Prolog (Colmerauer, 1990). In our implementation, Prolog provides the member predicate and performs the overall unification.

#### Optimizing Synthesis and Schedules

The core synthesis algorithm enumerates syntactically valid schedules and tests them with the verifier. Such a design shares the modularity benefits of the axiomatic verifier of Chapter 3, which is critical for simplifying the implementation of our formalism and its extensions. However, brute force enumeration of schedules suffers an exponential explosion in the number of traversals and attributes. Our optimized algorithm addresses both sources of explosion:

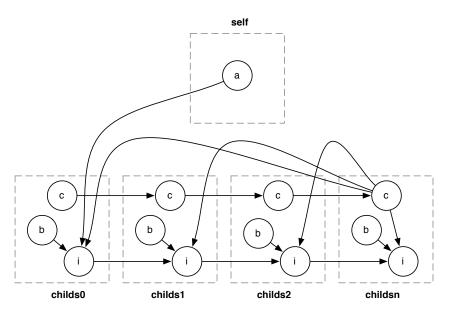

- Prefix expansion of traversals. We observe that if the beginning of a schedule is correct and that a full schedule exists, there must be some correct suffix that, appended to the schedule prefix, will complete the schedule. For example, if the synthesizer finds that width and heights can be computed in an initial postorder traversal for H-AG, it can then need only find subsequent traversals for computing x and y positions. By limiting the search of traversal sequences to successive suffixes, we avoid backtracking and thus the first type of explosion.

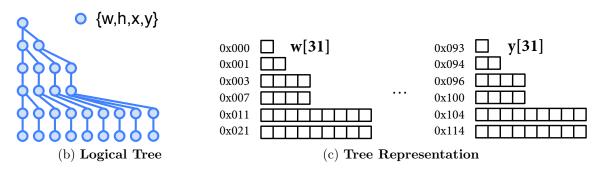

- Iterative refinement of attributes. Our algorithm avoids examining all combinations of attributes for use within a traversal. It initially over-approximates the set of schedulable attributes within a traversal, such as guessing that "{w,h,x,y}" can all be scheduled in the first traversal. Our verifier will reject the schedule, and as an extension to the algorithm presented in Chapter 3, provides an error message of a non-empty subset of the unschedulable attributes, such as "{x}". The synthesizer removes the bad guesses from the over-approximation and repeats the process until either all attributes are eliminated or the verifier accepts the remaining ones. Because the number of refinement iterations is bounded by the number of attributes, our approach avoids the second source of explosion in automatic scheduling. Our iterative refinement differs from a CEGAR loop (Solar-Lezama et al., 2006) by guaranteeing a solution in polynomial time.

Chapter 4 describes additional optimizations, such as incrementalization in the prefix expansion (Bochmann, 1976), topological sorting (Kastens, 1980) to perform the dependency analysis within the verification step, and using a greedy heuristic for minimizing the number of traversals (Kastens, 1980). Our Prolog library implements all of the optimizations: each one represents pruning the enumeration and therefore a cut for Prolog's unifier.

We leveraged the synthesizer towards optimizing the schedule design through autotuning. As already shown, H-AGsupports multiple schedules. We modified the synthesizer to enumerate all of them rather than stopping after finding the first one, and then tested each schedule on programmer-provided inputs and select the fastest. For example, parallel schedules are generally longer than sequential ones and rely upon parallel speedups to offset

the overheads from additional traversals: the hardware architecture impacts the schedule selection.

#### **Evaluation**

We evaluated the ability of our synthesizer to automatically find parallel schedules for common layout language constructs. It finds parallel schedules for all of them. The most notable case was CSS, which uses 9 passes. The difficulty in CSS was that while the solver found parallel traversals for most of the passes, it could not find the nested traversal because the nesting construct triggers an exponential explosion in the synthesis. By providing a sketch of the expected nesting, we guided the synthesizer to the desired result. Sketches were generally of only the traversal sequence and thus took one line of code. The exception was CSS, which required 3 lines for the traversal sequence and 2 lines to describe the nesting.

Our synthesis algorithm was fast enough for interactive use. In most cases, synthesis was within 30s. The CSS specification is a notable exception due to the nesting. Fully automatic parallelization of CSS took 30 minutes, but by providing the 5 line sketch, we reduced the time down to one minute.

## 1.6 Optimizing Parallel Tree Traversals for MIMD and SIMD

Chapter 5 shows how to optimize tree traversals for different parallel hardware architectures. Our problem was that our implementations of existing techniques such as Cilk-style (Blumofe et al., 1995) work stealing and data flattening as in NESL (Blelloch et al., 1994) gave little-to-no speedup on our benchmarks, and in many cases, performed worse than sequential execution due to high overheads and poor data locality. Our solution was to optimize the schedule of nodes within a traversal and the data representation of the tree.

We show different techniques for optimizing parallel tree traversals on MIMD and SIMD hardware:

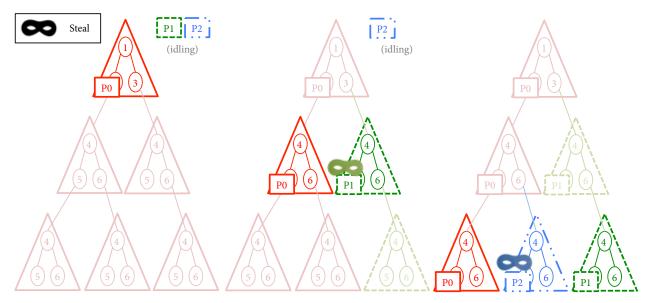

1. MIMD Tree Traversals: Semi-Static Work Stealing We optimized MIMD traversals for low overheads, load balancing, and data locality. We drew inspiration from two sources: work stealing (Blumofe et al., 1995) and tiling (Irigoin and Triolet, 1988). Work stealing provides spatial locality, and tiling avoids further scheduling and data movement overheads. However, work stealing provides poor temporal locality across a sequence of tree traversals because the chance of assigning a node to the same processor across traversals is effectively random. Therefore, as the number of processors increases, the probability of temporal locality decreases and performance suffers. Our solution was to first load balance the initial traversal by dynamically scheduling tiles through a simulation of work stealing. All subsequent traversals then simply reuse the initial schedule. The intuition assumes that (1) the same load balancing applies

across traversals because every node visit generally executes few statements, and (2) by reusing the schedule's assignment of nodes to processors, temporal locality improves.

2. SIMD Tree Traversals: Input-Dependent Clustering The performance of SIMD evaluation suffers when parallel tasks diverge in instruction selection. For example, consider extending H-AG with vertical boxes and then vectorizing the computation of the widths of all nodes in a tree level. Vertical boxes will invoke a max function while horizontal boxes, a sum. If the distribution of vertical and horizontal is random, the instructions for adjacent nodes will diverge. We observe that nodes that share the same type can be computed over in parallel with little divergence. Our SIMD scheduler therefore clusters such nodes at load-time and, instead of vectorizing the loop over all of the nodes in a level, vectorizes smaller loops over clusters with the guarantee of no divergence. Our full implementation involves the selection of several input attributes to consider when clustering, not just the node type.

Note that while both algorithms optimize the traversal schedule, they do so as a runtime refinement of the overall parallel traversals identified by our synthesizer.

For H-AG, we achieved a 6.9X speedup on an 8-core device (9.3X when sequential optimizations are included). For a manual implementation of the SIMD algorithm for one pass of the CSS layout language, we saw a 3.5X speedup on SSE hardware with 4 vector lanes. The SIMD scheduler's load-time clustering cost is amortized over multiple traversals. In the case of the SIMD algorithm, we also measured the improvement in performance-per-Watt: 3.6X. As we expected for vectorization, it is close to the speedup. Finally, our MIMD and SIMD algorithms are complementary. The potential speedup of our approach on commodity hardware features heterogeneous parallelism is thus the product of the individual techniques.

An unexpected result arose for GPUs. GPU architectures suffer from instruction divergence similarly to the subword-SIMD ones we examined. However, in the case of data visualization on GPUs, we achieved significant speedups without clustering. We found that while different levels of the tree hold different types of nodes, most nodes on the same level of the tree are the same, such as the points of a time series chart. The SIMT model of GPUs automatically avoids slowdowns when all threads branch in the same direction. Therefore, laying out a tree map on a GPU achieves a 60.6X speedup under the default breadth-first order. The same property does not hold for document layout, which encounters significant divergence under the default ordering and thus benefited from clustering.

#### 1.7 Collaborators and Publications

Work in this thesis was introduced in prior publications (Jones et al., 2009; Meyerovich and Bodík, 2010; Meyerovich et al., 2013) in joint work with wonderful collaborators: Rastislav Bodík, Krste Asanović, Rose Liu, Chris Jones, Todd Mytkowicz, Wolfram Schulte, Matthew Torok, and Eric Atkinson.

### Chapter 2

# Mechanizing Layout Languages with Extended Attribute Grammars

#### 2.1 Motivation and Approach

This chapter examines the challenges inherent in designing and implementing layout languages and how to use attribute grammars to specify them. We use a running example of a simple layout language and show how our handling of it also applies to common layout language constructs and, more generally, computations over trees. By formalizing layout languages in our extended variant of attribute grammars, we can automate key tasks: checking the language's semantics for errors (Chapter 3), parallelizing it (Chapter 4), and performing aggressive low-level optimizations (Chapter 5). This chapter describes attribute grammars, how we specify layout language constructs with them, and expressive extensions we needed to add to the formalism.

#### Important Properties for Layout Languages

Layout languages extremely common – by one estimate, there are over 634 million websites live in 2012, with 51 million added that year <sup>1</sup>. Beyond the CSS and HTML languages used for webpage layout (Lie and Bos, 1997), designers also use LATEX (Knuth and Bibby, 1986) for document layout, D3 (Bostock et al., 2011) for data visualization, and Swing (Eckstein et al., 1998) for GUI layout in addition to more specialized languages such as Markdown (Gruber, 2004) for simpler text formatting within webpages.

Popular layout languages foster designer productivity by providing many domain-specific abstractions. The alternative is analogous to asking a programmer to write in a low-level language such as assembly: designers should not manually specify the position on a canvas and the style for each element. Instead, layout languages resemble constraint systems where designers declare high-level properties. For example, the high-level program hello world

<sup>&</sup>lt;sup>1</sup>http://news.netcraft.com/archives/2012/12/04/december-2012-web-server-survey.html

specifies that the words hello and world should be rendered, and world world should follow line-wrapping rules for its positioning after hello. Layout languages may provide quite complicated constraints – for example, most document layout languages resort to defining their line wrapping rule in a flexible low-level language. Likewise, they may provide many features, such as in the 250+ pages of rules for the CSS language. Adding to the sophistication, many languages support designers adding their own constraints, such as through macros in LATEX, percentage constraints in CSS, and arbitrary functions in Adobe Flex.

The richness of popular layout languages comes at the cost of complicating their design and implementation:

- Safe semantics. Does every input layout have exactly one unique rendering, i.e., is layout deterministic? Are the constraints restricted enough such that an efficient implementation is feasible for low-power devices, big datasets, and fast animation? When a new layout primitive is added, do these properties still hold? We want an automated way to verify such properties.

- Correct implementation. As a layout language grows in popularity, it grows in features. Likewise, developers will port it to many platforms and optimize it, and in cases such as CSS, reimplement it from scratch. Does the implementation conform to the intended semantics? Conformance bugs for CSS plague developers, and failures to match LATEX's semantics have killed multiple attempts to modernize the implementation. We want an automated way to ensure that the implementation matches the specification.

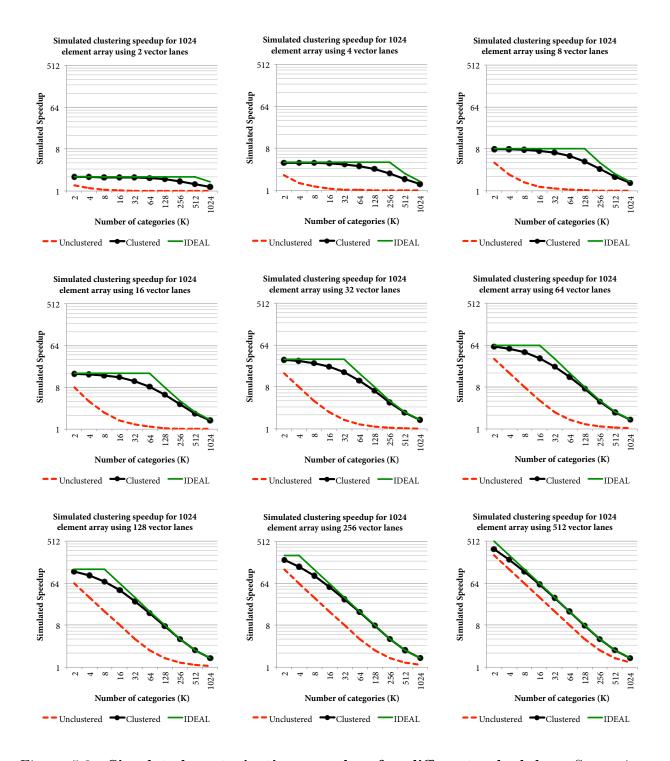

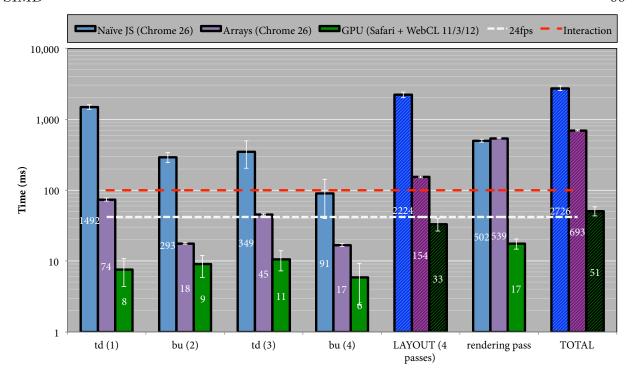

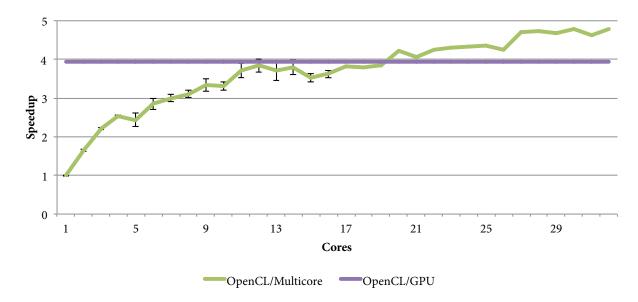

- Advanced implementation. Browser layout engines for CSS are currently over 100,000 lines of optimized C++ code. Rich layout languages thus far have resisted parallelization, and improving the speed, memory footprint, debugging support, and other implementation details is difficult for such a quantity of code. We want automation techniques to lower the implementation burden and perform more aggressive optimizations.