### **Nanoscale SRAM Variability and Optimization**

Seng Oon Toh

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2011-144 http://www.eecs.berkeley.edu/Pubs/TechRpts/2011/EECS-2011-144.html

December 16, 2011

# Copyright © 2011, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Acknowledgement

My research has been supported by the Center for Circuit \& System Solutions (C2S2) Focus Center. The final year of my research was particularly made possible through IBM's generous Ph. D. fellowship. Chip fabrication was donated by STMicroelectronics.

#### Nanoscale SRAM Variability and Optimization

by

Seng Oon Toh

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Tsu-Jae King Liu Professor Paul Wright

Fall 2011

| The diss<br>approve | sertation of d: | Seng Oon | Toh, tit | led Nanc | scale SF | RAM Va | riability              | and ( | Optimizat | ion, is |

|---------------------|-----------------|----------|----------|----------|----------|--------|------------------------|-------|-----------|---------|

|                     |                 |          |          |          |          |        |                        |       |           |         |

|                     |                 |          |          |          |          |        |                        |       |           |         |

|                     |                 |          |          |          |          |        |                        |       |           |         |

|                     |                 |          |          |          |          |        |                        |       |           |         |

|                     |                 |          |          |          |          |        |                        |       |           |         |

| Chair               |                 |          |          |          |          |        | Date                   |       |           |         |

|                     |                 |          |          |          |          |        | Date                   | ·     |           |         |

|                     |                 |          |          |          |          |        | $\mathrm{Dat}\epsilon$ | ·     |           |         |

|                     |                 |          |          |          |          |        |                        |       |           |         |

University of California, Berkeley

### Nanoscale SRAM Variability and Optimization

Copyright 2011 by Seng Oon Toh

#### Abstract

Nanoscale SRAM Variability and Optimization

by

Seng Oon Toh

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

Robust SRAM design is one of the key challenges of process technology scaling. The steady pace of process technology scaling allows doubling memory array sizes, which requires thorough characterization of the impact of sources of process variability on SRAM operation. SRAM arrays are traditionally designed using static noise margins which are known to be optimistic in writeability and pessimistic in read stability. This work presents techniques for characterizing SRAM using dynamic stability metrics, which better represent actual SRAM operating conditions. Quantitative relationships between static and dynamic stability metrics are explored through statistical circuit simulations. Nano-scale SRAM design is traditionally complicated by sources of variability related to physical variability in the structure of the transistors, such as random dopant distribution. This work identifies temporal sources of variability in transistor intrinsic parameters, caused by random telegraph signaling (RTS) noise, which is directly correlated with fluctuation in SRAM performance. A large-scale dynamic stability characterization architecture is introduced and implemented in an early commercial low-power 45 nm CMOS process. This is used to experimentally verify the expected correlations between static and dynamic stability metrics. Outliers of up to 100X which are not correlated between static and dynamic stability metrics were observed and identified to be due to enhanced sensitivity of dynamic stability metrics to variability. Measurement techniques for characterizing temporal sources of variability caused by RTS noise, with particular emphasis on the large-signal bias change response typically encountered in SRAM operation, are used to collect large-scale statistics and to estimate the statistical impact of RTS noise on large SRAM arrays.

An importance sampling algorithm adapted for dynamic stability metrics is developed in this work. This algorithm is used to estimate improvements in SRAM robustness expected from new process technology options such as FDSOI, different bitcell designs such as the 8T-SRAM, as well as several read-assist and write-assist techniques. An optimization framework enabled by this importance sampling algorithm is used to design SRAM arrays with maximum array efficiency through joint-optimization between process technology, bitcell

design, and array organization. In conclusion, this dissertation identifies important sources of variability in nano-scale SRAM and also introduces the relevant optimization tools for performing variability-aware SRAM design.

To my wife, Jessica.

# Contents

| Lis | st of | Figure           | es                                          | V   |

|-----|-------|------------------|---------------------------------------------|-----|

| Lis | st of | Tables           | 3                                           | xii |

| 1   | Stat  | ic and           | Dynamic SRAM Stability                      | 1   |

|     | 1.1   | Introd           | uction                                      | 1   |

|     | 1.2   | Backgr           | round                                       | 2   |

|     |       | 1.2.1            | SRAM Margins                                | 3   |

|     |       | 1.2.2            | SRAM Array                                  | 4   |

|     | 1.3   | Read A           | Access Metrics                              | 5   |

|     |       | 1.3.1            | Static Read Current $(I_{read})$            | 5   |

|     |       | 1.3.2            | Read Access Time $(T_{access})$             | 6   |

|     | 1.4   | Read S           | Stability Metrics                           | 6   |

|     |       | 1.4.1            | Static Read Stability Margins               | 6   |

|     |       | 1.4.2            | Critical Read Stability $(T_{read})$        | 7   |

|     | 1.5   | Writea           | ability Metrics                             | 7   |

|     |       | 1.5.1            | Static Writeability Margins                 | 7   |

|     |       | 1.5.2            | Critical Writeability $(T_{write})$         | 8   |

| 2   | Dyn   | amic S           | Stability Characterization                  | 11  |

|     | 2.1   | Dynan            | nic Stability Characterization Architecture | 12  |

|     |       | 2.1.1            | Programmable Pulse Generator                | 12  |

|     |       | 2.1.2            | Word-line Sampler                           | 14  |

|     |       | 2.1.3            | Non-Destructive Read-Back                   | 15  |

|     |       | 2.1.4            | Built-In-Self-Test                          | 16  |

|     | 2.2   | $45~\mathrm{nm}$ | CMOS Implementation                         | 16  |

|     | 2.3   |                  | rement Results                              | 17  |

|     |       | 2.3.1            | Pulse Generator                             | 18  |

|     |       | 2.3.2            | Read Access Time                            | 18  |

|     |       | 2.3.3            | Critical Writeability                       | 20  |

|     |       | 2.3.4            | Critical Read Stability                     |     |

|   | 2.4  | Impact   | of Assist Techniques                                             |

|---|------|----------|------------------------------------------------------------------|

|   |      | 2.4.1    | Write Assist                                                     |

|   |      | 2.4.2    | Read Assist                                                      |

| 3 | Ran  | ndom T   | elegraph Signal and SRAM Variability 25                          |

|   | 3.1  | Introdu  | action                                                           |

|   | 3.2  |          | ics of Random Telegraph Signal                                   |

|   |      | 3.2.1    | Background                                                       |

|   |      | 3.2.2    | Bias and Temperature Dependence                                  |

|   |      | 3.2.3    | Dynamic Behavior Response under Large-Bias Changes 35            |

|   |      | 3.2.4    | Alternating-Bias Technique                                       |

|   | 3.3  | Amplit   | udes of Random Telegraph Signaling Noise                         |

|   |      | 3.3.1    | Background                                                       |

|   |      | 3.3.2    | Empirical Bias-Dependent Model                                   |

|   | 3.4  | Impact   | of Random Telegraph Signal on Static SRAM margins 48             |

|   |      | 3.4.1    | 45 nm SRAM Transistors                                           |

|   |      | 3.4.2    | Static Write Margin                                              |

|   | 3.5  | Impact   | of Random Telegraph Signal on SRAM Dynamic Stability 57          |

|   |      | 3.5.1    | RTS in pull-down NMOS transistor 1 61                            |

|   |      | 3.5.2    | RTS in pull-up PMOS transistor 2                                 |

|   |      | 3.5.3    | RTS in pull-up PMOS transistor 1                                 |

|   |      | 3.5.4    | RTS in pass-gate NMOS transistors                                |

|   |      | 3.5.5    | Statistical Distributions and Implications to SRAM Robustness 65 |

|   | 3.6  | Correla  | ation Between RTS and NBTI                                       |

| 4 | Stat | tistical | Estimation of SRAM Dynamic Stability 70                          |

|   | 4.1  |          | action                                                           |

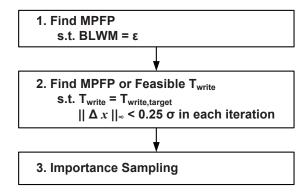

|   | 4.2  |          | ance Sampling and Most Probable Failure Point Search             |

|   | 4.3  | -        | ance Sampling and Dynamic Stability                              |

|   |      | _        | Dynamic Read Stability                                           |

|   |      |          | Dynamic Writeability                                             |

|   |      |          | Dynamic Read Access                                              |

|   | 4.4  |          | ance Sampling with non-Gaussian Distributions                    |

|   |      | 4.4.1    | Lognormal Distribution                                           |

|   |      | 4.4.2    | Random Telegraph Signal and Dynamic Read Stability 86            |

| 5 | Sto  | chastic  | Optimization of SRAM Bitcell and Array 92                        |

|   | 5.1  |          | action                                                           |

|   | 5.2  | Bitcell  | Optimization                                                     |

|   |      | 5.2.1    | Global Process Variation                                         |

|   |      | 5.2.2    | $V_{DD}$ Scaling                                                 |

|    |                  | 5.2.3  | Bitcell Variety       | 95  |  |  |

|----|------------------|--------|-----------------------|-----|--|--|

|    |                  | 5.2.4  | 8T SRAM               | 96  |  |  |

|    |                  | 5.2.5  | Process Technology    | 99  |  |  |

|    | 5.3              | Array  | Optimization          | 101 |  |  |

|    |                  | 5.3.1  | Read and Write Assist | 102 |  |  |

|    |                  | 5.3.2  | Bit-line Capacitance  | 103 |  |  |

|    |                  | 5.3.3  | Array Segmentation    | 104 |  |  |

| 6  |                  | clusio |                       | 111 |  |  |

|    | 6.1              | Key C  | ontributions          | 111 |  |  |

|    | 6.2              | Future | e Work                | 113 |  |  |

| Bi | Bibliography 115 |        |                       |     |  |  |

# List of Figures

| 1.1        | SRAM array VDD reported in ISSCC and VLSI (2004-2010) and ITRS predictions                                                                                                                                                                                                                                                                                                                              | 2        |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2        | Schematic of an SRAM bitcell                                                                                                                                                                                                                                                                                                                                                                            | 2        |

| 1.3        | (a) Schematic of bitcell for SRAM margin measurement. (b) Static noise margin (SNM) extraction. (c) Write margin ( $I_{write}$ ) extraction                                                                                                                                                                                                                                                             | 9        |

| 1.4        | Schematic of an $m \times n$ SRAM array                                                                                                                                                                                                                                                                                                                                                                 | 4        |

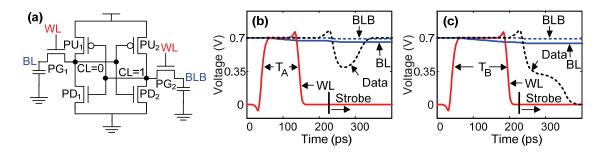

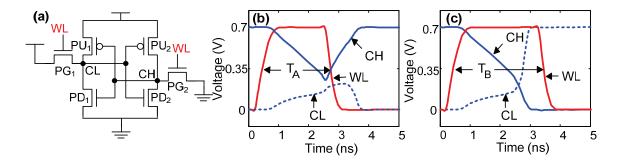

| 1.5        | (a) Schematic of a 6-T SRAM cell storing a 0 on the left internal node. (b) Simulated waveforms corresponding to failed read access with pulse-width, $T_A$ . Output of the sense-amplifier $(Data)$ resolves to the incorrect value. (c) Simulated waveforms corresponding to successful read access with a longer pulse-width, $T_B$ . Output of the sense-amplifier $(Data)$ resolves to the correct |          |

|            | value.                                                                                                                                                                                                                                                                                                                                                                                                  | 6        |

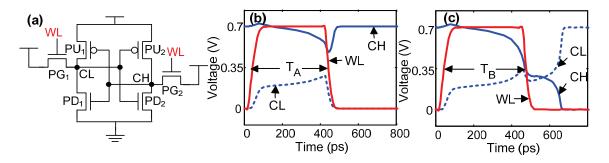

| 1.6        | (a) Schematic of a 6-T SRAM cell under read stress. (b) Simulated waveforms corresponding to read stable access with pulse-width, $T_A$ . The state of the bitcell is retained after read operation. (c) Simulated waveforms corresponding to read upset with a longer pulse-width, $T_B$ . The state of the bitcell is                                                                                 |          |

|            | accidently flipped by the read operation                                                                                                                                                                                                                                                                                                                                                                | 8        |

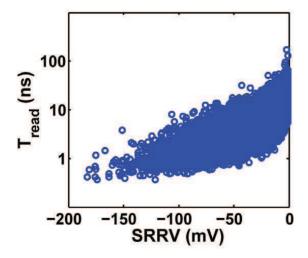

| 1.7        | Simulated scatter plot showing the correlation between critical read stability $(T_{read})$ and negative static read margin (SRRV)                                                                                                                                                                                                                                                                      | 8        |

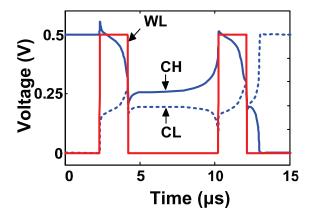

| 1.8        | Simulated waveforms corresponding to an SRAM bitcell under read-after-read                                                                                                                                                                                                                                                                                                                              | _        |

| 1.9        | access                                                                                                                                                                                                                                                                                                                                                                                                  | Ć        |

|            | into the bitcell                                                                                                                                                                                                                                                                                                                                                                                        | 10       |

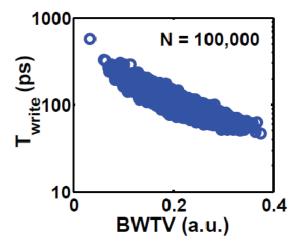

| 1.10       | Simulated scatter plot comparing critical writeability $(T_{write})$ and static write margin (BWTV) obtained from Monte-Carlo simulations                                                                                                                                                                                                                                                               | 10       |

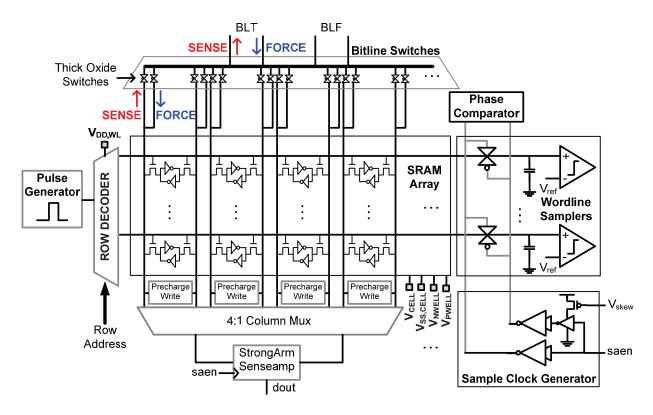

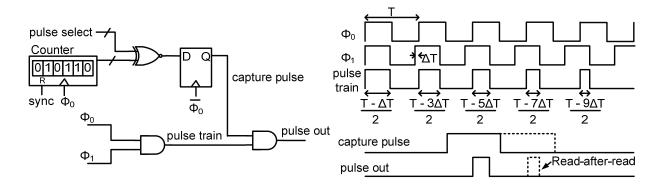

| 2.1<br>2.2 | SRAM array organization for static and dynamic stability characterization Frequency mixing programmable pulse generator with corresponding waveforms.                                                                                                                                                                                                                                                   | 12<br>13 |

|            |                                                                                                                                                                                                                                                                                                                                                                                                         |          |

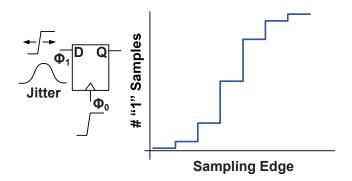

| 2.3  | Statistics at the output of a flip-flop sub-sampling $\phi_1$ using $\phi_0$ with jitter                                                                                                         | 13              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

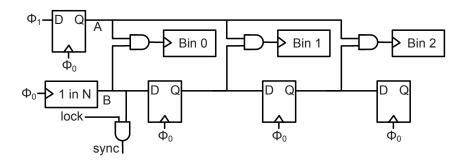

| 2.4  | Architecture of averaging sync generator                                                                                                                                                         | 14              |

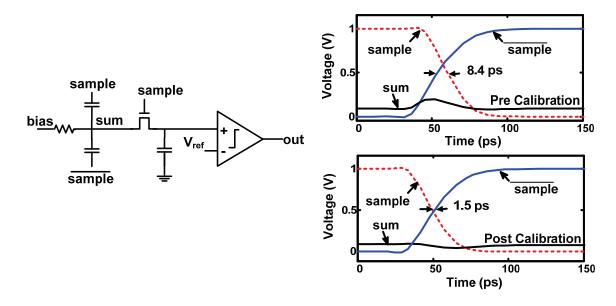

| 2.5  | Capacitive summing phase comparator and simulated waveforms before and                                                                                                                           |                 |

|      | after calibration.                                                                                                                                                                               | 15              |

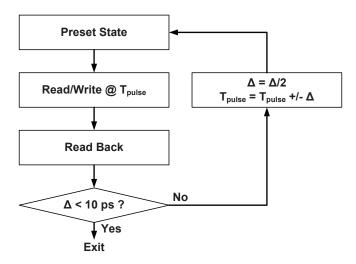

| 2.6  | Built-In-Self-Test state machine for finding the critical word-line pulse width.                                                                                                                 | 16              |

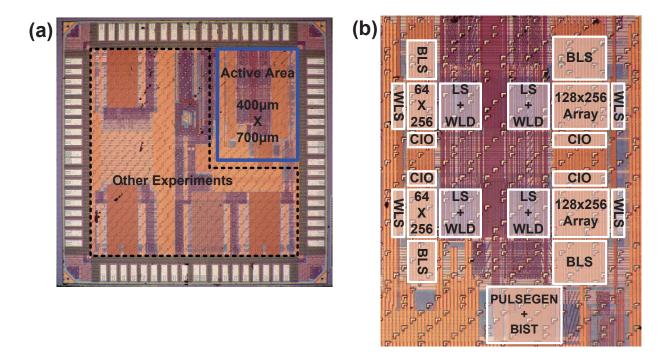

| 2.7  | (a) Die photo of the 45 nm CMOS test chip. (b) Die photo of active area. BLS: bitline switches; WLS: word-line samplers; LS+WLD: level shifters and word-line drivers; CIO: column I/O circuitry | 17              |

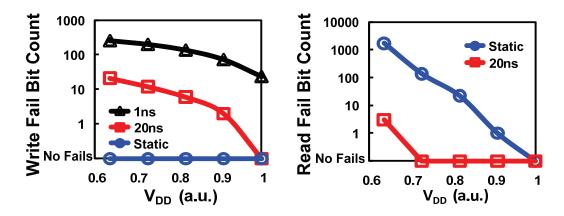

| 2.8  | SRAM writeability and read stability fail bit count measured from a 45nm CMOS SRAM                                                                                                               | 18              |

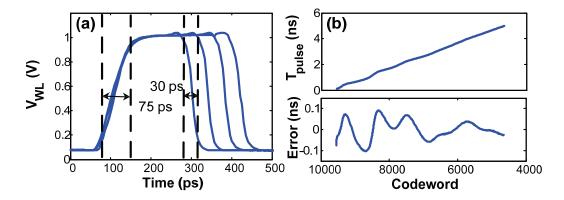

| 2.9  | Plots of (a) multiple sub-sampled word-line waveforms and (b) codeword to                                                                                                                        |                 |

| 2.5  | pulse width transfer function and measured error                                                                                                                                                 | 19              |

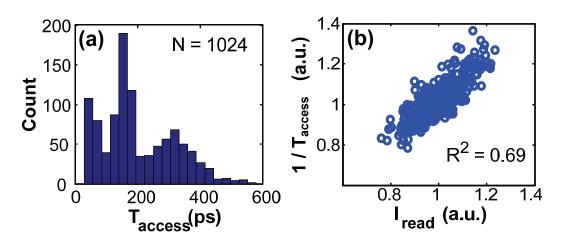

| 2.10 | (a) Histogram of measured read access time. (b) Scatter plot showing correlation between read access time and static read current after normalization                                            |                 |

| 0.44 | with sense-amplifier offset voltage and bit-line capacitance                                                                                                                                     | 19              |

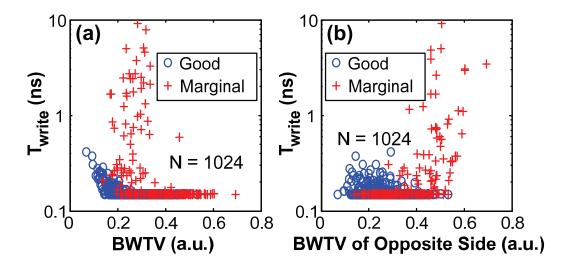

| 2.11 | Critical writeability vs. static write margin of (a) same side and (b) opposite side of SRAM cell measured at $V_{DD,low}$                                                                       | 20              |

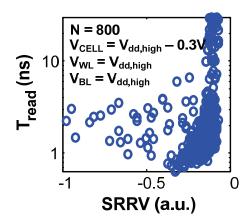

| 2.12 | Critical read stability versus static read margin                                                                                                                                                | 21              |

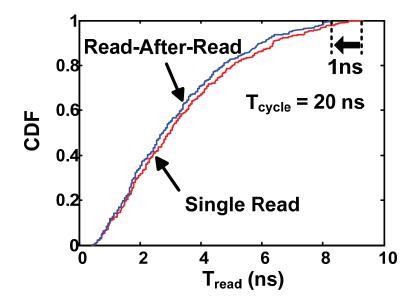

| 2.13 | Statistical distributions of critical read stability under single read and read-                                                                                                                 |                 |

|      | after-read access with 20 ns clock period                                                                                                                                                        | $2\overline{2}$ |

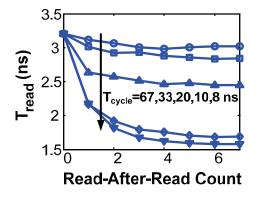

| 2.14 | Critical read stability of a selected bitcell as a function of the number of read-after-read cycles. The different curves correspond to the period of the read-after-read cycles.                | 22              |

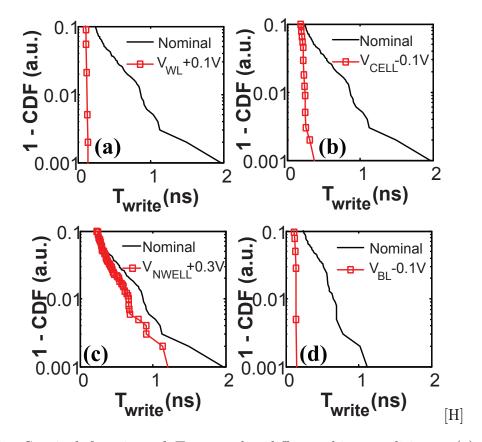

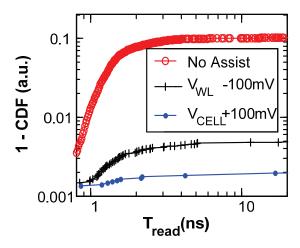

| 2.15 | Survival function of $T_{write}$ under different bias conditions: (a) Word-line boosting; (b) $V_{CELL}$ under-drive; (c) PMOS reverse body-bias; (d) Negative                                   |                 |

| 2.16 | bit-line. Survival function of $T_{read}$ without assist techniques, with -100 mV word-line bias offset and with +100 mV $V_{CELL}$ offset                                                       | 23<br>24        |

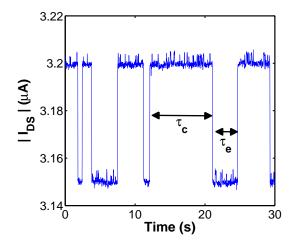

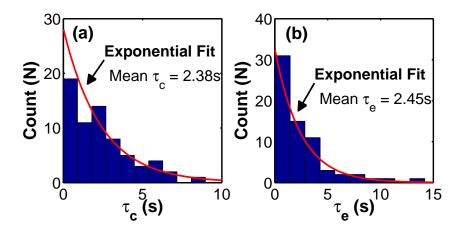

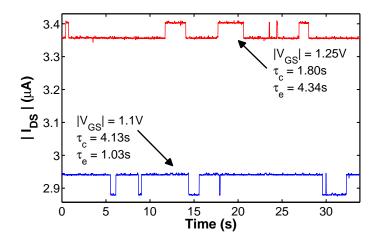

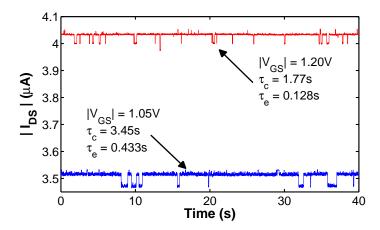

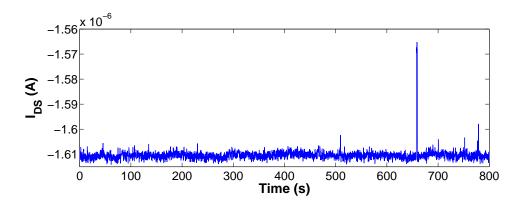

| 3.1  | Drain current measured from a PMOS SRAM transistor showing RTS                                                                                                                                   | 27              |

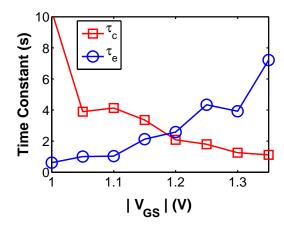

| 3.2  | Exponential fit of extracted time constants corresponding to (a) time until capture $(\tau_c)$ and (b) time until emission $(\tau_e)$                                                            | 27              |

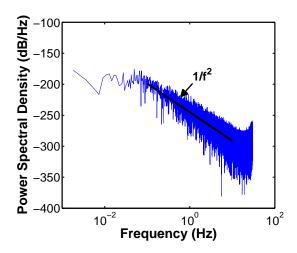

| 3.3  | Power spectral density of RTS drain current measurement                                                                                                                                          | 28              |

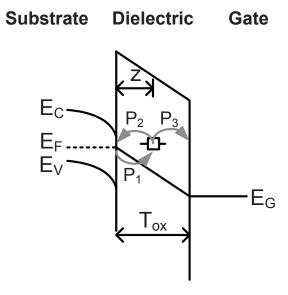

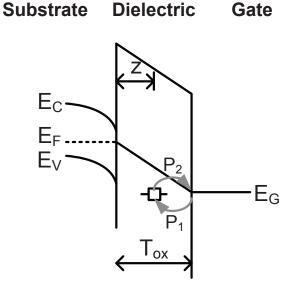

| 3.4  | Energy band diagram of oxide trap with tunneling probabilities                                                                                                                                   | 28              |

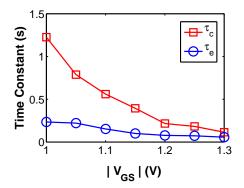

| 3.5  | Drain current of PMOS SRAM transistor under different gate biases                                                                                                                                | 30              |

| 3.6  | Dependence of $\tau_c$ and $\tau_e$ on gate bias                                                                                                                                                 | 31              |

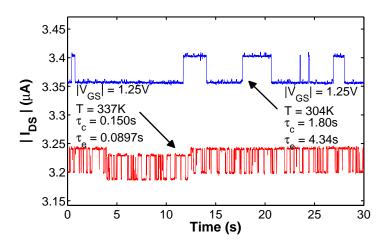

| 3.7  | Drain current of PMOS SRAM transistor at different temperatures                                                                                                                                  | 31              |

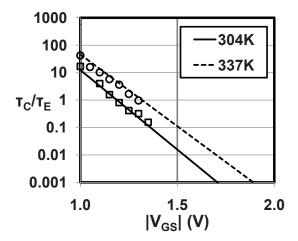

| 3.8  | Measured mark-space ratio at different gate bias and temperatures with extrapolation. Lines indicate exponential fits.                                                                           | 32              |

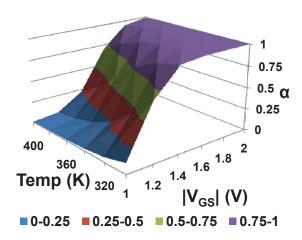

| 3.9  | Surface contour of average trap occupancy ( $\alpha$ ) as a function of gate bias and temperature, extrapolated using Equation 3.2 with $K=26$ and $\frac{z}{T}=0.35$ .                          | 32              |

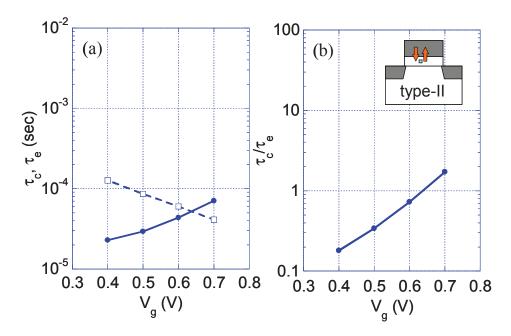

| 3.10 | (a) $V_{GS}$ dependence of $\tau_c$ (filled circles) and $\tau_e$ (open squares) and (b) mark-                                   |    |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

|      | space ratio of a type II trap. Reference [53]                                                                                    | 33 |

| 3.11 | Band diagram of type II oxide trap with tunneling probabilities                                                                  | 34 |

| 3.12 | Drain current of PMOS SRAM transistor, with type III, under different gate                                                       |    |

|      | biases                                                                                                                           | 35 |

| 3.13 | Type III trap dependence of $\tau_c$ and $\tau_e$ on gate bias                                                                   | 35 |

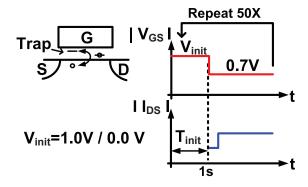

| 3.14 | Cross-section of transistor with oxide trap as well as associated waveforms for                                                  |    |

|      | characterizing the response of RTS to large-bias changes                                                                         | 36 |

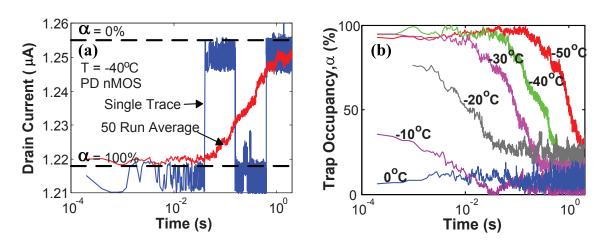

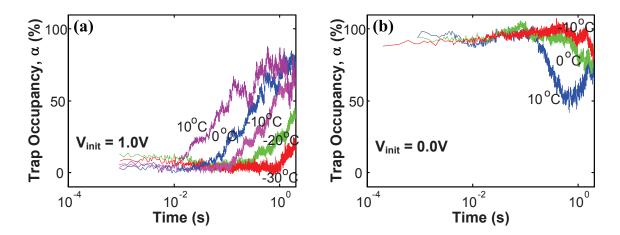

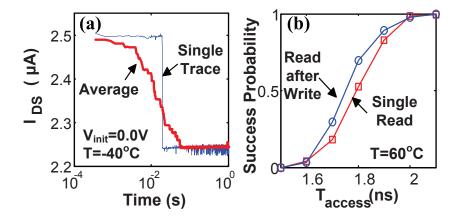

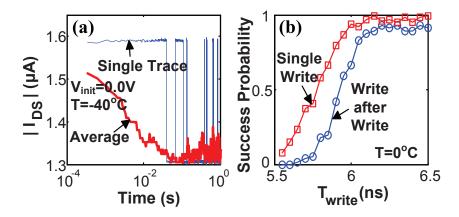

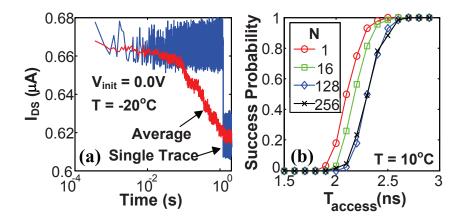

| 3.15 | (a) Single trace and average response of a trap to large-bias change $(V_{init} =$                                               |    |

|      | $1.0V, V_{measure} = 0.7V)$ (b) Large-bias response of trap at different temperatures.                                           | 37 |

| 3.16 | (a) Single trace and average response of a trap to large-bias change $(V_{init} =$                                               |    |

|      | $0.0V$ , $V_{measure} = 0.7V$ ) (b) Large-bias response of trap at different temperatures.                                       | 37 |

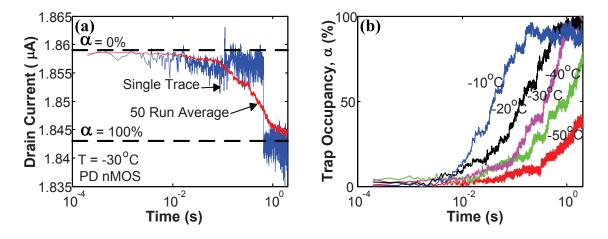

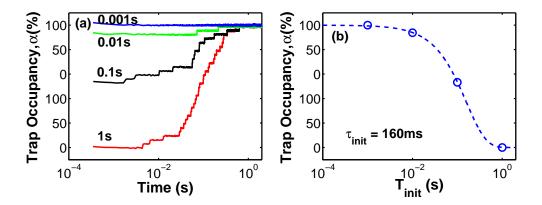

| 3.17 | (a) Average response of a trap to large-bias change with different values of                                                     |    |

|      | $T_{init}$ ( $V_{init} = 0.0 \text{V}$ , $V_{measure} = 0.7 \text{V}$ ) (b) Estimated average response of the                    |    |

|      | trap to large-bias change with $V_{init} = 0.7 \text{V}$ and $V_{measure} = 0.0 \text{V}$                                        | 38 |

| 3.18 | (a) Single trace and average response of a type-II trap to large-bias change                                                     |    |

|      | $(V_{init} = 1.0 \text{V}, V_{measure} = 0.7 \text{V}) \text{ (b) } (V_{init} = 0.0 \text{V}, V_{measure} = 0.7 \text{V}) \dots$ | 36 |

| 3.19 | Measured drain current of SRAM $PU$ PMOS transistor demonstrating RTS                                                            |    |

|      | with long time constant                                                                                                          | 40 |

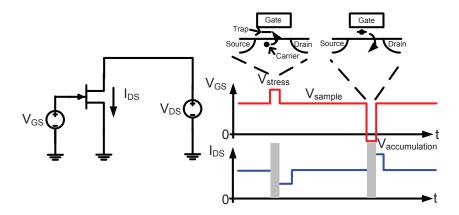

| 3.20 | Waveforms of the alternating-bias technique                                                                                      | 40 |

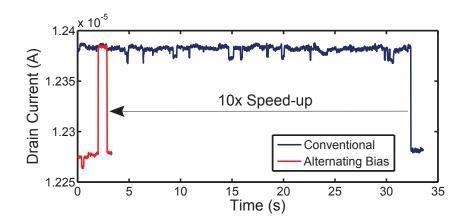

| 3.21 | Drain current of the same transistor measured using conventional and                                                             |    |

|      | alternating-bias techniques                                                                                                      | 41 |

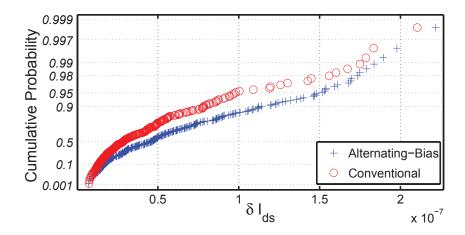

| 3.22 | Gumbel plots of RTS drain current fluctuations measured using conventional                                                       |    |

|      | and alternating-bias techniques with constant time                                                                               | 42 |

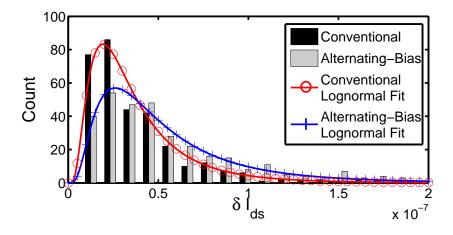

| 3.23 | Histogram and lognormal distribution fits of RTS $I_{ds}$ fluctuations measured                                                  |    |

|      | using conventional and alternating-bias techniques with constant time                                                            | 42 |

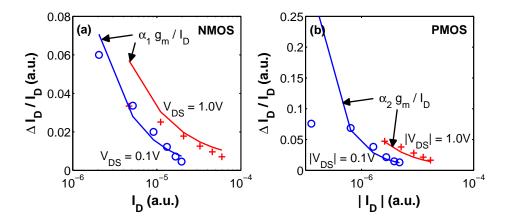

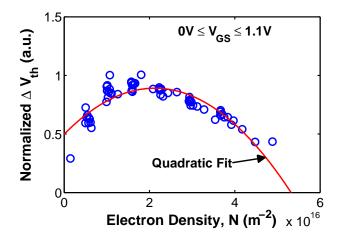

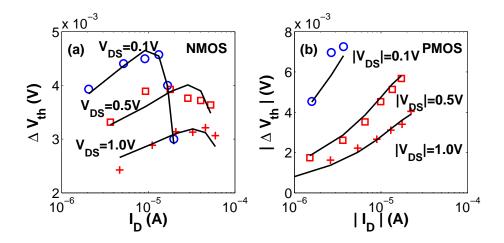

| 3.24 | Bias dependence of RTS amplitude extracted from 45 nm SRAM (a) NMOS                                                              |    |

|      | and (b) PMOS transistors. Solid lines correspond to number fluctuation model                                                     |    |

|      | fitted to data at $V_{DS} = 0.1$ V                                                                                               | 44 |

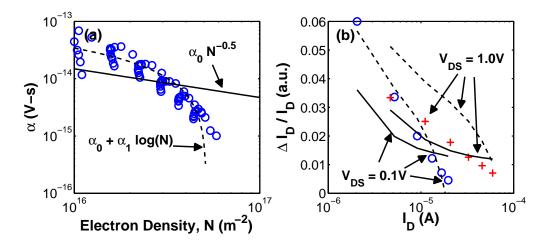

| 3.25 | 45 nm NMOS RTS amplitude fitted to correlated model. (a) Extracted                                                               |    |

|      | scattering co-efficients as a function of electron density and fitted models.                                                    |    |

|      | (b) Measured RTS amplitude across different biases and fitted models. Solid                                                      |    |

|      | lines and dashed lines correspond to $1/\sqrt{N}$ and $log(N)$ models for scattering                                             |    |

|      | co-efficient, respectively.                                                                                                      | 46 |

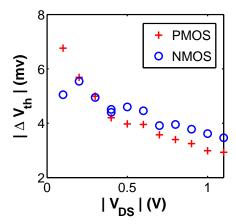

| 3.26 | $V_{DS}$ dependence of $\Delta V_{th}$ for a trap measured from PMOS and NMOS                                                    |    |

|      | transistors at constant gate bias ( $ V_{GS}  = 0.8 \text{ V}$ )                                                                 | 47 |

| 3.27 | Residual $\Delta V_{th}$ after normalization by linear fit of $V_{DS}$ dependence, as a                                          |    |

|      | function of electron density                                                                                                     | 47 |

| 3.28 | Equivalent $\Delta V_{th}$ fluctuation due to RTS across gate and drain biases extracted                                         |    |

|      | from (a) NMOS and (b) PMOS SRAM transistors. Solid lines represent the                                                           |    |

|      | empirical model fitted to the data                                                                                               | 49 |

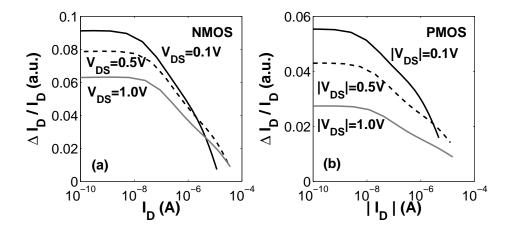

| 3.29         | RTS amplitude for (a) NMOS and (b) PMOS transistors estimate using SPICE models extended with empirical RTS amplitude model                      | 49  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3 30         | Gumbel plots of normalized RTS fluctuations in drain currents, measured from                                                                     | 48  |

| J.JU         | transistors in the padded-out SRAM cells                                                                                                         | 50  |

| 2 21         | •                                                                                                                                                | 50  |

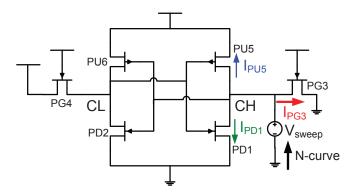

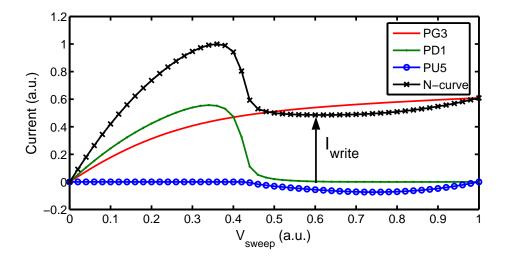

| 3.31         | Schematic of $I_{write}$ measurement. The N-curve is the sum of the currents                                                                     | E ( |

| 2 20         | flowing out of the internal node                                                                                                                 | 52  |

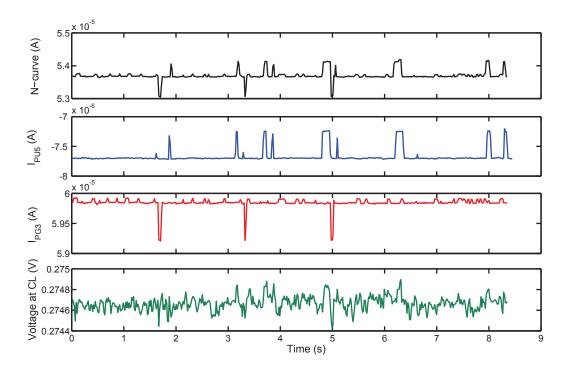

|              | Currents contributing to $I_{write}$                                                                                                             | 52  |

| <b>ა.</b> აა | Currents and voltages measured from padded-out SRAM cell with RTS. RTS characteristics of the N-curve are influenced by RTS in both PU5 and PG3. |     |

|              | Voltage fluctuation at node CL is minimal due to the low impedance of this                                                                       |     |

|              | node                                                                                                                                             | 53  |

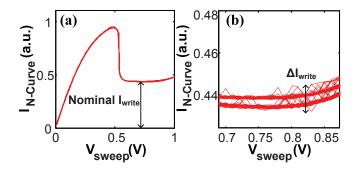

| 3.34         | N-curves measured from multiple sweeps demonstrating the technique for                                                                           |     |

|              | extracting (a) nominal $I_{write}$ and (b) RTS fluctuation in $I_{write}$ due to RTS                                                             | 54  |

| 3.35         | (a) Histogram of nominal $I_{write}$ . (b) Gumbel plots of $I_{write}$ RTS fluctuation.                                                          |     |

|              | The Maximum RTS amplitude normalized to $\sigma I_{write}$ at each operating voltage                                                             |     |

|              | does not change significantly, although the shape of the distribution changes.                                                                   | 54  |

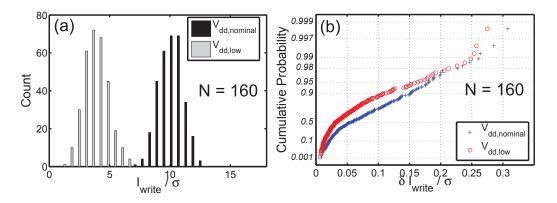

| 3.36         | (a) Quantile-quantile plot of $I_{write}$ with normal distribution fit. (b) Quantile-                                                            |     |

|              | quantile plot of RTS fluctuation in $I_{write}$ with hybrid distribution fit                                                                     | 55  |

| 3.37         | Scatter plots of measured nominal $I_{write}$ and RTS fluctuation at nominal and                                                                 |     |

|              | low operating voltages                                                                                                                           | 55  |

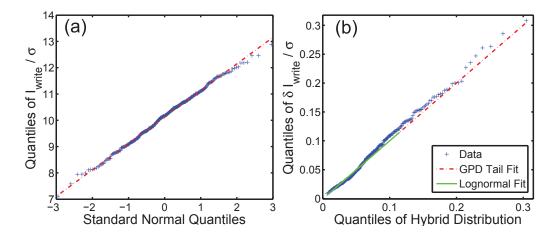

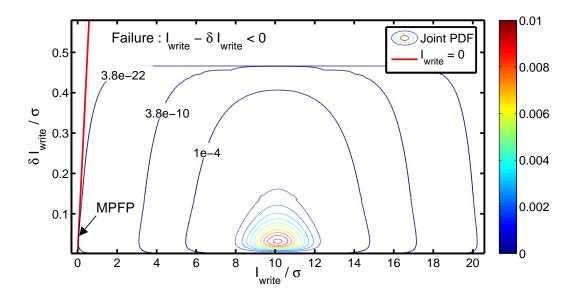

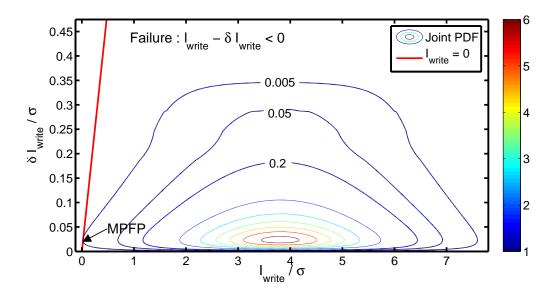

| 3.38         | Joint probability density function of nominal $I_{write}$ and RTS fluctuation at                                                                 |     |

|              | nominal $V_{dd}$                                                                                                                                 | 56  |

| 3.39         | Joint probability density function of nominal $I_{write}$ and RTS fluctuation at                                                                 |     |

|              | low $V_{dd}$                                                                                                                                     | 56  |

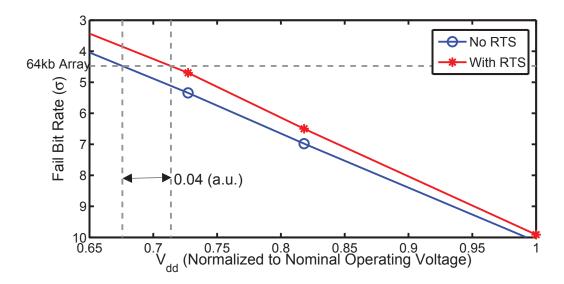

|              | FBR of SRAM at different voltages                                                                                                                | 58  |

| 3.41         | Measured fail bit count of a 64kb SRAM array                                                                                                     | 58  |

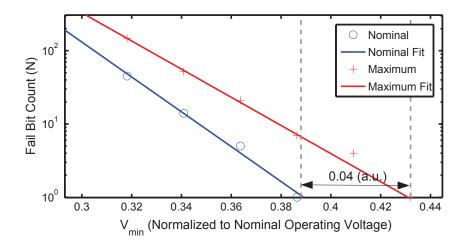

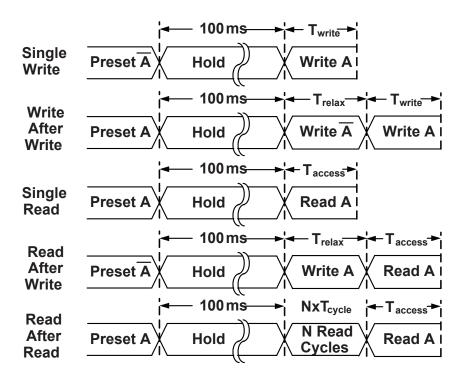

| 3.42         | ( ) 0 1                                                                                                                                          |     |

|              | (b) Zoomed-in view of region defining static SRAM write margin                                                                                   | 59  |

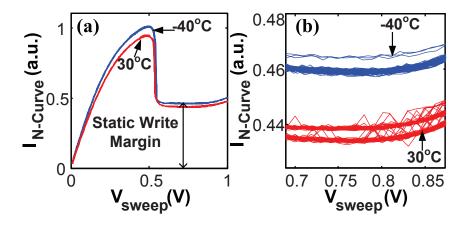

| 3.43         | SRAM access patterns for evaluating the impact of RTS on dynamic read and                                                                        |     |

|              | write ability.                                                                                                                                   | 60  |

| 3.44         | (a) SRAM schematic for read access with internal node $CL$ storing a "0". (b)                                                                    |     |

|              | SRAM schematic for writing a "0" into node $CH$                                                                                                  | 60  |

| 3.45         | (a) Large-bias change response occupancy of a trap in $PD1$ . (b) Statistical                                                                    |     |

|              | distributions of $T_{access}$ for single-read and read-after-write                                                                               | 61  |

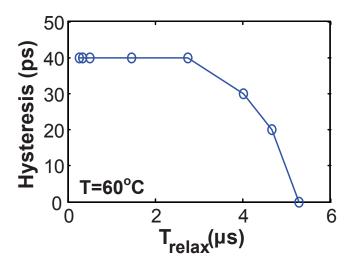

|              | Dependence of $T_{access}$ fluctuation on delay since last write access $(T_{relax})$                                                            | 62  |

| 3.47         | (a) Large-bias change occupancy of a type-II trap in $PD1$ . (b) Statistical                                                                     |     |

|              | distributions of $T_{access}$ for single-read and read-after-write                                                                               | 62  |

| 3.48         | (a) Large-bias change occupancy of a trap in $PU2$ . (b) Statistical distributions                                                               |     |

|              | of $T_{write}$ for single-write and write-after-write                                                                                            | 63  |

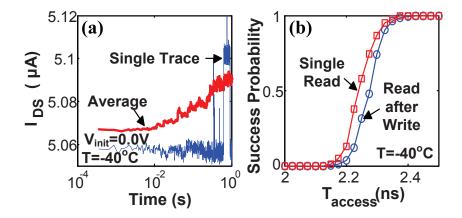

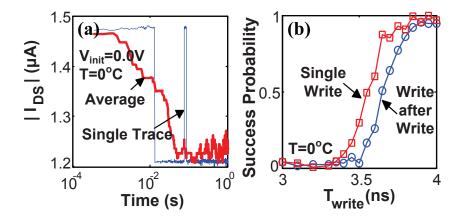

| 3.49         |                                                                                                                                                  |     |

|              | distributions of Tames, for single-write and write-after-write                                                                                   | 63  |

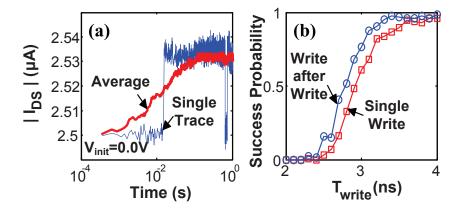

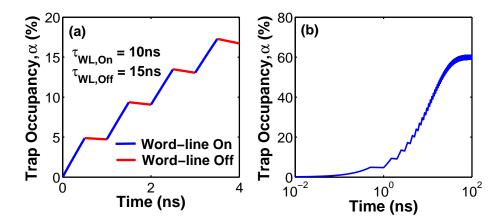

| 3.50  | (a) Large-bias change occupancy of a trap in $PU1$ . (b) Statistical distributions of $T_{write}$ for single-write and write-after-write                                                             |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

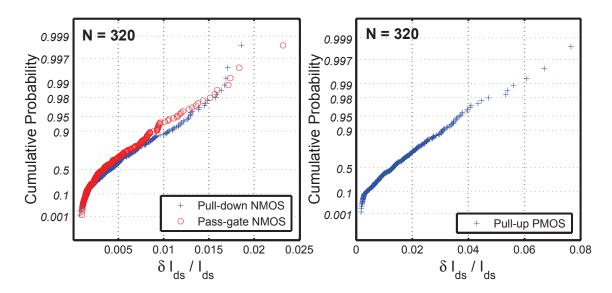

| 3.51  |                                                                                                                                                                                                      |

| 0.01  | Zoomed-in view (b) Expanded view                                                                                                                                                                     |

| 3.52  | (a) Large-bias change occupancy of a trap in $PG1$ . (b) Statistical distributions of $T_{access}$ with $N$ read-after-read cycles, saturting at $N=128$ 6                                           |

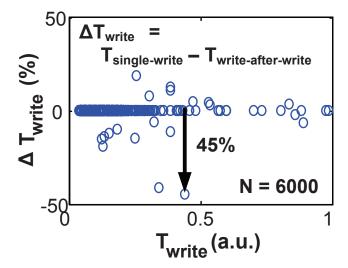

| 3.53  | 1 400000                                                                                                                                                                                             |

|       | Scatter plot of $\Delta T_{write}$ due to RTS vs. nominal $T_{write}$ 6                                                                                                                              |

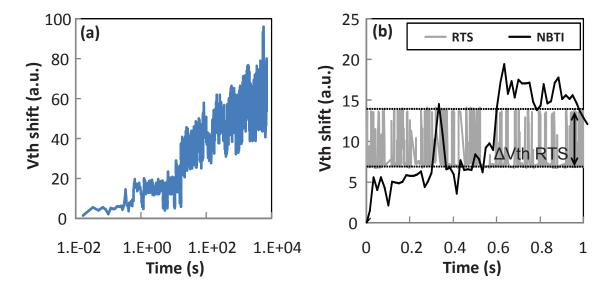

| 3.55  | (a) Measured $V_{th}$ degradation due to NBTI. (b) RTS observed in the same transistor at 25°C super-imposed on top of $V_{th}$ degradation observed during NBTI characterization at $125^{\circ}$ C |

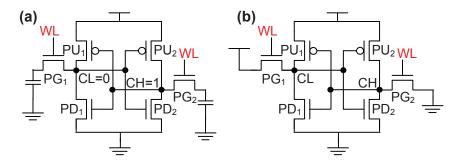

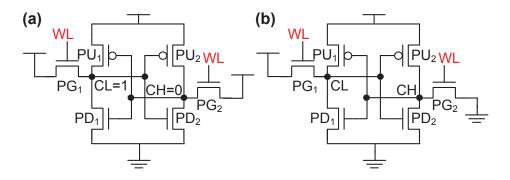

| 4.1   | Schematics of SRAM for: (a) Read static noise margin analysis. (b) Write static noise margin analysis                                                                                                |

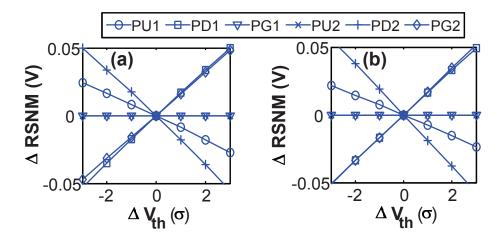

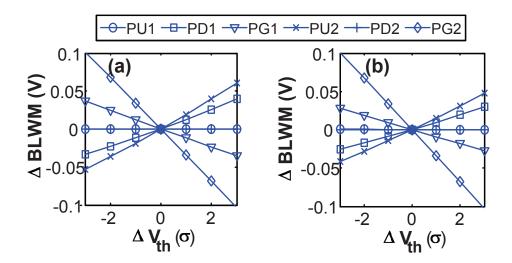

| 4.2   | Sensitivity of read static noise margin (RSNM) to $V_{th}$ variability centered at:<br>(a) $\mathbf{x} = 0$ . (b) $\mathbf{x} = MPFP$                                                                |

| 4.3   | Sensitivity of bit-line write margin (BLWM) to $V_{th}$ variability centered at: (a) $\mathbf{x} = 0$ . (b) $\mathbf{x} = MPFP$                                                                      |

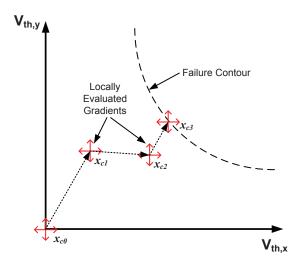

| 4.4   | MPFP search with locally evaluated gradients                                                                                                                                                         |

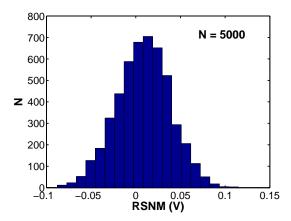

| 4.5   | RSNM histogram of 5000 samples generated from original Gaussian distributions shifted by the MPFP vector                                                                                             |

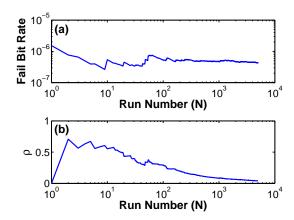

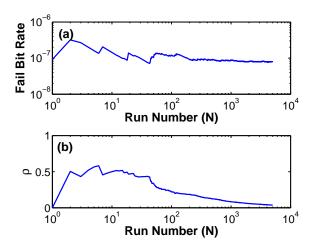

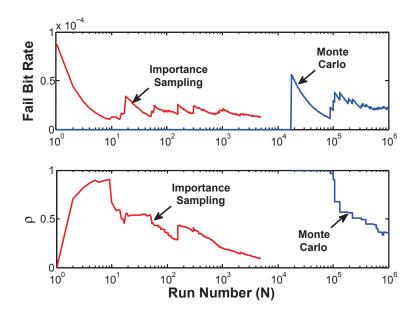

| 4.6   | Evolution of (a) fail bit rate $(\hat{p}_{IS})$ and (b) convergence metric $(\rho)$ as a function of run number                                                                                      |

| 4.7   | General algorithm for estimating statistical dynamic read stability reliability of SRAM                                                                                                              |

| 4.8   | Sensitivity of dynamic read stability $(T_{read})$ to $V_{th}$ variability                                                                                                                           |

| 4.9   | Evolution of (a) fail bit rate $(\hat{p}_{IS})$ and (b) convergence metric $(\rho)$ as a function of run number, corresponding to $T_{read}$ importance sampling                                     |

| 4.10  | General algorithm for estimating statistical dynamic writeability reliability of SRAM                                                                                                                |

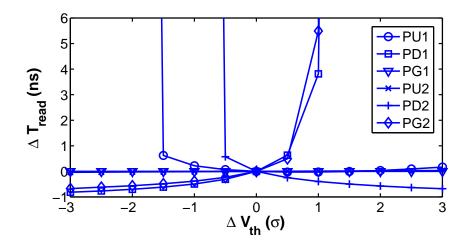

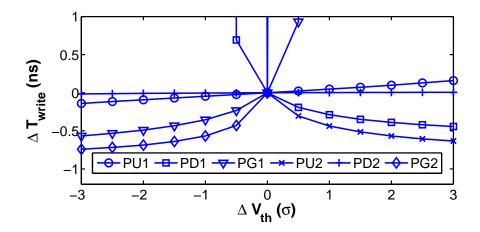

| 4.11  | Sensitivity of dynamic writeability $(T_{write})$ to $V_{th}$ variability                                                                                                                            |

| 4.12  | Evolution of (a) fail bit rate $(\hat{p}_{IS})$ and (b) convergence metric $(\rho)$ as a function                                                                                                    |

|       | of run number, corresponding to $T_{write}$ importance sampling                                                                                                                                      |

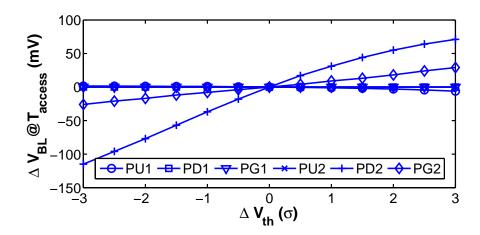

|       | Sensitivity of final bit-line voltage at $T_{access}$ to $V_{th}$ variability                                                                                                                        |

| 4.14  | Evolution of (a) fail bit rate $(\hat{p}_{IS})$ and (b) convergence metric $(\rho)$ as a function                                                                                                    |

|       | of run number, corresponding to dynamic read access importance sampling 8                                                                                                                            |

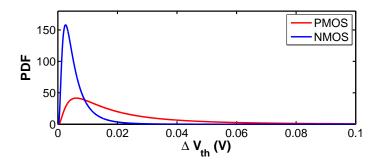

| 4.15  | Simulated lognormal distributions of $V_{th}$ fluctuation due to RTS in NMOS                                                                                                                         |

| 1 1 6 | and PMOS transistors                                                                                                                                                                                 |

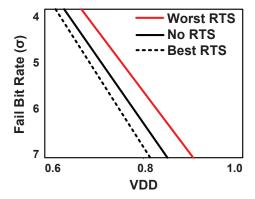

| 4.16  | Conceptual plot demonstrating shift in dependencies between cell sigma and                                                                                                                           |

|       | $V_{DD}$ with worst-case RTS combination, best-case RTS combination, and no                                                                                                                          |

|       | RTS                                                                                                                                                                                                  |

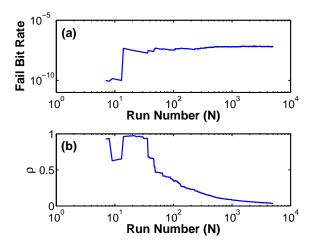

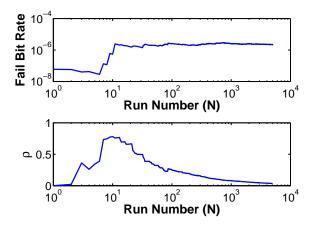

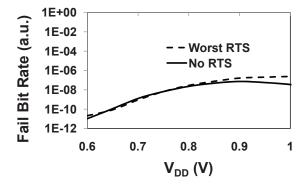

|            | Evolution of (a) fail bit rate $(p_{IS})$ and (b) convergence metric $(\rho)$ as a function of run number, corresponding to $T_{read}$ with lognormal RTS distributions evaluated using importance sampling and conventional Monte Carlo simulations. Fail bit rate corresponding to $T_{read}$ as a function of $V_{DD}$ without RTS and with worst-case RTS. $T_{read} = 1$ ns | 90  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

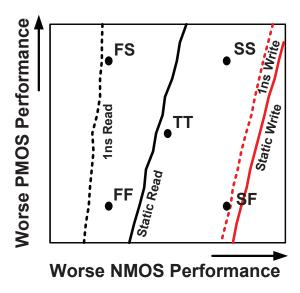

| 5.1        | NMOS and PMOS global process variation space annotated with failure contours for read and write operation, as well as process corners [86]                                                                                                                                                                                                                                       | 93  |

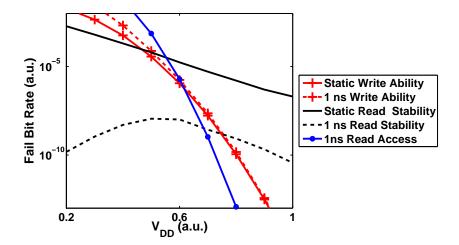

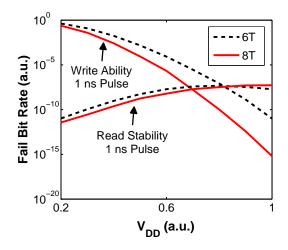

| 5.2        | Dependence of fail bit rate on $V_{DD}$ for static and dynamic writeability, read stability, and dynamic read access                                                                                                                                                                                                                                                             | 95  |

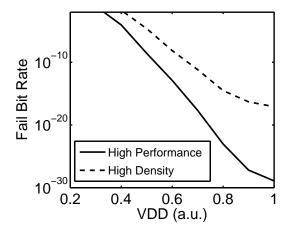

| 5.3        | Fail bit rate as a function of $V_{DD}$ for a high performance and high density bitcell from a particular process technology. The flattening of fail bit rate at higher $V_{DD}$ is due to the weaker sensitivity of dynamic read stability to $V_{DD}$                                                                                                                          | 0.6 |

| _ ,        | compared to other failure modes                                                                                                                                                                                                                                                                                                                                                  | 96  |

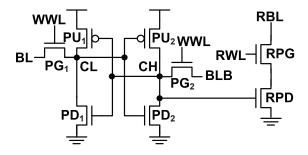

| 5.4        | Schematic of 8T SRAM bitcell.                                                                                                                                                                                                                                                                                                                                                    | 98  |

| 5.5        | Fail bit rate of 8T and 6T bitcells as a function of $V_{DD}$                                                                                                                                                                                                                                                                                                                    | 98  |

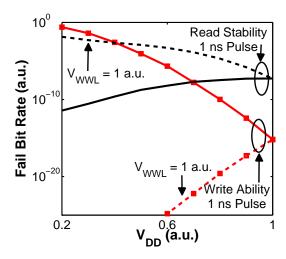

| 5.6        | Dynamic stability of 8T bitcell with and without $V_{WWL}$ boost                                                                                                                                                                                                                                                                                                                 | 96  |

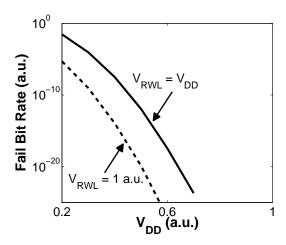

| 5.7        | Dynamic access (1 ns pulse) fail bit rate of 8T bitcell with and without $V_{RWL}$                                                                                                                                                                                                                                                                                               | 100 |

| <b>F</b> 0 | boost.                                                                                                                                                                                                                                                                                                                                                                           | 100 |

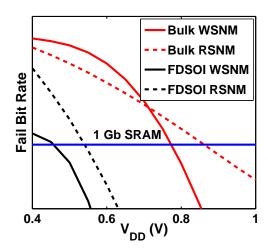

| 5.8        | Comparison of fail bit rate for a similar SRAM bitcell implemented either in                                                                                                                                                                                                                                                                                                     | 101 |

| 5.9        | bulk CMOS or FDSOI, demonstrating more than 200 mV reduction in $V_{min}$ Impact of word-line voltage offset on SRAM stability across different process                                                                                                                                                                                                                          | 101 |

|            | corners.                                                                                                                                                                                                                                                                                                                                                                         | 102 |

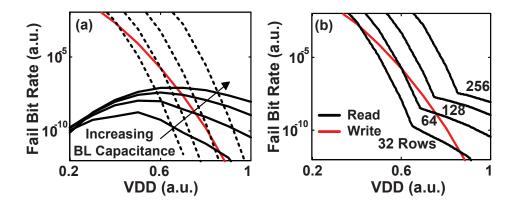

| 5.10       | (a) Fail bit rate degradation with increasing bit-line capacitance. (b) Fail bit rate degradation as a function of the number of rows in a bit-line with worst-case fail bit rate for dynamic read access and dynamic read stability combined                                                                                                                                    |     |

|            | into a single curve.                                                                                                                                                                                                                                                                                                                                                             | 104 |

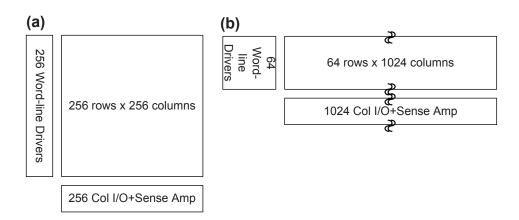

| 5.11       | 64 kb SRAM array segmented into (a) 256 rows x 256 columns, and (b) 64                                                                                                                                                                                                                                                                                                           |     |

|            | rows x 1024 columns                                                                                                                                                                                                                                                                                                                                                              | 105 |

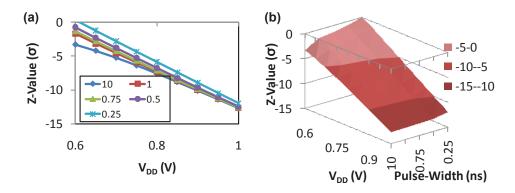

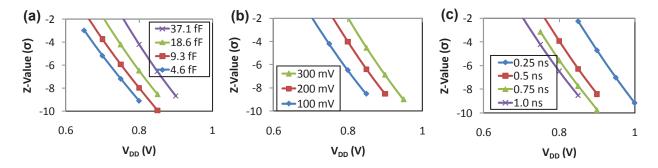

| 5.12       | (a) Dependence of SRAM reliability (Z-value) corresponding to dynamic                                                                                                                                                                                                                                                                                                            |     |

|            | writeability as a function of $V_{DD}$ across different access pulse-widths (ns),                                                                                                                                                                                                                                                                                                |     |

|            | and (b) contour plot of SRAM reliability corresponding to dynamic writeability.                                                                                                                                                                                                                                                                                                  | 106 |

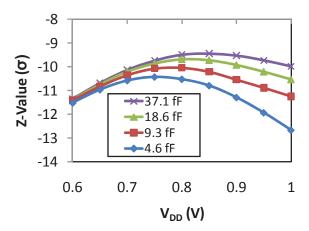

| 5.13       | SRAM reliability corresponding to dynamic read stability as a function of $V_{DD}$                                                                                                                                                                                                                                                                                               |     |

|            | across different bit-line capacitance (1 ns pulse-width)                                                                                                                                                                                                                                                                                                                         | 107 |

| 5.14       | (a) Dependence of SRAM reliability (Z-value) corresponding to dynamic read                                                                                                                                                                                                                                                                                                       |     |

|            | access as a function of $V_{DD}$ across different (a) bit-line capacitance, (b) sense-                                                                                                                                                                                                                                                                                           |     |

|            | amplifier offset voltages, and (c) access pulse-widths                                                                                                                                                                                                                                                                                                                           | 107 |

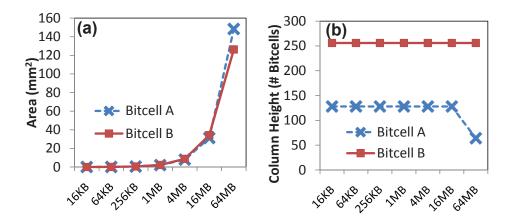

| 5.15       |                                                                                                                                                                                                                                                                                                                                                                                  |     |

| -          | two different bitcells, (b) column height corresponding to the minimum-area                                                                                                                                                                                                                                                                                                      |     |

|            | solution for each cache size                                                                                                                                                                                                                                                                                                                                                     | 109 |

|            |                                                                                                                                                                                                                                                                                                                                                                                  |     |

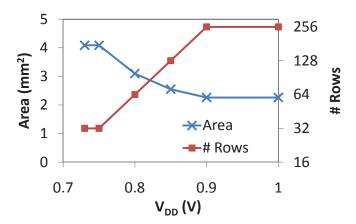

| 5.16 | Optimum area of a 1MB cache memory optimized at different operating           |     |

|------|-------------------------------------------------------------------------------|-----|

|      | $V_{DD}$ conditions. The corresponding optimum column height (# rows) is also |     |

|      | plotted on the same graph                                                     | 110 |

# List of Tables

| 1.1 | Sensitivity analysis of writeability to the respective transistor $V_{th}$ variation.                   | 10 |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 4.1 | Progress of MPFP search algorithm applied to RSNM                                                       | 75 |

| 4.2 | Progress of feasible $T_{read}$ search algorithm. $T_{read,target} = 1 \text{ ns } \dots \dots$         | 79 |

| 4.3 | Progress of $T_{read}$ MPFP search algorithm. $T_{read,target} = 1 \text{ ns} \dots \dots \dots$        | 80 |

| 4.4 | Progress of $T_{write}$ MPFP search algorithm. $T_{write,target} = 1 \text{ ns} \dots \dots$            | 82 |

| 4.5 | Progress of $T_{access}$ MPFP search algorithm. $\Delta V_{BL,target} = 0.1 \text{ V} \dots \dots$      | 84 |

| 4.6 | Progress of $T_{read}$ MPFP search algorithm with lognormal RTS distributions                           |    |

|     | in $PU1$ and $PU2$ . $T_{read,target} = 1.0 \text{ ns} \dots \dots \dots \dots \dots \dots \dots \dots$ | 89 |

#### Acknowledgments

First and foremost, I would like thank my advisor, Professor Borivoje Nikolić for guiding me on the various technical aspects related to this dissertation. It was from his insight into pressing issues impacting the scalability of SRAM, that this thesis was born, and it was due to his comprehensive knowledge of various disciplines that this work was finally completed. I am in great appreciation of his patience in working with me over countless iterations of drafts and presentations to ensure impeccable delivery of the technical content. I would also like to thank him for other kind words of advice related to life, family, and my career.

I would also like to acknowledge Professor Tsu-Jae King Liu who served as chair of my qualifying exam committee and participated as a member of my dissertation committee. She also played an active role as a co-advisor on various research projects. I would also like to thank her students, Dr. Changhwan Shin, Nattapol Damrongplasit, and Min Hee Cho for their help in testchip tapeout and many discussions on device physics.

I am also grateful to Professor Paul Wright for participating as a member of my qualifying exam committee and dissertation committee and helping me place my research within the context of interest to society. I am also thankful to Professors Andy Neureuther and Costas Spanos for their feedback provided during countless variability group meetings. I would also like to thank one of Professor Neureuther's students, Dr. Lynn Wang, for her collaboration on interpreting variability results within the context of lithography. I am also indebted to Professor Martin Wainwright who provided advice on importance sampling and optimization. I would also like to thank Professor Jan Rabaey for being a member of my dissertation committee and his valuable advice earlier on in my Ph. D. career.

My research has been supported by the Center for Circuit & System Solutions (C2S2) Focus Center. The final year of my research was particularly made possible through IBM's generous Ph. D. fellowship. Chip fabrication was donated by STMicroelectronics.

I am appreciative of the help and support from the staff at the EECS graduate office and the Berkeley Wireless Research Center (BWRC). In particular, Ruth Gjerde, Tom Boot, Brenda Farrell, Pierce Chua, and Olivia Nolan for their administrative support; Kevin Zimmerman and Brian Richards for maintaining a top notch computing environment equipped with up-to-date tools and design kits; Susan Mellers and Chang Chun for maintaining the BWRC lab and co-ordinating availability of lab equipment; and Gary Kelson for directing the BWRC. I would also like to acknowledge various students of the department - Dr. Zheng Guo, Dr. Liang-Teck Pang, and Dr. Andrew Carlson for passing down to me a rich set of circuits, scripts, and techniques for variability characterization and overseeing my research; Dr. Bastien Giraud for his help on testchip debugging; Lauren Jones and Jason Tsai for their help on a testchip tapeout; Patrick Bennett for de-processing the testchips for failure analysis; Sriramkumar Venugopalan for helping me on RTS noise amplitude modeling; Katerina Papadopoulou and Brian Zimmer for their assistance on FDSOI testchip tapeouts; and Andrew Mairena for performing measurements.

This thesis would not have been possible and would lack relevance to the industry if not

for the mentorship of a few industrial domain experts. I do not have enough words to thank Dr. Yasumasa Tsukamoto for bringing me up to speed on state of the art SRAM statistical analysis, introducing me to new sources of SRAM variability, as well as being a friend. I would also like to thank Dr. Stephen Kosonocky, Dr. Olivier Thomas, and Dr. Sani Nassiff for providing constant feedback on my research.

Finally, I would like to thank my wife and son - Jessica and Ethan Toh - for standing by me and graciously giving me time to complete this work. I am also grateful to my parents - Professor Seong Chong Toh and How Chan Wong - for supporting me through this long journey.

# Chapter 1

# Static and Dynamic SRAM Stability

#### 1.1 Introduction

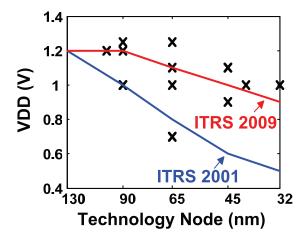

SRAM scaling has been identified as one of the bottlenecks for supply voltage  $(V_{DD})$  reduction in current and future technology nodes. Minimum SRAM operating voltage  $(V_{MIN})$  is a function of the magnitude of process-induced variability as well as the array size. Aggressive SRAM bitcell scaling, coupled with continued increase in SRAM array sizes, has resulted in stagnation in SRAM  $V_{DD}$  scaling. This trend is observed in reported values of SRAM array  $V_{DD}$  and is recognized in the latest edition of the International Technology Roadmap for Semiconductors (ITRS) (Figure 1.1) [30].  $V_{MIN}$  is traditionally estimated using various static noise margins (SNM) [82, 61]. These metrics are known to be optimistic in writeability and pessimistic in read stability primarily due to the fact that SRAM access is a dynamic operation and occurs within a finite duration versus the main assumption of infinite access time in static noise margins [87]. Dynamic stability metrics, derived from the SRAM under dynamic access, have been proposed to provide a better estimate of SRAM  $V_{MIN}$  [32, 37, 62]. While these metrics have been studied extensively through simulations, results based on large-scale silicon characterization of both read and write stability have only been reported in this dissertation. Similarly, a quantitative relationship between the static and dynamic read and write margins is studied here. The sensitivity of dynamic stability to non-idealities such as random telegraph signaling (RTS) noise and aging is also studied in this work.

This chapter first reviews conventional static and dynamic 6 transistor SRAM metrics as well as their expected correlations. Monte-Carlo simulations, introducing Gaussian distributions of  $V_{th}$  to the 6 SRAM transistors, are presented in this section to illustrate expected correlations between the metrics.

Figure 1.1: SRAM array VDD reported in ISSCC and VLSI (2004-2010) and ITRS predictions.

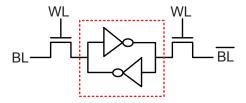

Figure 1.2: Schematic of an SRAM bitcell.

### 1.2 Background

Memory represents one of the fundamental building blocks of any computation system as it is required to retrieve variables for the computation as well as to store results of the calculation. Memory can be divided into two classes: volatile and non-volatile. Volatile memory loses the stored information when the power supply is removed while non-volatile memory typically retains the data for a few years. Static Random Access Memory (SRAM), which is the main subject of this work, is classified as volatile memory because it relies on a power supply to statically retain data. It is further classified as a random access memory because it allows access to arbitrary locations of data without any restrictions.

Each bit of data within an SRAM is stored in SRAM bitcells. Figure 1.2 illustrates a schematic representation of a bitcell circuit. The core of the SRAM bitcell (enclosed by dotted lines) consists of cross-coupled inverting gain elements and is used to store the state of the bitcell. Assuming that one node in the core is storing an electrical representation of a logic-0. This node drives the input of an inverting gain element to logic-1 which then causes the next inverting gain element to drive the original node back to a logic-0. This

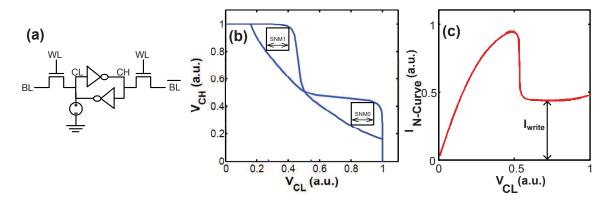

Figure 1.3: (a) Schematic of bitcell for SRAM margin measurement. (b) Static noise margin (SNM) extraction. (c) Write margin ( $I_{write}$ ) extraction.

positive feedback configuration increases robustness of the circuit to noise. The bitcell core is accessed using a pair of access transistors that are used to read the contents of the bitcell or to write new values. These transistors connect the core of the bitcell to a pair of bitlines  $(BL \text{ and } \overline{BL})$  and are enabled by pulsing on the word-line signal (WL). These access transistors are designed to be strong enough to overcome the positive feedback in the bitcell core and overwrite the contents of the bitcell. On the other hand, they also need to be weak enough that the content of the bitcell is not accidentally disturbed during a read operation. Herein lies one of the fundamental constraints in SRAM bitcell design - the tradeoff between read and write margin. The cross-coupled inverting gain elements in the core are usually implemented as two static CMOS inverters with each static CMOS inverter consisting of a PMOS and NMOS transistor. This SRAM bitcell design is usually called a 6T bitcell due to the fact that there are 6 transistors in a bitcell.

#### 1.2.1 SRAM Margins

SRAM margins are used to quantify the robustness of a read and write operation. 1.3 (a) illustrates the schematic of a bitcell set up for SRAM static margin extraction. A voltage source is connected to one of the internal nodes (CL). This node voltage is swept while measuring voltages at other nodes or the current flowing out of this voltage source  $(I_{N-Curve})$ . Figure 1.3 (b) plots the technique for characterizing the static noise margin (SNM) of a bitcell [61]. Both bit-lines and the word-line  $(BL, \overline{BL}, WL)$  are connected to  $V_{DD}$ . The first curve is measured by sweeping the voltage of node CL while monitoring the voltage at node CH. This essentially traces the switching characteristic of one of the cross-coupled inverters. The other curve is measured by sweeping node CH while monitoring the voltage at node CL. The static noise margin for storing a 0 or 1 (SNM0) and (SNM1) corresponds to the side of the largest square that fits into the respective lobes. This static

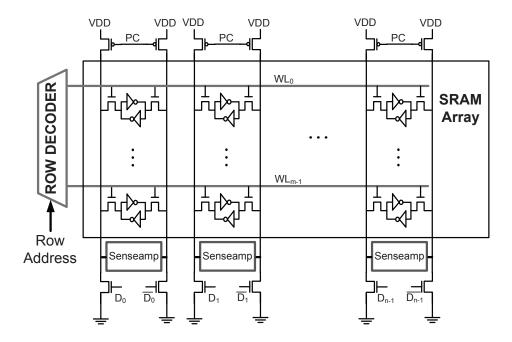

Figure 1.4: Schematic of an  $m \times n$  SRAM array.

margin essentially characterizes the largest voltage perturbation that can be sustained in the internal nodes of the bitcell before the bitcell looses the ability to store two states. The bias conditions applied on the bitcell for write margin characterization depend on the data that is being written into the bitcell. To write a logic-0 into node CL, node BL is grounded while nodes  $\overline{BL}$  and WL are connected to  $V_{DD}$ . The voltage at node CL is then swept from  $V_{DD}$  to ground while the current flowing through the voltage source  $(I_{N-Curve})$  is monitored. This emulates the bias conditions applied to the transistors as a logic-0 is written to node CL.  $I_{N-Curve}$  observed during this voltage sweep is plotted on Figure 1.3 (c). The static write margin  $(I_{write})$  is defined as the minimum current observed at the right side of the plot [13]. The  $I_{write}$  write margin is preferred over an alternative write noise margin proposed by Seevinck  $et\ al$  because of easier extraction from experimental results and better correlation with SRAM write  $V_{min}$  across a wide range of voltages [24].

#### 1.2.2 SRAM Array

Figure 1.4 illustrates an array of SRAM bitcells representing an organization typically encountered in SRAM array implementations. The bitcells are organized into m rows and n columns. Additional circuits are located at the periphery of the array. This peripheral circuitry is used to support random read and write access to the data stored in the SRAM bitcells. All bitcells in a column share a common pair of bit-lines and column peripheral circuitry while all bitcells in a row share a common word-line, driven by the row decoder.

The pre-charge headers at the top of the array are used to pre-charge the bit-lines up to  $V_{DD}$  prior to a read or write operation. During a read operation, the row decoder enables one of the word-lines, depending on the row address that is selected. The enabled word-line turns on the access transistors which connects the bitcell core to the bit-lines and transfers the contents of the bitcell onto the bit-lines. A sense-amplifier is then used to read the values stored on the bit-lines and sent to the output of the array. During a write operation, one of the bit-lines in a pair is selectively dis-charged using the transistors at the bottom of the array, depending on the new data that is to be written into the bitcells. The word-line corresponding to the desired row where new data is to be stored is then enabled. This transfers the state of the bit-lines into the core of the bitcells.

The amount of capacitance on the bit-lines plays a critical role in SRAM performance and stability. The bit-line capacitance is dominated mainly by diffusion capacitance of all the access transistors sharing the same bit-line. Coupling capacitance of the bit-line to neighboring wires also plays a role. From an array efficiency perspective, it is highly desirable to have long bit-lines tied to many bitcells, sharing a single sense-amplifier. This however results in large bit-line capacitance which reduces SRAM read performance due to the extra time required to discharge the higher capacitance. Energy efficiency of the array is also degraded as this large capacitance needs to be charged and dis-charged frequently. More recently, hierarchical bit-lines have been introduced to minimize bit-line capacitance. These array organization involves segmenting the bit-lines into many local bit-lines with a small number of bitcells sharing the bit-line and logically combining the results from all the bit-lines. Although this requires more area overhead, this scheme could potentially allow the use of smaller less robust bitcells with weaker read current, ultimately resulting in a smaller SRAM array with lower energy consumption.

#### 1.3 Read Access Metrics

#### 1.3.1 Static Read Current $(I_{read})$

Static read current ( $I_{read}$ ) corresponds to the current that is being sourced from the bit-line into the SRAM node storing a 0. Under SRAM read operation, this current is responsible for discharging the pre-charged bit-line capacitances ( $C_{BL}$ ) enough to overcome the offset voltage ( $V_{offset}$ ) of the sense-amplifier to result in a correct value being latched. It is expected to correlate with actual read access time ( $T_{access}$ ) according to Equation 1.1

$$T_{access} \propto \frac{C_{BL} \times V_{offset}}{I_{read}}$$

(1.1)

Actual read access time might deviate from this linear relationship due to leakage currents from inactive bitcells sharing the bit-line as well as the fact that  $C_{BL}$  is a distributed RC network spanning the entire column of the SRAM array. Degradation in  $I_{read}$  and read access

Figure 1.5: (a) Schematic of a 6-T SRAM cell storing a 0 on the left internal node. (b) Simulated waveforms corresponding to failed read access with pulse-width,  $T_A$ . Output of the sense-amplifier (Data) resolves to the incorrect value. (c) Simulated waveforms corresponding to successful read access with a longer pulse-width,  $T_B$ . Output of the sense-amplifier (Data) resolves to the correct value.

time due to RTS also contributes to this discrepancy, as will be shown in Section 3.5.

#### 1.3.2 Read Access Time $(T_{access})$

Figure 1.5 illustrates an SRAM bitcell undergoing read access with pulse-widths  $T_A$  and  $T_B$ . Pulse-width  $T_A$  is too short to sufficiently discharge the bit-line capacitance to overcome offset in the sense-amplifier. There exists a pulse-width,  $T_{access}$  ( $T_A < T_{access} < T_B$ ), where the sense-amplifier is on the threshold of a successful read access that is defined as the read access time. This is similar to the dynamic access failure criteria defined in [37]. This definition of read access time isolates out variability in the read access operation due to variability of the SRAM bitcell and ignores other delays such as word-line driver delay and sense-amplifier delay.

#### 1.4 Read Stability Metrics

#### 1.4.1 Static Read Stability Margins

Conventional stability metrics, such as SNM and N-curves [82, 61], require sweeping internal nodes in order to obtain the voltage transfer curves, which is not practical for evaluating large arrays. Supply read retention voltage (SRRV), which does not require access to the internal nodes, is used in this chapter to characterize static read stability [24]. This metric characterizes read stability margins by decreasing the supply voltage of the bitcell core while monitoring the currents flowing through the bit-lines which are held at  $V_{DD}$ . A flip in data stored by the bitcell is correlated to a sharp change in the bitcell currents. The SRRV margin is defined as the additional bitcell core voltage reduction that can be tolerated before the

bitcell loses the data. A direct correlation between this and other stability metrics has already been established in [24].

#### 1.4.2 Critical Read Stability $(T_{read})$

Figure 1.6 illustrates an SRAM bitcell undergoing read stress with pulse-widths  $T_A$  and  $T_B$ . Pulse-width  $T_A$  is short enough that the internal nodes (CH and CL) return back to their original levels after the word-line pulse. The longer pulse-width  $T_B$  subjects the bitcell to too much read stress, causing the cell to flip to an opposite state after the word-line pulse. There exists a pulse-width,  $T_{read}$  ( $T_A < T_{read} < T_B$ ), where the bitcell is on the threshold of a read upset, that is defined as the critical read stability. This is similar to the dynamic read failure criteria defined in [37]. This metric does not require access to the internal nodes of the SRAM cell. A subsequent read operation (read-back) is used to verify the contents of the bitcell and to determine if a read disturb had occurred. This read-back operation however needs to be performed under operating conditions which guarantee a correct read operation. This is usually done by raising the supply voltage of the bitcell to improve read stability.

A bitcell with positive static read margin will have infinite  $T_{read}$  while a bitcell with zero or negative static read margin will have a finite value of  $T_{read}$ . With the SRRV margin, it is possible to characterize a negative static read margin for a particular bitcell by measuring how much additional bitcell  $V_{DD}$  ( $V_{CELL}$ ), above the nominal voltage, is required to maintain the stored state of the bitcell. Figure 1.7 plots the positive correlation observed between SRRV and  $T_{read}$  extracted from Monte-Carlo simulations. Although  $T_{read}$  is observed to be exponentially dependent on static read margin, it is impossible to accurately estimate exact values of critical read stability from a voltage screen test at elevated  $V_{CELL}$  due to the large dispersion (up to 10x) observed in  $T_{read}$  at a particular SRRV.

SRAM access with read-after-read operation presents the worst-case condition for critical read stability [37, 62]. Figure 1.8 illustrates the waveforms corresponding to an SRAM bitcell with read-after-read access. The SRAM bitcell is stable after the first word-line pulse but is subsequently corrupted by the second pulse. It is therefore important to characterize  $T_{read}$  as a function of the number of read-after-read pulses as well as the access frequency.

#### 1.5 Writeability Metrics

#### 1.5.1 Static Writeability Margins