## **Sense Amplifier-Based Pass Transistor Logic**

Louis Poblete Alarcon Jan M. Rabaey

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-173 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-173.html

December 19, 2010

Copyright © 2010, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Sense Amplifier-Based Pass Transistor Logic

by

Louis Poblete Alarcón

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Jan M. Rabaey, Chair Professor Elad Alon Professor Paul K. Wright

Fall 2010

Sense Amplifier-Based Pass Transistor Logic

Copyright 2010 by Louis Poblete Alarcón

#### Abstract

Sense Amplifier-Based Pass Transistor Logic

by

Louis Poblete Alarcón

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Jan M. Rabaey, Chair

Reducing the energy required per operation is the key to building ultra-low energy systems, and the most effective way of achieving this is to reduce the supply voltage. However, operating CMOS circuits at low supply voltages increases circuit delay, leading to lower circuit performance. In this region, the sub-threshold leakage energy component becomes more pronounced and can even dominate the total circuit energy. Increasing threshold voltages reduces the amount of leakage, but this forces operation in the sub-threshold region where performance and variability become exponentially worse.

The use of the sense amplifier-based pass transistor logic (SAPTL) topology is one approach to reducing the energy per operation. It uses an inverted pass transistor logic (PTL) tree, which inherently has no gain, and hence no power supply connections, eliminating the sources of sub-threshold leakage current. Reducing the threshold voltages of the PTL transistors improves performance, without the leakage current increase associated with conventional static CMOS logic. This reduced threshold voltage also allows the PTL transistors to operate in the super-threshold region, even for very low supply voltages, avoiding the increased delay and variability associated with the sub-threshold operating regime.

Gain is introduced by using drivers and sense amplifiers (SAs) that restore the output voltage swing and provide the appropriate output current to drive the fan-out capacitances. These drivers and SAs are the primary source of sub-threshold leakage, which can be amortized by making the PTL networks complex, and by applying various leakage reduction techniques.

SAPTL-based 90nm test circuits using both synchronous and asynchronous timing schemes have been designed, fabricated and tested. These circuits show leakage and energy characteristics better than the equivalent static CMOS circuits. These test chips also demonstrate rudimentary SAPTL-based design flows using commercially available CAD tools.

Simulation and measurement results of basic synchronous SAPTL building blocks show a

40X-50X reduction in standby current and a 6X reduction in energy when compared to an equivalent CMOS logic block, at the expense of a 10X-30X increase in delay. Operating the SAPTL asynchronously reduces the average delay by 89%. However, adding the necessary handshaking circuitry increases the energy by 31%.

These SAPTL building blocks are used to create a parallel 64-byte asynchronous SAPTLbased CRC generator with a minimum energy point that is 25% lower than that of the static CMOS equivalent, with a 6X delay penalty. Also, due to the nature of the PTL tree, forward-biasing the body of the PTL transistors results in a 10% reduction in delay with no energy penalty.

The advantages of the SAPTL over conventional static CMOS is expected to be more significant as technology continues to scale, where subthreshold leakage continue to prevent supply voltages from being aggressively scaled.

## Contents

| Li            | List of Figures iv               |                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                        |  |

|---------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $\mathbf{Li}$ | st of                            | Tables                                                                                                                                                                                                                                                                                                                                           | viii                                                                                                                                                                   |  |

| 1             | <b>Intr</b><br>1.1               | oduction<br>Overview                                                                                                                                                                                                                                                                                                                             | <b>1</b><br>1                                                                                                                                                          |  |

|               | 1.2                              | Thesis Flow and Organization                                                                                                                                                                                                                                                                                                                     | 2                                                                                                                                                                      |  |

| <b>2</b>      | Ultr                             | ra-Low Energy Design                                                                                                                                                                                                                                                                                                                             | 3                                                                                                                                                                      |  |

|               | 2.1<br>2.2<br>2.3<br>2.4<br>2.5  | Characteristics of CMOS Logic         2.1.1       The CMOS Inverter         2.1.2       Delay         2.1.3       Power         2.1.4       Energy         A Sampling of Low Energy Design Techniques         Fundamental Limits         2.3.1       Variability         2.3.2       Subthreshold Leakage         Leakage and Gain       Summary | $     \begin{array}{c}       3 \\       4 \\       6 \\       7 \\       8 \\       9 \\       11 \\       12 \\       12 \\       13 \\       14 \\     \end{array} $ |  |

| 3             | Pass<br>3.1<br>3.2<br>3.3<br>3.4 | s Transistor Logic         Basic PTL Topologies         PTL Operation and Circuit Gain         3.2.1         Leakage in PTL Circuits         3.2.2         The Effect of Adding Gain         3.2.3         Decoupled Operation         Alternative Gain Elements         3.3.1         Sense Amplifiers         Summary                          | <ul> <li>16</li> <li>19</li> <li>19</li> <li>20</li> <li>20</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> </ul>                                                 |  |

| <b>4</b>      | The                              | SAPTL Organization                                                                                                                                                                                                                                                                                                                               | <b>25</b>                                                                                                                                                              |  |

|          | 4.1  | The SAPTL logic block                                                                                                                                               |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

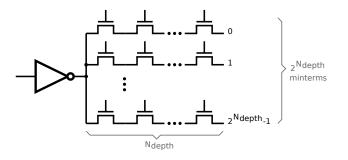

|          | 4.2  | The Inverted PTN Multiplexer Tree                                                                                                                                   |

|          | 4.3  | The Full Stack                                                                                                                                                      |

|          | 4.4  | The Simple Stack                                                                                                                                                    |

|          |      | 4.4.1 A First Order Delay Model                                                                                                                                     |

|          |      | 4.4.2 Simple Stack Energy                                                                                                                                           |

|          | 4.5  | Analysis of The Differential Full Stack                                                                                                                             |

|          | 4.6  | Stack Minimization                                                                                                                                                  |

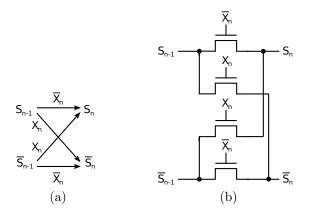

|          |      | 4.6.1 The XOR Logic Function                                                                                                                                        |

|          |      | 4.6.2 A Full-Adder Implementation                                                                                                                                   |

|          | 4.7  | Stack Implementation and Variability                                                                                                                                |

|          | 4.8  | Differential Stack Operation                                                                                                                                        |

|          |      | 4.8.1 The Stack Output Voltage                                                                                                                                      |

|          |      | 4.8.2 The Weak Output Latch                                                                                                                                         |

|          | 4.9  | The Sense Amplifier 43                                                                                                                                              |

|          |      | 4.9.1 Sense Amplifier Design                                                                                                                                        |

|          |      | 4.9.2 Delay and Energy                                                                                                                                              |

|          | 4.10 | Decoupling Functionality and Gain                                                                                                                                   |

|          | 4.11 | Summary                                                                                                                                                             |

|          |      |                                                                                                                                                                     |

| <b>5</b> | SAI  | PTL Timing 54                                                                                                                                                       |

|          | 5.1  | Synchronous SAPTL Operation                                                                                                                                         |

|          |      | 5.1.1 Two-Phase Clocking $\ldots \ldots 56$                                                          |

|          |      | 5.1.2 Synchronous SAPTL Design                                                                                                                                      |

|          | 5.2  | Asynchronous Operation                                                                                                                                              |

|          |      | 5.2.1 The Delay Line-based Asynchronous SAPTL 59                                                                                                                    |

|          |      | 5.2.2 The Asynchronous SAPTL Operation without a Delay Line 62                                                                                                      |

|          |      | 5.2.3 The Cost of Asynchrony $\ldots \ldots \ldots$ |

|          | 5.3  | An Example: The SAPTL XOR gate                                                                                                                                      |

|          | 5.4  | Summary                                                                                                                                                             |

| 6        | Car  | e Studies 70                                                                                                                                                        |

| 0        | 6.1  |                                                                                                                                                                     |

|          | 0.1  | J 1                                                                                                                                                                 |

|          |      | 1                                                                                                                                                                   |

|          |      | 1 0                                                                                                                                                                 |

|          |      |                                                                                                                                                                     |

|          | ເງ   | 6.1.4Summary75The Asynchronous SAPTL Test Chip78                                                                                                                    |

|          | 6.2  | · ·                                                                                                                                                                 |

|          |      | 6.2.1Design Methodology786.2.2Test Chip Organization79                                                                                                              |

|          |      | 1 0                                                                                                                                                                 |

|          |      |                                                                                                                                                                     |

|          | 6 9  | 6.2.4 Summary                                                                                                                                                       |

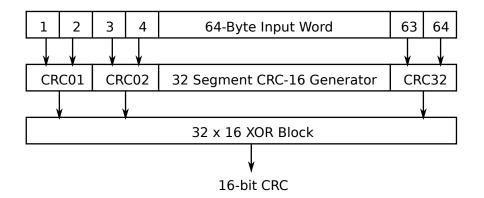

|          | 6.3  | The SAPTL CRC Circuit                                                                                                                                               |

|              |                                                        | 6.3.1  | The CRC Algorithm          | . 85 |  |  |

|--------------|--------------------------------------------------------|--------|----------------------------|------|--|--|

|              |                                                        | 6.3.2  | Implementation             | . 86 |  |  |

|              |                                                        | 6.3.3  | Simulation Results         | . 89 |  |  |

|              |                                                        | 6.3.4  | Measurement Results        | . 91 |  |  |

|              |                                                        | 6.3.5  | Summary                    | . 93 |  |  |

|              | 6.4                                                    | Conclu | usions                     | . 93 |  |  |

| 7            | 7.1                                                    | Contri | and Conclusions<br>butions |      |  |  |

| 8            | Rec                                                    | ommer  | ndations and Future Work   | 100  |  |  |

| Bi           | Bibliography                                           |        |                            |      |  |  |

| $\mathbf{A}$ | A Exploring the $V_{TH}$ Space: A Simulation Technique |        |                            |      |  |  |

# List of Figures

| 2.1 | A generalized complementary CMOS logic gate                                                             | 4   |

|-----|---------------------------------------------------------------------------------------------------------|-----|

| 2.2 | A CMOS inverter driving a capacitive load.                                                              | 5   |

| 2.3 | CMOS inverter delay as a function of $V_{DD}$                                                           | 6   |

| 2.4 | CMOS inverter power as a function of $V_{DD}$                                                           | 8   |

| 2.5 | CMOS inverter energy per operation as a function of $V_{DD}$                                            | 9   |

| 2.6 | The energy-delay plot of the 65nm CMOS inverters.                                                       | 10  |

| 2.7 | Theoretical energy and voltage limits                                                                   | 11  |

| 2.8 | A NAND4 gate implemented using (a) a single gate and (b) multiple gates.                                | 13  |

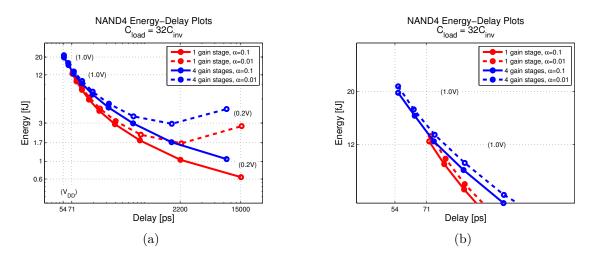

| 2.9 | The CMOS NAND4 gate: (a) energy-delay characteristics and (b) details at high supply voltages           | 1 / |

|     | high supply voltages                                                                                    | 14  |

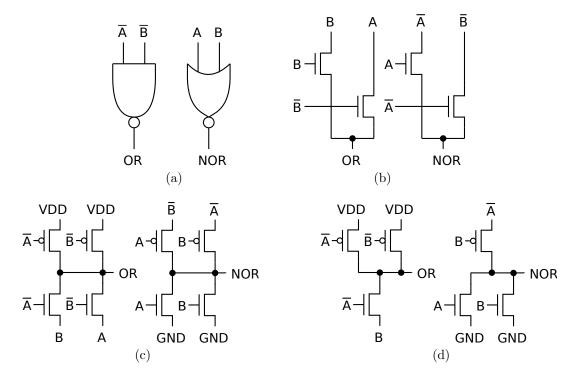

| 3.1 | $\mathrm{OR}/\mathrm{NOR}$ implementations in (a) CMOS, (b) CPL, (c) DPL and (d) DVL. $% \mathcal{A}$ . | 17  |

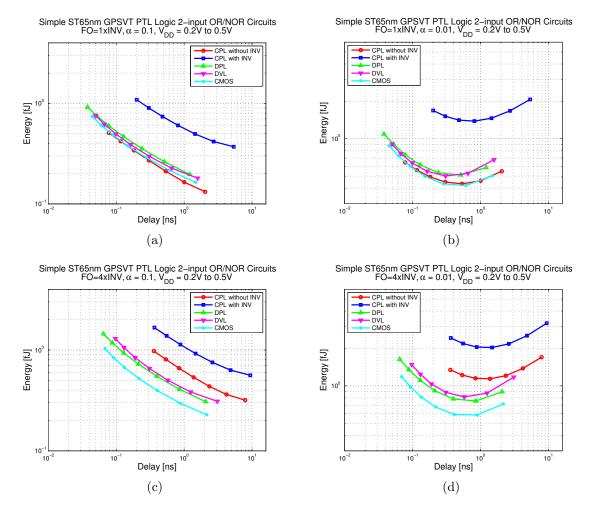

| 3.2 | PTL 2-input OR/NOR energy-delay characteristics: (a) $\alpha = 0.1$ and loaded                          |     |

|     | with a 1X INV, (b) $\alpha = 0.01$ and loaded with a 1X INV, (c) $\alpha = 0.1$ and                     |     |

|     | loaded with a 4X INV and (d) $\alpha = 0.01$ and loaded with a 4X INV                                   | 18  |

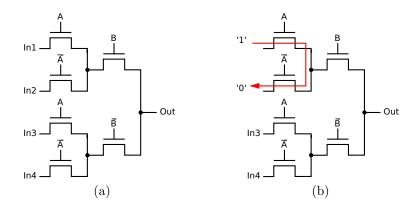

| 3.3 | The pass transistor multiplexer tree (a) with $N_{depth} = 2$ and (b) a sneak path.                     | 19  |

| 3.4 | A pass transistor network (a) with no gain elements and (b) with gain at the                            |     |

|     | output and internal nodes                                                                               | 20  |

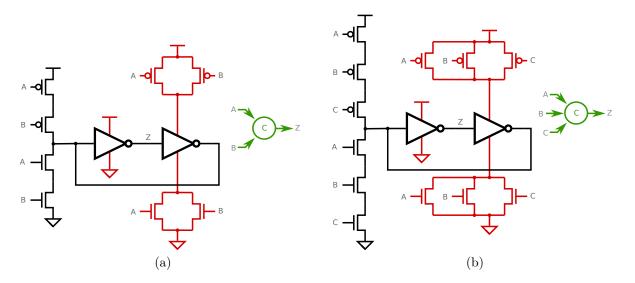

| 3.5 | The PTL energy and delay as a function of gain.                                                         | 21  |

| 3.6 | Alternative gain elements: (a) a sense amplifier and (b) a regenerative element.                        | 22  |

| 3.7 | A generalized PTL model                                                                                 | 24  |

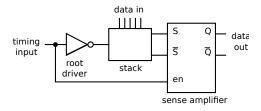

| 4.1 | The SAPTL logic block.                                                                                  | 26  |

| 4.2 | The inverted pass transistor tree network (a) with two inputs and (b) config-                           |     |

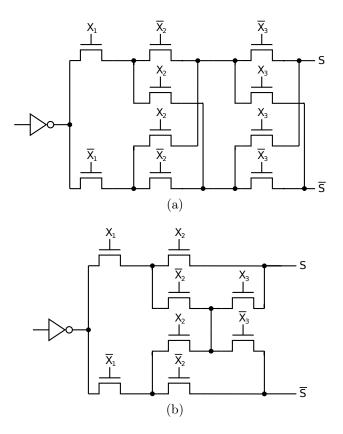

|     | ured as a two-input OR/NOR stack.                                                                       | 26  |

| 4.3 | The full stack and driver showing (a) the logic paths and (b) switches for                              |     |

|     | reconfigurability.                                                                                      | 27  |

| 4.4 | The simple stack (a) schematic and (b) rising transient model                                           | 29  |

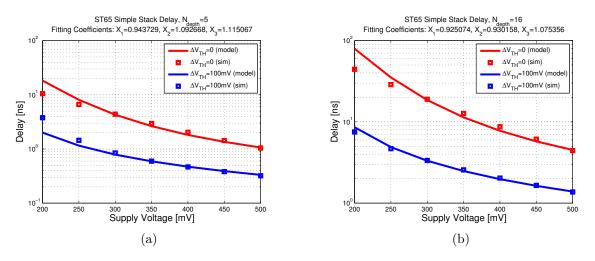

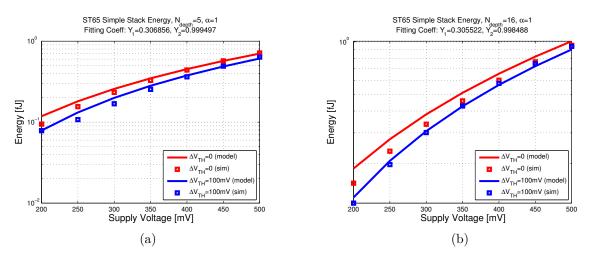

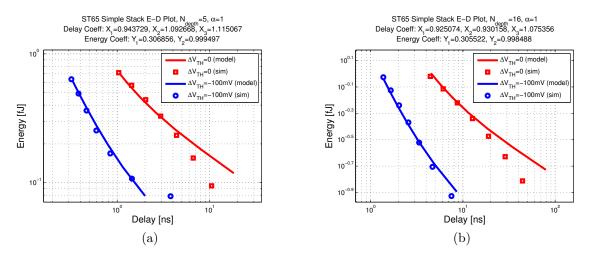

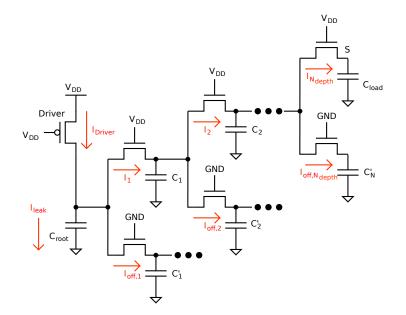

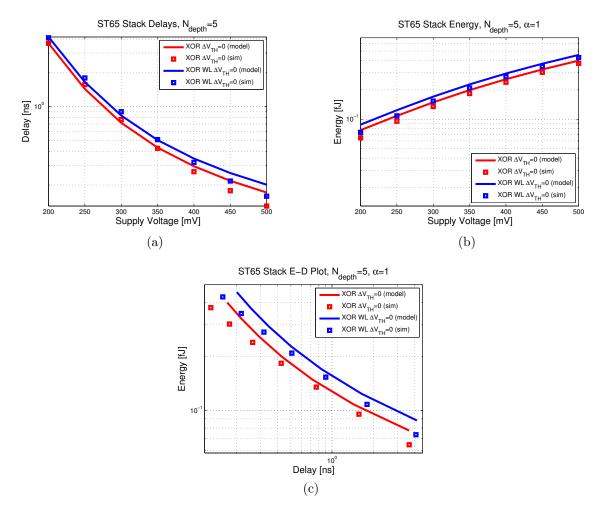

| 4.5 | The simple stack delay model for (a) $N_{depth} = 5$ and (b) $N_{depth} = 16$                           | 30  |

| 4.6 | The simple stack energy mode for (a) $N_{depth} = 5$ and (b) $N_{depth} = 16$                           | 31  |

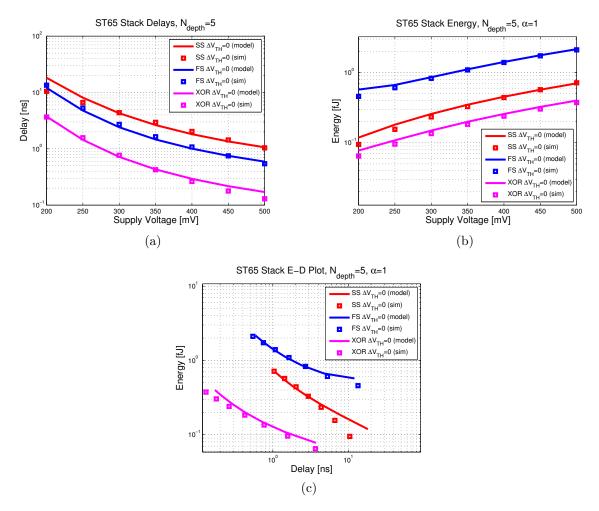

| 4.7 | The simple stack energy-delay model for (a) $N_{depth} = 5$ and (b) $N_{depth} = 16$ .                  | 32  |

| 4.8 | The full stack rising transient model.                                                                  | 33  |

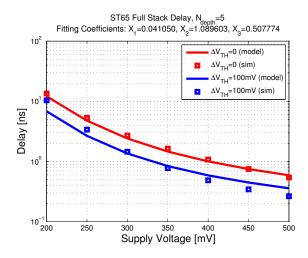

| 4.9 | The full stack delay model                                                                              | 34  |

|                | The full stack energy model (a) vs. $V_{DD}$ and (b) vs. delay. $\ldots$ $\ldots$ $\ldots$ The DCVSL OR/NOR gate with (a) a full pull-down tree and (b) a minimized   | 35         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

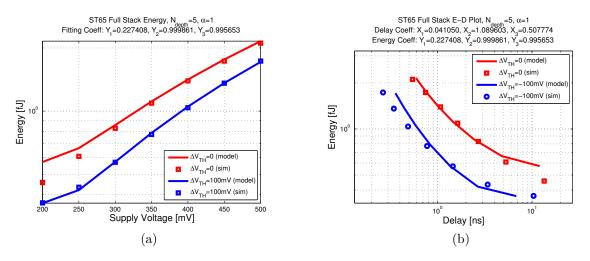

| <b>T</b> , I I |                                                                                                                                                                       | 36         |

| 1 19           | pull-down tree                                                                                                                                                        | 37         |

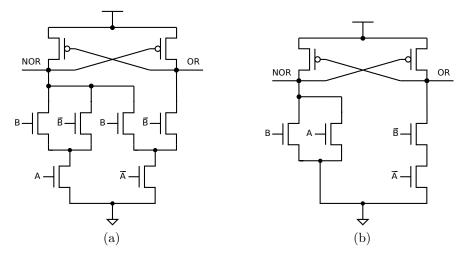

|                | The (a) delay, (b) energy and (c) energy-delay plots of the simple stack (SS),                                                                                        | 51         |

| 4.10           | full stack (FS) and XOR stack.                                                                                                                                        | 38         |

| 1 1 1          |                                                                                                                                                                       | 39         |

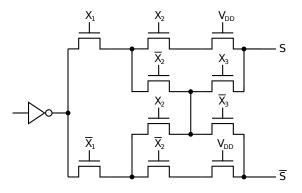

|                | The minimized stack-based full-adder (a) sum stage and (b) carry-out stage.<br>The carry-out full-adder function with balanced stack delays.                          | 39<br>40   |

|                | •                                                                                                                                                                     | 40<br>40   |

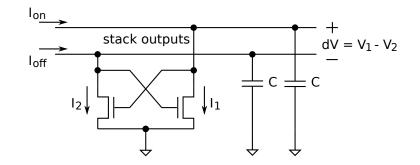

|                | Full stack implementation using an array of minimum-sized transistors The weak stack output latch                                                                     | 40<br>42   |

|                | 1                                                                                                                                                                     | 42         |

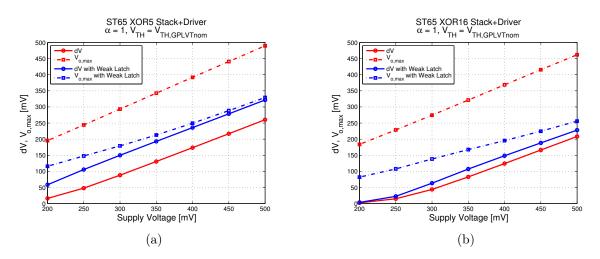

| 4.18           | The effect of the weak output latch on $dV$ and $V_{o,\text{max}}$ as a function of $V_{DD}$ for<br>(a) XOP5 and (b) XOP16 stacks                                     | 49         |

| 4 10           | (a) XOR5 and (b) XOR16 stacks.                                                                                                                                        | 42         |

| 4.19           | The effect of the weak output latch on $dV$ and $V_{o,\max}$ as a function of $V_{TH,stack}$                                                                          | 49         |

| 4.90           | for (a) XOR5 and (b) XOR16 stacks.                                                                                                                                    | 43         |

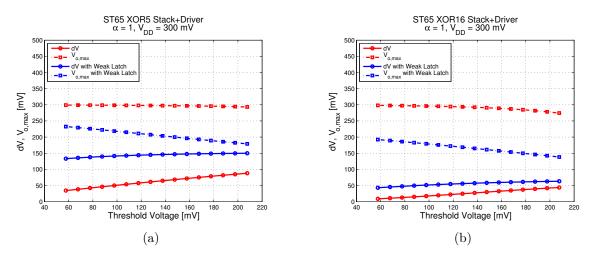

| 4.20           | The (a) delay, (b) energy and (c) energy-delay characteristics of an XOR5                                                                                             | 4.4        |

| 4.01           | stack with and without a weak output latch.                                                                                                                           | 44         |

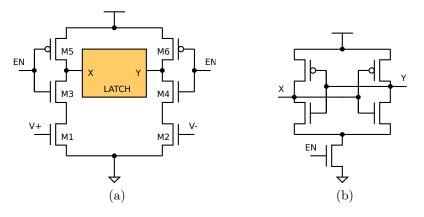

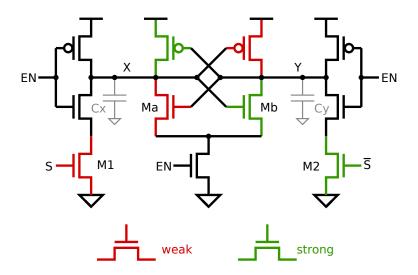

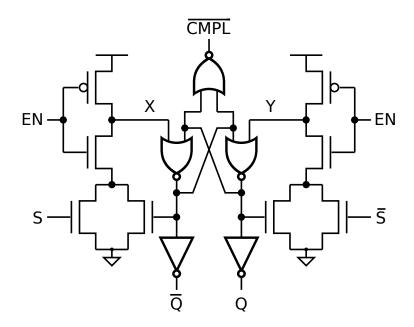

|                | The basic SAPTL sense amplifier (a) pre-amplifier and (b) latch                                                                                                       | 45         |

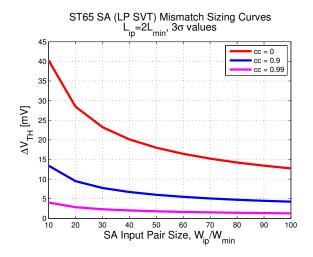

|                | Sense amplifier input transistor $\Delta V_{TH}$ as a function of input transistor width.                                                                             | 46         |

|                | The sense amplifier worst-case mismatch scenario. $\dots \dots \dots$ | 47         |

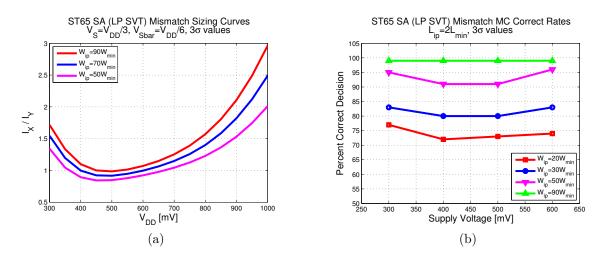

| 4.24           | The effect of $V_{DD}$ on (a) the modeled SA $\frac{I_X}{I_Y}$ ratio and (b) the Monte Carlo                                                                          | 10         |

| 4.05           | simulation of the correct SA decision rates.                                                                                                                          | 49         |

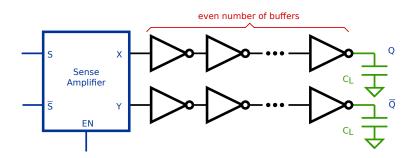

|                | Buffering the sense amplifier output.                                                                                                                                 | 49         |

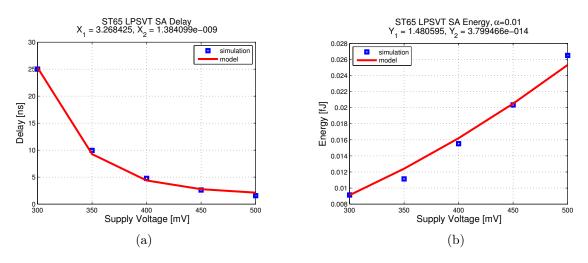

|                | The sense amplifier (a) delay and (b) energy models.                                                                                                                  | 50         |

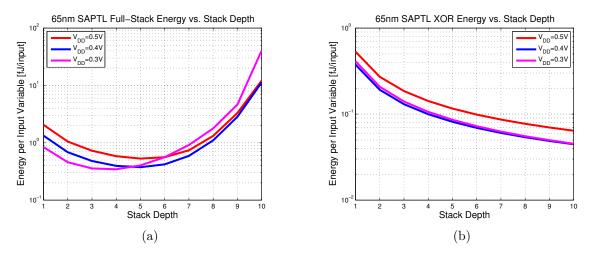

| 4.27           | The SAPTL energy as a function of stack depth for (a) a full-stack and (b)                                                                                            | <b>F</b> 1 |

| 4.00           | for an XOR stack.                                                                                                                                                     | 51         |

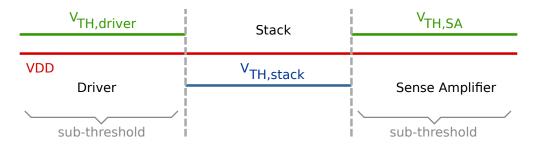

| 4.28           | A possible SAPTL $V_{DD}$ and $V_{TH}$ scenario where the driver, stack and sense                                                                                     |            |

|                | amplifier operate in different regions within one SAPTL block                                                                                                         | 52         |

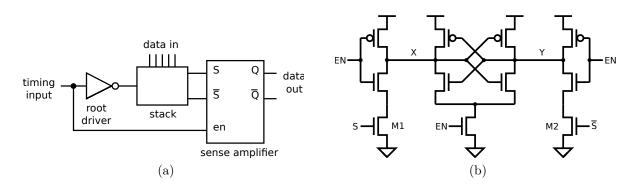

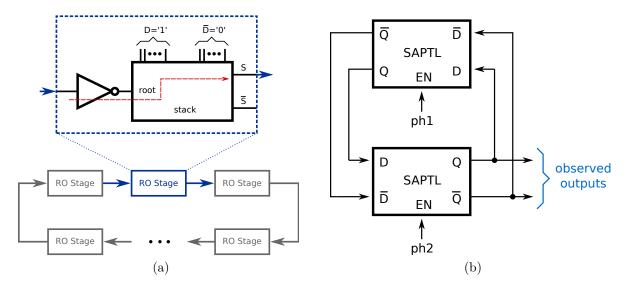

| 5.1            | The SAPTL (a) logic block organization and (b) sense amplifier                                                                                                        | 54         |

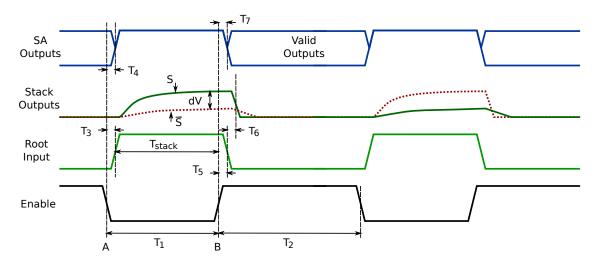

| 5.2            | The clocked SAPTL timing diagram.                                                                                                                                     | 55         |

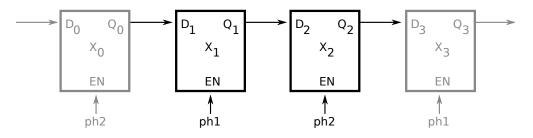

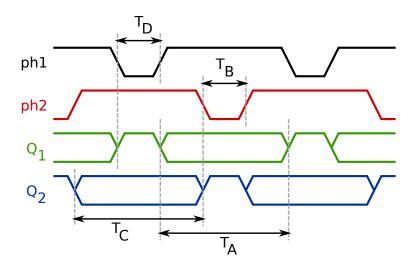

| $5.2 \\ 5.3$   | Cascaded SAPTL blocks using two-phase clocking.                                                                                                                       | 56         |

| 5.4            | The two-phase synchronous SAPTL operation.                                                                                                                            | 56         |

| 5.5            | Stack initialization.                                                                                                                                                 | 50<br>57   |

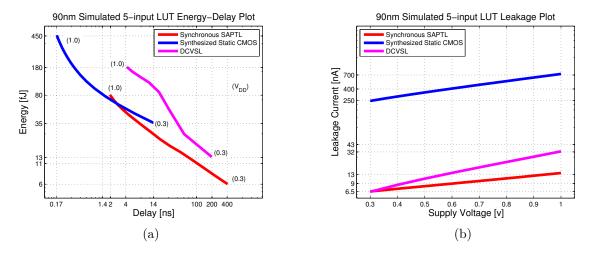

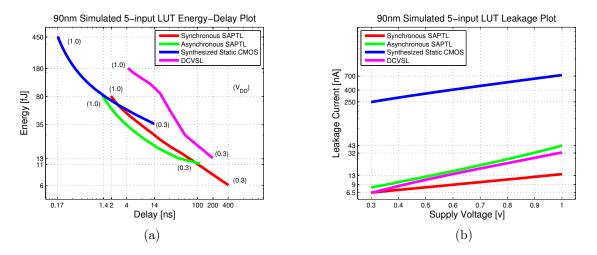

| 5.6            | The synchronous SAPTL5 (a) energy-delay characteristics and (b) leakage                                                                                               | 51         |

| 5.0            | current.                                                                                                                                                              | 58         |

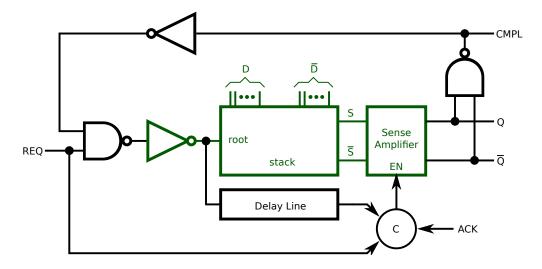

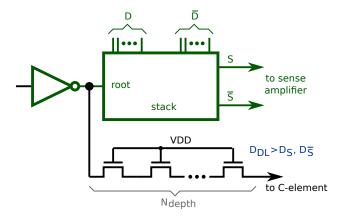

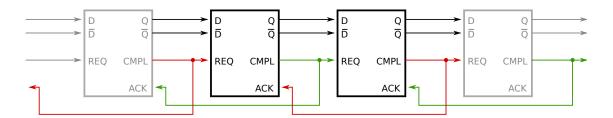

| 5.7            | The delay line-based asynchronous SAPTL.                                                                                                                              | 60         |

| 5.8            | The delay line.                                                                                                                                                       | 60         |

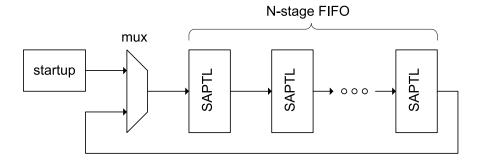

| 5.9            | Simple DL-SAPTL pipeline.                                                                                                                                             | 60         |

| 5.9<br>5.10    | The DL-SAPTL timing diagram.                                                                                                                                          | 61         |

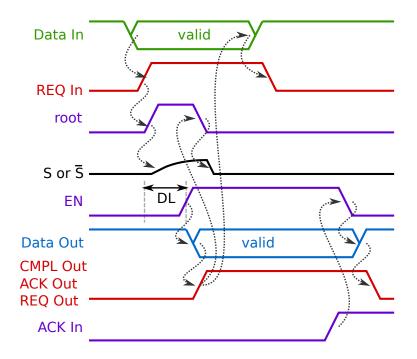

| 5.10           |                                                                                                                                                                       | 61<br>62   |

| 5.11           |                                                                                                                                                                       | 63         |

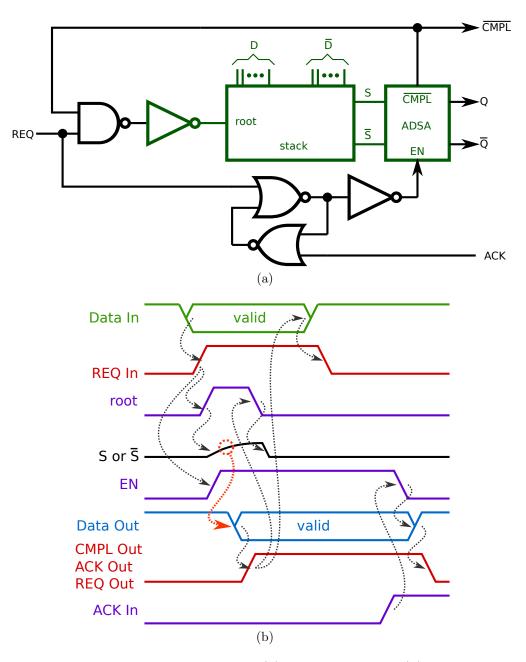

|                | The ADSA-based SAPTL (a) architecture and (b) timing diagram.                                                                                                         | 03<br>65   |

| 0.10           | THE REPORT DATE IN (a) ALTIMETURE AND (D) UNING MARIAN.                                                                                                               | 00         |

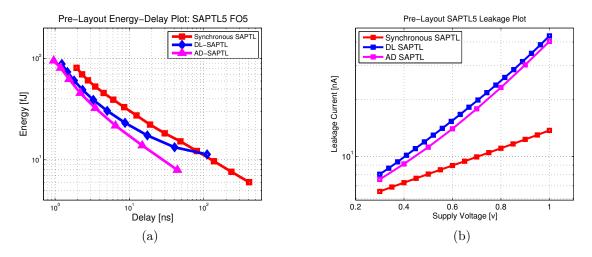

| 5.14                                      | Comparison of the (a) energy-delay characteristics and (b) leakage currents of the AD-SAPTL, DL-SAPTL and the synchronous SAPTL as $V_{DD}$ is increased                |          |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                           | from 0.3V to 1V. $\ldots$                                                              | 66       |

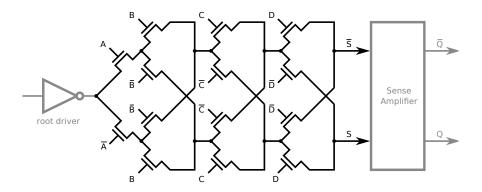

|                                           | 4-input SAPTL XOR stack.                                                                                                                                                | 67       |

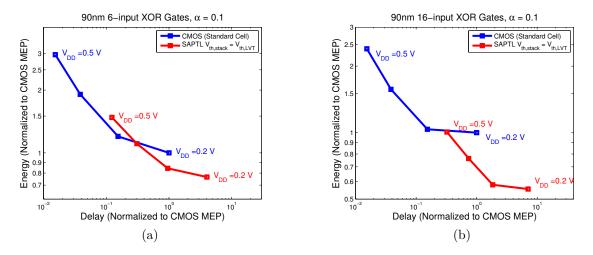

| 5.16                                      | AD-SAPTL XOR gate energy-delay characteristics for (a) 6-inputs and (b) 16-inputs.                                                                                      | 68       |

| 6.1                                       | The synchronous SAPTL test blocks: (a) the ring oscillator without a sense                                                                                              |          |

|                                           | amplifier and (b) the back-to-back SAPTL blocks                                                                                                                         | 71       |

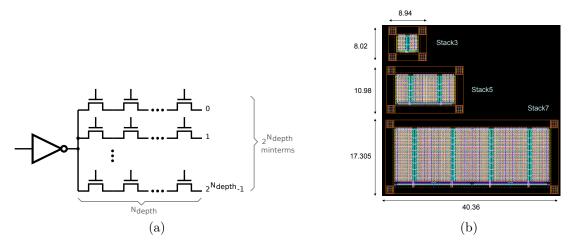

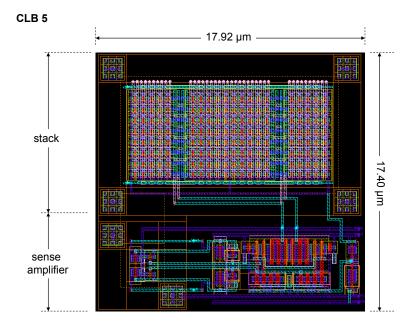

| 6.2                                       | The pass transistor stack implementation showing (a) the stack layout strategy                                                                                          |          |

|                                           | and (b) the relative layout sizes of the 90nm SAPTL stacks                                                                                                              | 72       |

| 6.3                                       | The synchronous 90nm SAPTL5 layout.                                                                                                                                     | 72       |

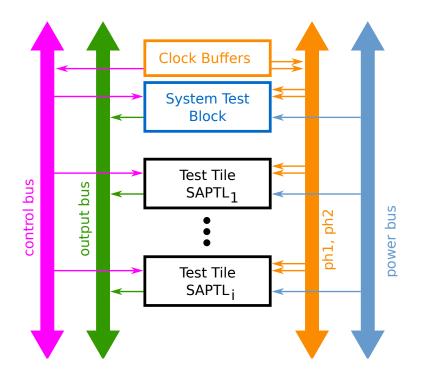

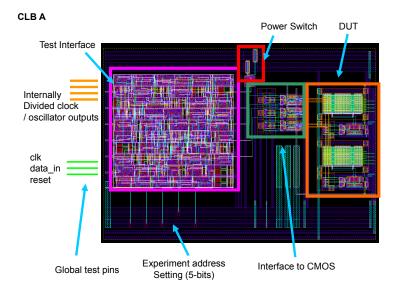

| 6.4                                       | Synchronous SAPTL test chip architecture                                                                                                                                | 73       |

| 6.5                                       | Synchronous SAPTL test tile organization                                                                                                                                | 74       |

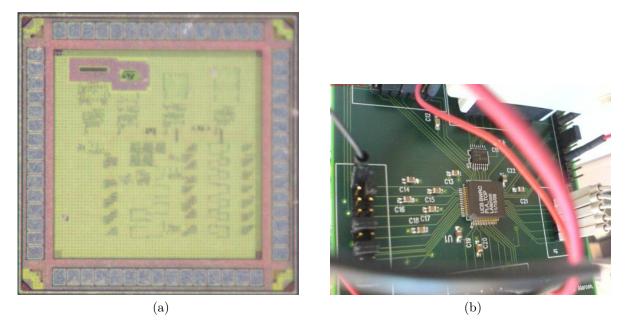

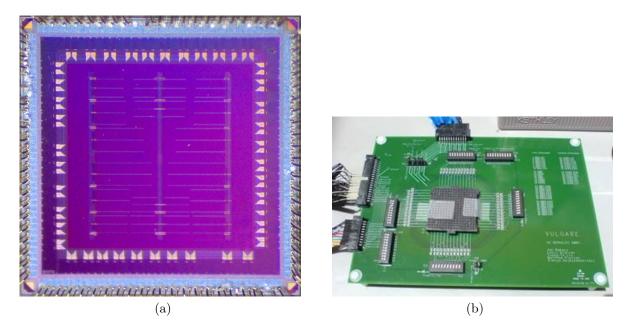

| $\begin{array}{c} 6.6 \\ 6.7 \end{array}$ | The synchronous SAPTL (a) test chip and (b) packaged chip and circuit board.<br>Simulated vs. measured stack delays for (a) $N_{depth} = 3$ , (b) $N_{depth} = 5$ , (c) | 75       |

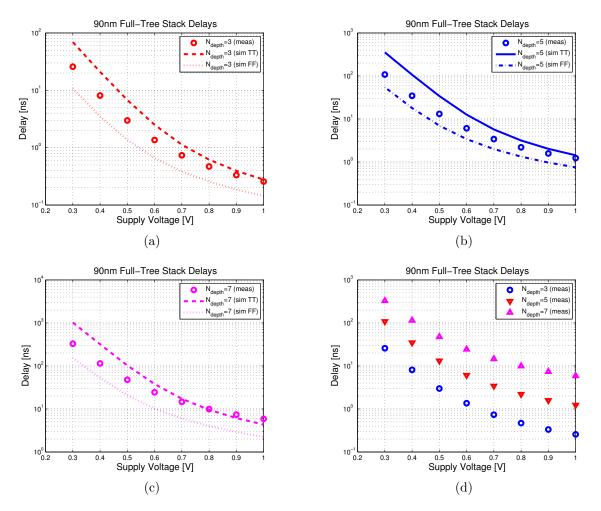

|                                           | $N_{depth} = 7.$ (d) shows the measured stack delays vs. stack depth                                                                                                    | 76       |

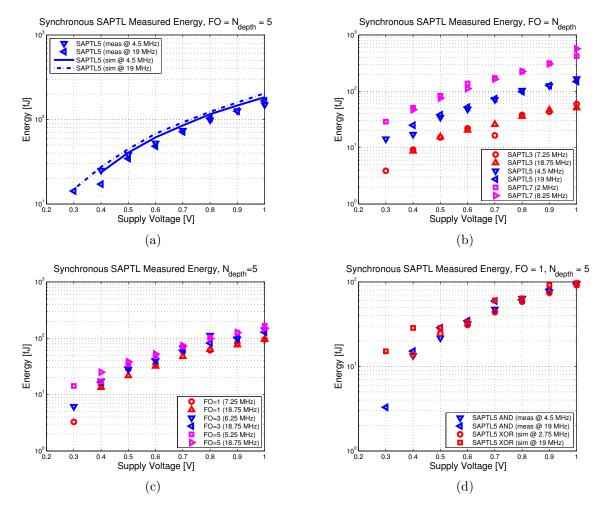

| 6.8                                       | Measured energy vs. $V_{DD}$ of (a) a synchronous SAPTL5 logic block, (b)                                                                                               |          |

|                                           | measured energy vs. $V_{DD}$ with varying stack depth, (c) fanout and (d) logic                                                                                         |          |

|                                           | functionality.                                                                                                                                                          | 77       |

| 6.9                                       | Test setup for energy and delay measurements. The energy and delay of the                                                                                               |          |

|                                           | various SAPTL5 implementations were measured using $N = 8. \ldots \ldots$                                                                                               | 78       |

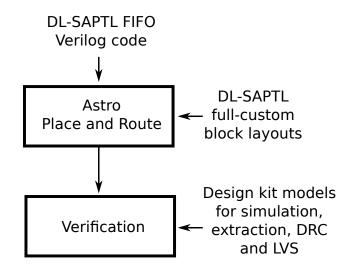

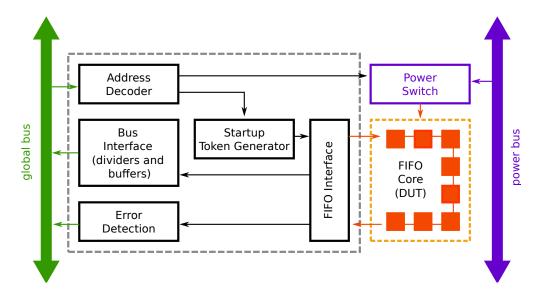

| 6.10                                      | The asynchronous SAPTL tool flow.                                                                                                                                       | 79       |

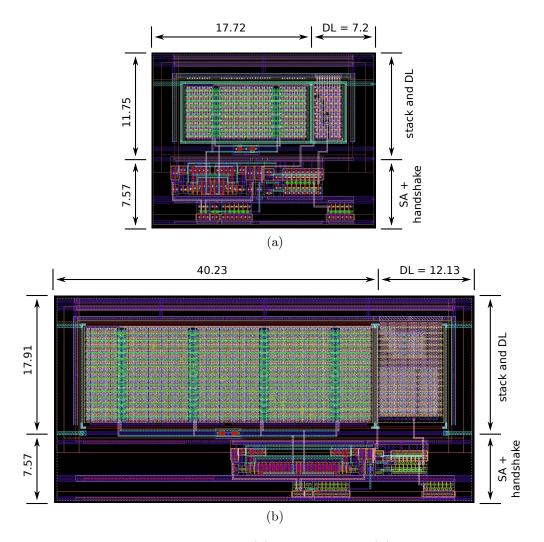

| 6.11                                      | The asynchronous (a) SAPTL5 and (b) SAPTL7 layouts                                                                                                                      | 80       |

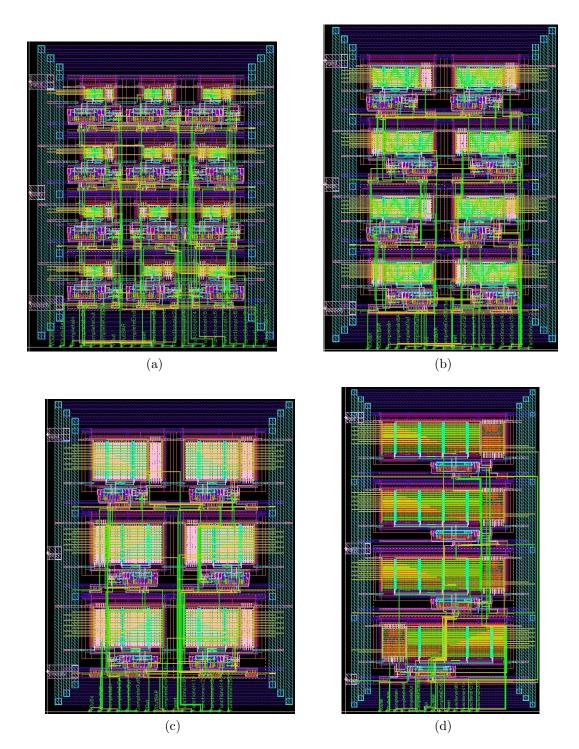

|                                           | The automatically generated asynchronous FIFO circuits using (a) SAPTL3,                                                                                                |          |

|                                           | (b) SAPTL5, (c) SAPTL6 and (d) SAPTL7                                                                                                                                   | 81       |

| 6.13                                      | The asynchronous SAPTL test tile.                                                                                                                                       | 82       |

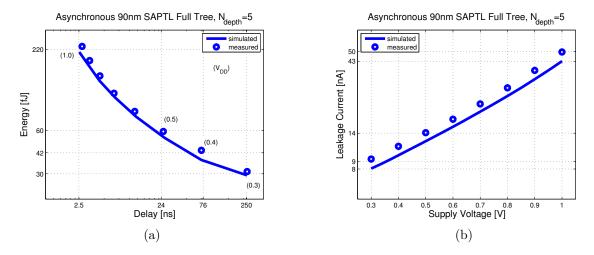

| 6.14                                      | The asynchronous SAPTL5 (a) energy-delay characteristics and (b) leakage                                                                                                | 83       |

| 6 15                                      | current                                                                                                                                                                 | 00       |

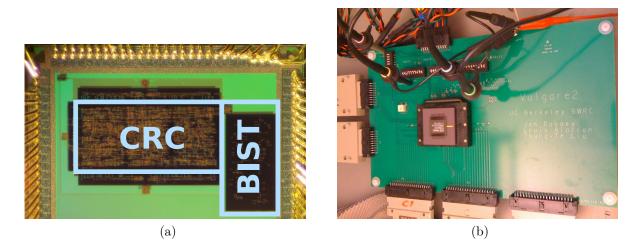

| 0.15                                      | The (a) asynchronous SAPTL test chip, also known as the Vulgare test chip<br>and (b) the Vulgare circuit board                                                          | 09       |

| 6 16                                      |                                                                                                                                                                         | 83       |

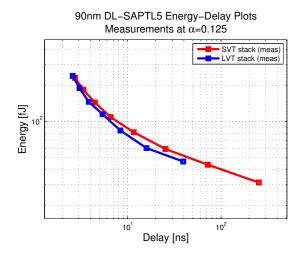

| 0.10                                      | The DL-SAPTL5 SVT stack measured (a) energy-delay characteristics and                                                                                                   | 01       |

| 6 17                                      | (b) leakage current                                                                                                                                                     | 84<br>85 |

|                                           | The effect of stack threshold on the DL-SAPTL5 energy-delay characteristics.                                                                                            | 85<br>86 |

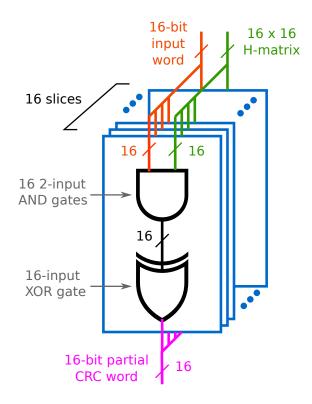

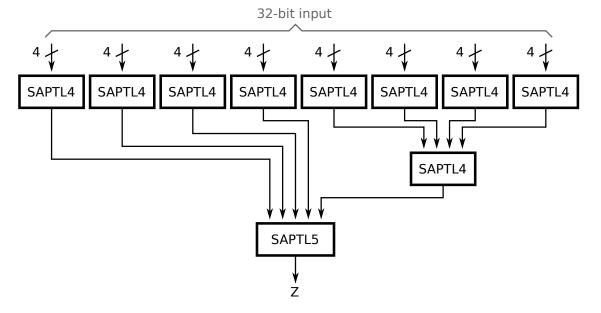

|                                           | The SAPTL CRC-CCITT generator                                                                                                                                           | 87       |

|                                           | 0                                                                                                                                                                       | 87       |

|                                           | SAPTL CRC XOR templates for (a) 7 to 11 inputs and (b) 12 and 13 inputs.                                                                                                |          |

|                                           | SAPTL CRC 32-input XOR.       The SAPTL CRC tool flow.                                                                                                                  | 88       |

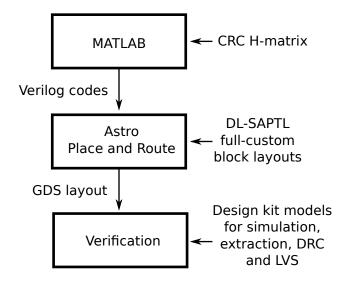

|                                           | SAPTL CRC tool now                                                                                                                                                      | 89<br>90 |

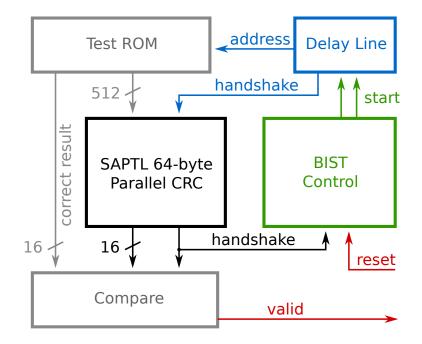

|                                           | • 0                                                                                                                                                                     | 90<br>90 |

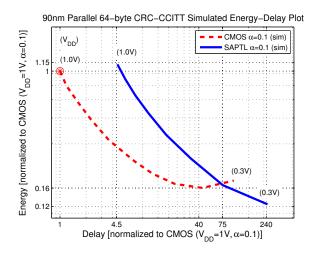

|                                           | Simulated SAPTL CRC-CCITT energy-delay characteristics                                                                                                                  | 90<br>91 |

| 0.20                                      | 1 10 10 - 511 11 0 100 (a) 100 0 100 and (b) 0 100 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                      | JI       |

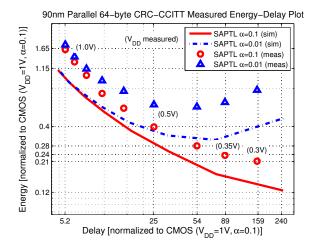

| Measured SAPTL CRC-CCITT energy-delay characteristics                    | 92                                                                                                          |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

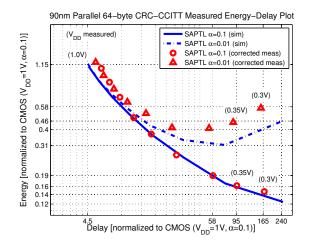

| The energy-delay characteristics of the measured SAPTL CRC-CCITT circuit |                                                                                                             |

| with the layout parasitics removed.                                      | 93                                                                                                          |

|                                                                          |                                                                                                             |

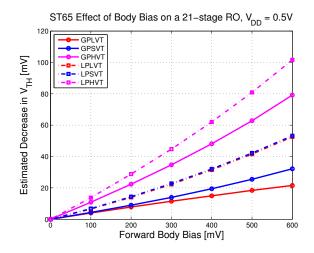

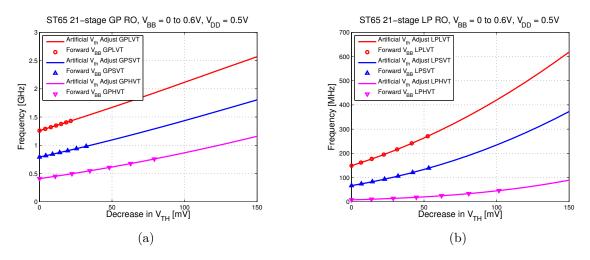

| The effectiveness of forward body bias                                   | 111                                                                                                         |

| Artificial threshold voltage reduction                                   | 111                                                                                                         |

| $V_{TH}$ reduction methods for (a) GP and (b) LP devices                 | 111                                                                                                         |

|                                                                          | The energy-delay characteristics of the measured SAPTL CRC-CCITT circuit with the layout parasitics removed |

# List of Tables

| 4.1 | The XOR stack transistor count.                      | 37 |

|-----|------------------------------------------------------|----|

|     | The SAPTL timing scheme (energy and delay) tradeoffs |    |

| 6.1 | 90nm pass transistor stack layout area comparison.   | 71 |

| 6.2 | SAPTL XOR W, X and Y values                          | 88 |

| 6.3 | Normalized delay (energy) of the SAPTL CRC generator | 92 |

#### Acknowledgments

A lot of people have helped me, one way or the other, to finish this thesis, and I would like to take this opportunity to say thank you...

... to my advisor, Jan Rabaey, for his constant support and patience, without which, this thesis would not have been possible.

... to Mircea Stan, who started all this, with talks and ideas about stacks and pass transistors; to Elad Alon, for all the excellent feedback; to John Wawrzynek and Paul Wright, for agreeing to be on my quals and thesis committee and to Marly Roncken and Ivan Sutherland for all the great help and insights.

... to Tsung-Te Liu, for being the best tapeout partner and for taking all the abuse I sent his way with a smile and the ever-present "can do" attitude.

... to the awesome *jansgroup* and the rest of the BWRC crowd, especially to Simone Gambini, Rikky Muller, Michael Mark, Jesse Richmond, David Chen, Matthew Pierson, Ping-Chen Huang, Arash Parsa, Wen Li, Ali Ercan, Jing Yang, Cristian Marcu, Amin Arbabian, and Maryam Tabesh, whose friendship made the whole process of getting this thesis done both fun and stimulating, with coffee and chocolate being the preferred stimulant.

... to Kimiya Hajkazemshirazi, Jayson Hu, Vittoria Lok, Sun Chen and Shuo Liu, for the amazing effort that really helped.

... to the tremendous BWRC faculty and administrative/support staff especially Ali Niknejad, Borivoje Nikolic, Andre Vladimirescu, Gary Kelson, Deirdre McAuliffe-Bauer, Ellen Lenzi, Pierce Chua, Kevin Zimmerman, Brian Richards, Susan Mellers, and Ken Tang for taking care of all of us at BWRC.

... to Tom Boot, for treating all of us like family.

... to Octavian Florescu, for being a great project partner in the early stages of the SAPTL, and to Ehsan Adabi, Bagher Afshar, Subramaniam Venkatraman, Alexandr Simma, Benjamin Rubinstein, Juliet Rubinstein, Leon Barrett, Zachary Anderson, Bonnie Kirkpatrick, Lauren Barth-Cohen, Anupama Bowonder, Pratik Patel, and Eric Chin for the great company and making sure I get out of the lab often enough.

.. to Amy Wu, for the love, friendship and understanding.

... to the University of the Philippines, Diliman and the UP Electrical and Electronics Engineering Department for giving me the time and support I needed everytime I asked for it, and to Richard Hizon, Marc Rosales, Anastacia Ballesil-Alvarez, Maria Teresa Gusad-de Leon and Joy Reyes-Madamba, for keeping my chair warm.

... to my parents, Wilfredo Alarcón and Maria Luisa Alarcón and my sisters Yazmynn and Maria Celine, for the love, encouragement and unwavering support.

... and to God, Ad maiorem Dei gloriam.

## Chapter 1

## Introduction

The ability to design and build logic and computational elements that operate at extremely low energy levels is seen as a very important enabler for systems in various application domains such as mobile devices, wireless sensor networks and bio-medical systems [Sak03]. Devices operating at these low energy levels can also take advantage of alternative energy storage and scavenging methods that can lead to almost indefinite operational lifetimes [CFK<sup>+</sup>10], as well as new computing and system paradigms.

Technology scaling and supply voltage reduction have been responsible for the continued energy reduction and performance improvement in complementary static CMOS circuits, the most popular logic topology in use today. However, the increased leakage energy brought about by scaling and  $V_{DD}$  reduction is starting to limit the minimum energy that static CMOS circuits can achieve. One low-energy alternative to complementary static CMOS circuits is the sense amplifier-based pass transistor logic (SAPTL) topology.

### 1.1 Overview

This work presents the sense amplifier-based pass transistor logic (SAPTL) as a low energy alternative logic topology to fully complementary static CMOS logic. The SAPTL takes advantage of the inherent decoupling of logic functionality and circuit gain in pass transistor circuits in order to achieve ultra-low energy operation that is lower than static CMOS, especially in cases where leakage energy becomes a significant component of total circuit energy. This decoupling also allows the improvement of performance through threshold voltage reduction without increasing the total SAPTL energy consumption.

## 1.2 Thesis Flow and Organization

Chapter 2 presents an overview of the low energy design, starting with the basics of how energy is consumed in digital circuits. Techniques on how energy consumption can be reduced, such as sub-threshold leakage current mitigation, as well as the challenges involved, are mentioned. Metrics showing how these reductions affect the performance of these circuits are then introduced.

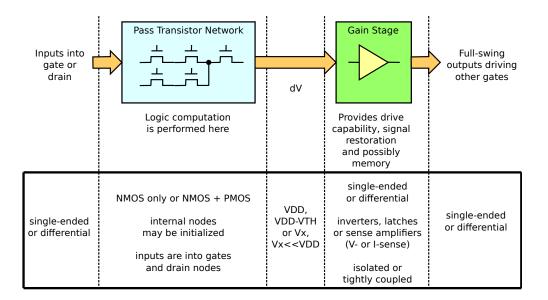

Pass transistor logic is introduced in Chapter 3 as a low leakage alternative to complementary static CMOS logic, since it operates inherently without built-in gain elements. The penalties of operating without gain, as well as ways to introduce more gain into the circuit are also presented.

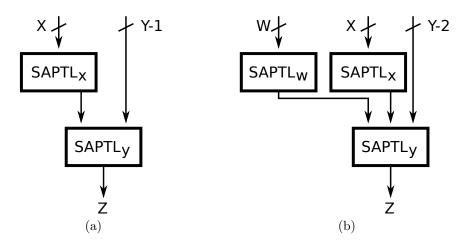

Chapter 4 introduces the basic organization of the sense amplifier-based pass transistor logic (SAPTL) circuit, which is built using (1) an inverted pass transistors tree, or stack, and (2) gain elements in the form of drivers and sense amplifiers. This is followed by an analysis of the delay and energy of these SAPTL building blocks and the implications of combining these two blocks in order to implement boolean functions.

The timing behavior of SAPTL is shown in Chapter 5. A two-phase clocking scheme as well as two asynchronous handshaking schemes are presented. The energy and delay characteristics of logic functions using these timing schemes are then compared with their corresponding complementary static CMOS implementations, highlighting design areas where using SAPTL will be advantageous. Chapter 6 shows several examples of the SAPTL circuits, including practical design and implementation issues as well as measurement results of fabricated circuits.

Chapter 7 presents the conclusions drawn from this work, and then recommendations as well as possible future extensions of this thesis are presented in Chapter 8.

## Chapter 2

## Ultra-Low Energy Design

The continued scaling of CMOS technology provides increased transistor density, as well as increased performance. Ideally, scaling also reduces the the overall circuit power consumption. However, due to nonidealities like leakage, scaling typically results in an increase in overall circuit power consumption and this increase in power that accompanies this scaling trend is preventing us from truly harnessing the benefits of decreasing transistor feature sizes [Sak03]. For applications (1) that are severely energy limited, such as those using implantable electronics [ROSO05] [GN04] or (2) where performance requirements are relaxed and energy is the primary constraint, such as RFID protocol processor systems [RGDMC09] and implantable integrated circuits [KGM09] with clock frequencies in the hundreds of kHz, the energy per operation must continue to decrease, allowing for years of battery life at relatively low operating frequencies and power levels.

The goal, therefore, of ultra-low energy design is to be able to create circuits and systems that consume the least amount of energy possible, while meeting application-specific constraints in the face of device and process nonidealities.

In this chapter, the relationship between energy, supply voltage, performance and MOS subthreshold leakage current of CMOS logic circuits are presented, leading to the main difficulties in reducing their energy per operation  $(E_{OP})$ . Various methodologies and techniques currently used to lower  $E_{OP}$  are then enumerated. The chapter concludes with a discussion on the possibilities of using pass transistor logic (PTL) as an alternative approach to reducing  $E_{OP}$  in certain application scenarios.

## 2.1 Characteristics of CMOS Logic

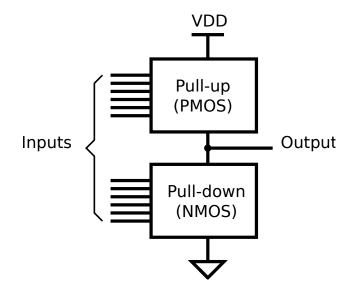

A generalized complementary static CMOS logic, shown in Fig. 2.1, is composed of a PMOS pull-up network, connecting the supply rail to the output and an NMOS pull-down network that connects the output to ground. These complementary pull-up and pull-down networks connects the output to either  $V_{DD}$  or ground, depending on the logic gate's input.

Figure 2.1: A generalized complementary CMOS logic gate.

The behavior of a generic complementary CMOS logic gate can be analyzed in terms of an equivalent CMOS inverter since its pull-up and pull-down networks can be modeled as a single equivalent PMOS or NMOS transistor. Thus, the CMOS inverter and its behavior, as described in this chapter, can be regarded as representative of the entire fully complementary CMOS logic family.

#### 2.1.1 The CMOS Inverter

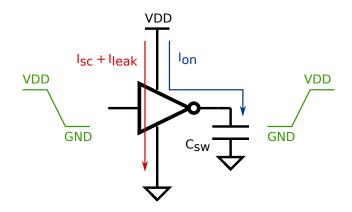

The current that a CMOS inverter draws from the supply voltage,  $V_{DD}$ , can be decomposed into three main components [RCN03], (1)  $I_{ON}$ , the switching or dynamic current used to charge up the capacitive load at its output,  $C_{sw}$ , (2)  $I_{leak}$ , the subthreshold leakage current and (3)  $I_{sc}$ , the short-circuit or direct path current, as seen in Fig. 2.2.

For supply voltages significantly above the threshold voltage [SN90][ZBSF05],

$$I_{ON,sat} = \frac{\mu_{eff} C_{ox}}{2} \frac{W}{L_{eff}} \left( V_{DD} - V_{TH} \right)^{\alpha_{mos}}$$

(2.1)

where  $\alpha_{mos} \approx 1.3$ . However, in the subthreshold region it can be expressed as [TN98][BRG05]

$$I_{ON,sub} = \mu_{eff} C_{ox} \frac{W}{L_{eff}} (m-1) V_T^2 e^{\frac{V_{DD} - V_{TH}}{mV_T}} \left( 1 - e^{-\frac{V_{DD}}{V_T}} \right)$$

(2.2)

Figure 2.2: A CMOS inverter driving a capacitive load.

where m is defined as

$$m = \left(1 + \frac{C_d}{C_{ox}}\right) = \frac{S_S}{\left(\ln 10\right) V_T} \tag{2.3}$$

and  $S_S$  is the subthreshold slope, given by

$$S_S = (\ln 10) V_T \left( 1 + \frac{C_d}{C_{ox}} \right) \tag{2.4}$$

where  $V_T = \frac{kT}{q}$ ,  $C_{ox}$  is the gate-oxide capacitance per unit area,  $C_d$  is the depletion region capacitance per unit area, W is the width and  $L_{eff}$  is the effective channel length of the MOS device.

The leakage current is the current that flows when  $V_{GS}$  is equal to zero, and is commonly dominated by subthreshold leakage currents [KAB<sup>+</sup>03], thus

$$I_{leak} = \mu_{eff} C_{ox} \frac{W}{L_{eff}} (m-1) V_T^2 e^{-\frac{V_{TH}}{mV_T}} \left(1 - e^{-\frac{V_{DS}}{V_T}}\right)$$

(2.5)

Note that at supply voltages less than the sum of the NMOS and PMOS threshold voltages, the short-circuit current,  $I_{sc}$ , becomes negligible [CB95]. Though the paths through which  $I_{leak}$  and  $I_{sc}$  take are the same,  $I_{sc}$  flows only when a transient event occurs. The leakage current, on the other hand, is the current that flows when the circuit node voltages settle to their final static values after a transient event.

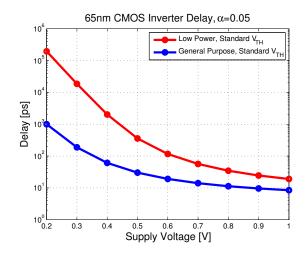

Figure 2.3: CMOS inverter delay as a function of  $V_{DD}$ .

#### 2.1.2 Delay

The delay in a CMOS gate can be expressed as

$$D = \frac{C_{sw} V_{DD}}{2I_{ON}} \tag{2.6}$$

Thus, the delay for above threshold operation can be expressed as a function of the supply voltage, as

$$D_{sat} \propto \frac{V_{DD}}{\left(V_{DD} - V_{TH}\right)^{\alpha_{mos}}} \tag{2.7}$$

and in the subthreshold region, assuming  $V_{DD} > 0.1$  V, such that  $1 - e^{-\frac{V_{DD}}{V_T}} \approx 1$ , the delay is

$$D_{sub} \propto V_{DD} e^{-\frac{V_{DD} - V_{TH}}{mV_T}} \tag{2.8}$$

As seen in Eqs. 2.7 and 2.8, decreasing the supply voltage increases the delay. Fig. 2.3 shows the delay of two flavors of 65nm CMOS inverters as a function of supply voltage.

In real systems, several CMOS gates are normally grouped into logic or pipeline stages in order to perform a certain function or operation, such as adding two numbers. If the time needed to complete this operation is defined as  $T_{OP}$ , then the activity factor of each gate *i* in the logic or pipeline stage can be defined as

$$\alpha_i = k_i \frac{D_i}{T_{OP}} \tag{2.9}$$

For an inverter, every change at its input causes a change at the outputs, hence, k = 1. For multiple-input gates, k can be less than 1 since not all changes at the gate input causes the output to change. For synchronous systems, on the other hand, if  $f_{sw}$  is the global clock frequency, where  $f_{sw} = \frac{1}{T_{OP}}$ , then  $\frac{1}{\alpha}$  can represent the average number of clock cycles between each output switching event of a particular gate or subsystem.

#### 2.1.3 Power

The average power consumed by the CMOS inverter for a low-to-high transition at its output can be expressed as the sum of the dynamic and leakage power components

$$P_{ave} = P_{dyn} + P_{leak} = V_{DD}I_{DD} + V_{DD}(I_{leak} + I_{sc}) = \alpha C_{sw}V_{DD}^2 f_{sw} + V_{DD}(I_{leak} + I_{sc}) \quad (2.10)$$

where  $I_{DD}$  is the total current drawn from the supply. If the voltage swing across the switched capacitance is less than the supply voltage, the dynamic power, in general, is given as

$$P_{dyn} = \alpha C_{sw} V_{DD} V_{swing} f_{sw} \tag{2.11}$$

Combining Eqs. 2.1, 2.5, 2.7 and 2.8, we get the CMOS power expressions in terms of the supply voltage as

$$P_{dyn,sat} \propto \alpha C_{sw} V_{DD} \left( V_{DD} - V_{TH} \right)^{\alpha_{mos}} \tag{2.12}$$

$$P_{dyn,sub} \propto \alpha C_{sw} V_{DD} e^{\frac{V_{DD} - V_{TH}}{mV_T}}$$

(2.13)

$$P_{leak} \propto V_{DD} e^{-\frac{V_{TH}}{mV_T}} \tag{2.14}$$

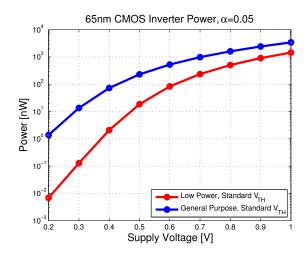

Fig. 2.4 shows the power as a function of supply voltage for two different flavors of inverters in a 65nm CMOS process. As seen in Eq. 2.10, the average power is dependent on the value of the switched capacitance, the switching rate of the output node, the leakage current and the supply voltage.

Figure 2.4: CMOS inverter power as a function of  $V_{DD}$ .

#### 2.1.4 Energy

The average power is a very important metric, providing insight into how much average current a power source needs to provide a logic gate. Of interest as well is the time integral of the average power over the duration of an operation, or the energy per operation,  $E_{OP}$ . The energy required to complete a set of meaningful logic operations typically determines the amount of energy an energy source must be able to provide before it needs to be replenished.

Thus, for a given time needed to complete an operation,  $T_{OP}$ , the energy per operation is defined as

$$E_{OP} = P_{ave}T_{OP} = (P_{dyn} + P_{leak})T_{OP} = P_{dyn}D + P_{leak}T_{OP}$$

(2.15)

The dynamic component of the average power is multiplied only by the delay of the gate since  $I_{ON}$  is zero after the output switches. Combining Eqs. 2.10 and 2.15, and ignoring the short-circuit current, we get

$$E_{OP} = C_{sw} V_{DD}^2 f_{sw} D + V_{DD} I_{leak} T_{OP} = \alpha C_{sw} V_{DD}^2 + V_{DD} I_{leak} T_{OP}$$

(2.16)

For the simple case when the logic gate's output switches only once per operation, or  $D = \alpha T_{OP}$ , the energy per operation can be expressed as

$$E_{OP} = E_{dyn} + E_{leak} = \alpha C_{sw} V_{DD}^2 + \frac{V_{DD} I_{leak} D}{\alpha}$$

(2.17)

Again, if the voltage swing across the switched capacitance is less than the supply voltage, the dynamic energy, in general, is given as

Figure 2.5: CMOS inverter energy per operation as a function of  $V_{DD}$ .

$$E_{dyn} = \alpha C_{sw} V_{DD} V_{swing} \tag{2.18}$$

Combining Eqs. 2.5, 2.7 and 2.8, we can express the leakage energy as

$$E_{leak,sat} \propto \frac{V_{DD}^2}{\alpha} \frac{e^{-\frac{V_{TH}}{mV_T}}}{\left(V_{DD} - V_{TH}\right)^{\alpha_{mos}}}$$

(2.19)

$$E_{leak,sub} \propto \frac{V_{DD}^2}{\alpha} e^{-\frac{V_{DD}}{mV_T}}$$

(2.20)

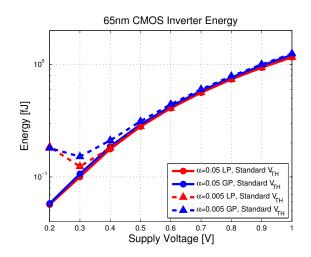

Thus, a lower activity factor decreases the dynamic energy component, but at the same time increases the effect of the static or leakage energy component, as shown in Fig. 2.5 for two versions of a 65nm CMOS inverter, and for two different activity factors. For  $\alpha = 0.005$ , the total energy is dominated by the leakage energy component, which is proportional to the delay as seen in Eq. 2.17.

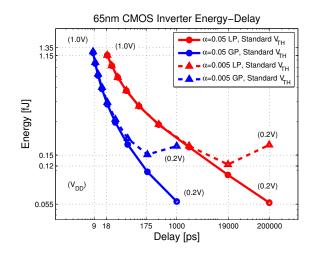

The tradeoff between energy and delay or performance can be visualized in a more compact manner by combining the Figs. 2.3 and 2.5, with the supply voltage as a swept parameter. Thus, the energy-delay plot of the two 65nm CMOS inverters, in Fig. 2.6, shows the effect of changing the supply voltage, simultaneously on both the inverter energy and delay.

### 2.2 A Sampling of Low Energy Design Techniques

As seen in Eq. 2.17, the dynamic energy per operation of CMOS gates can be reduced if (1) the effective switched capacitance,  $\alpha C_{sw}$ , is lowered, (2) the voltage swing is lowered and/or (3) the supply voltage is lowered.

Figure 2.6: The energy-delay plot of the 65nm CMOS inverters.

The effective switched capacitance of a circuit or system can be reduced by lowering the switching activity,  $\alpha$ . One way of reducing  $\alpha$  is by preventing unnecessary transitions in the clock network by gating the clock [WPW00]. Another way of reducing the switching activity is to create circuit elements such as flip-flops that sense if the incoming data is different from the stored data [KKJ01] [HTH<sup>+</sup>99]. These conditional flip-flop evaluation methods can prevent unnecessary transitions within the flip-flop itself at the expense of the additional circuitry needed to detect these differences.

Reducing the supply voltage seems to be the best way to reduce power and energy [CB95] [DC97] due to their quadratic dependence on  $V_{DD}$ . However, due to the increased gate delays, circuit performance must be traded off for reduced power and/or energy [LS93]. This tradeoff can be made more fine-grained and flexible by using variable and/or multiple (1) supply voltages to reduce energy and (2) threshold voltages to reduce the delay penalty incurred by reducing  $V_{DD}$  [KSM<sup>+</sup>98] [Kur02] [DC97] [CC06]. Reduced output-swing circuits such as pass transistors [SKK97] or bus drivers [NII<sup>+</sup>93] can also be selectively used to drive nodes with relatively large capacitances, thus allowing more fine-tuned voltage control over individual circuit nodes rather than groups of gates.

This increased flexibility is accompanied by additional overhead costs, such as voltage level converters, increased design complexity and the cost of generating and routing the various supply and threshold voltages that are required. Thus in order to minimize energy, optimal combinations of the supply and threshold voltage have been reported [Sta01], most often leading to subthreshold operation [WC05].

In order to understand how much more energy reductions can potentially be achieved, it is important to determine if theoretical limits on  $E_{OP}$  exists, and if these limits exist, can logic gates can operate near these limits or are there barriers preventing current logic circuits from operating close to these limits.

Figure 2.7: Theoretical energy and voltage limits.

### 2.3 Fundamental Limits

In order to discriminate between two binary states, the transfer characteristic of an inverter must have a slope, m, where |m| > 1 [MD00]. This leads to the minimum allowable CMOS supply voltage of

$$V_{DD,\lim} \cong 2V_T \ln\left(2 + \frac{C_d}{C_{ox}}\right) = 2V_T \ln\left(1 + \frac{S_S}{(\ln 10) V_T}\right) \cong 2(\ln 2) V_T \approx 36 \, mV$$

(2.21)

This minimum allowable supply voltage,  $V_{DD,lim}$ , gives the minimum energy,  $E_{OP,lim}$ , needed to move a single electron in order to charge the gate capacitance of a MOSFET, resulting in [MD00] [ZBSF05]

$$E_{OP,\text{lim}} = (\ln 2) \, kT \approx 2.87 \times 10^{-21} \, J \tag{2.22}$$

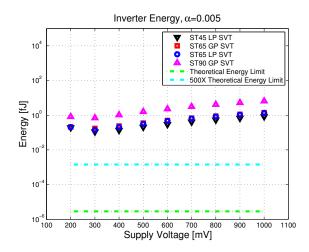

Fig. 2.7 shows the relative simulated values of minimum energies and voltages of various CMOS inverter technologies, as compared to  $E_{OP,\text{lim}}$ . In current technologies, the inverter switching energies are approximately five orders of magnitude larger than the theoretical limit.

Eqs. 2.21 and 2.22 assume ideal and perfectly matched transistors. Other factors can significantly limit the minimum achievable supply voltage and energy. Most notable are (1) the increased device variability and mismatch [TBK<sup>+</sup>10] that can affect the functionality of the circuit and (2) the increased subthreshold leakage energy components [ITR] that increases the minimum energy that can be achieved.

Although device noise sources such as shot noise, flicker noise and thermal noise can still be considered negligible in digital circuits, external noise sources such as (1) crosstalk, (2) power/ground bounce and (3) substrate noise can significantly degrade the performance and the reliability of digital integrated circuits [NRC08]. These external noise sources can also limit the reduction of  $V_{DD}$  [BS99], but is outside the scope of this work.

#### 2.3.1 Variability

Variability arises due to the fact that devices are scaling faster than the manufacturing technology's ability to control the process parameters, resulting in (1) random atomic-level differences between devices and (2) systematic shifts in manufacturing dependent process conditions [BFG<sup>+</sup>06]. In MOS transistors, variability significantly affects the channel width and length as well as the threshold voltage [UTB<sup>+</sup>06]. At low voltages, variability can cause (1) logic failure, (2) the inability of an SRAM cell to retain its state, (3) reduced noise margins, (4) increased soft-error failures, (5) exponential degradation of performance and (6) increased subthreshold leakage current [TBK<sup>+</sup>10] [PdGT04].

Circuit and architectural approaches to reduce the impact of variability have been reported, such as (1) the use of more stringent design rules and regular circuit layout techniques [KRH+05] [CCL+08] [PN09], (2) variability-aware device sizing [VCT+04], and (3) systems that employ error detection and/or correction blocks that can allow aggressive clocking or voltage scaling [DRL+06] [BTK+09] [Mit10] [TBW+09].

Thus, in order to assure correct functionality in the presence of process variations, additional energy is needed to support these circuit and architectural techniques. This additional energy then raises the minimum energy required to complete an operation.

#### 2.3.2 Subthreshold Leakage

The most effective way of reducing the dynamic energy per operation of digital circuits is by reducing the supply voltage,  $V_{DD}$ . This however, comes at the expense of increased leakage or standby energy per operation due to the required threshold voltage reduction needed to achieve a given performance goal [Sak03]. This energy wall due to standby energy is now considered a clear long-term threat to the survival of CMOS technology itself, and its management a major challenge [ITR].

Standby energy is commonly dominated by subthreshold leakage currents [KAB<sup>+</sup>03], which flow in circuits that provide gain, by virtue of their power rail connections. In static complementary CMOS logic, each gate is essentially a gain stage, with a  $V_{DD}$  and ground connection, giving each gate (1) signal regeneration, (2) current drive and also (3) a leakage path. Thus, the functionality of the gate is tightly coupled to its gain, and hence to leakage.

Figure 2.8: A NAND4 gate implemented using (a) a single gate and (b) multiple gates.

Subthreshold leakage current can thus be reduced (1) by increasing the effective channel length,  $L_{eff}$ , (2) by reducing the supply voltage and consequently the drain-to-source voltage,  $V_{DS}$  or (3) by increasing the threshold voltage,  $V_{TH}$ .

Device-level leakage reduction techniques have been reported, such as multiple threshold voltages (MTCMOS) [MDM<sup>+</sup>95] [CHC04], as well as the use of non-CMOS devices such as integrated relays [CFK<sup>+</sup>10]. Circuit-level techniques that exist in literature include the use of boosted-gate MOS (BGMOS) transistors [ITN<sup>+</sup>00], super cut-off CMOS (SCCMOS) devices [KNS98] and multi-voltage CMOS (MVCMOS) techniques [Sta98].

A sampling of other currently used low leakage circuit techniques aside from voltage scaling include the use of (1) non-minimum channel lengths; (2) stacked transistors and (3) various header and footer switch topologies and are summarized in [KNC02], [CSH<sup>+</sup>03] and [Sak03].

Increasing the transistor channel length reduces leakage by increasing the effective resistance of the leakage path between the supply rails, resulting in delay penalties. Using reverse body bias to increase  $V_{TH}$  also leads to the same results, however due to increased channel doping [Yu04], BTBT limits the effectiveness of body bias to reduce leakage, and hence the effective power reduction is reduced by approximately 4X per technology generation [KNB+99].

As seen in Fig. 2.6, the leakage energy component prevents further reductions in energy and thus, determines the minimum  $E_{OP}$  that can be achieved, which is still several orders of magnitude larger than the theoretical limit in Eq. 2.22. By applying the leakage reduction techniques described above, circuit operation closer to  $E_{OP,\text{lim}}$  can be obtained.

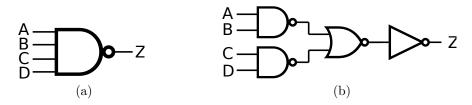

### 2.4 Leakage and Gain

Another way to reduce leakage current is to use more complex gates. By combining more functionality in a single gate, less gates are used resulting in less leakage paths from  $V_{DD}$  to ground. Again, this would increase the effective resistance of the leakage path from the supply rails. However, using fewer, more complex gates reduces the amount of gain present in the circuit. Fig. 2.8 shows two different implementations of a NAND4 gate: (1) using a single complex gate, and hence a single gain stage, as seen in Fig. 2.8a, and (2) using multiple gates (gain stages) shown in Fig. 2.8b.

Figure 2.9: The CMOS NAND4 gate: (a) energy-delay characteristics and (b) details at high supply voltages.

The energy and delay characteristics of both NAND4 gates as the supply voltage is swept from 0.2 V to 1 V is given in Fig. 2.9. As expected, at high supply voltages near 1 V, the NAND4 implemented using more gain stages can drive the output load faster than the one implemented using a single gate. However, this performance improvement costs more energy. Note that at lower supply voltages, the single, more complex gate consumes less energy due to a smaller effective switched capacitance. At lower activity factors, the leakage energy component is also less due to the fact that it has fewer leakage current paths. Thus, in cases where performance is less critical than energy consumption, using circuits with a reduced number of gain elements may allow lower energy operation than just scaling down the supply voltage of a topology optimized for speed.

### 2.5 Summary

Lowering the supply voltage has been the most effective method of lowering the energy per operation of CMOS logic gates. However, due to increased variability and standby energy caused by subthreshold leakage currents, the effectiveness of voltage scaling has diminished to the point where further reductions in supply voltage can lead to incorrect operation or an increase the total energy per operation instead of a reduction. Thus, various variability mitigation and leakage current reduction techniques have been reported, in an effort to bring the voltage and energy levels as close as possible to their theoretical minimum values. Though noise and variability are important issues that must be considered carefully, the focus of this work, however will be on the reduction of subthreshold leakage current. Also, since most noise and variability mitigation circuits also introduce additional leakage themselves, the resulting overall leakage current determines the minimum energy per operation that can be achieved.

One key idea presented in this chapter is that due to the inherent gain in static CMOS gates, the subthreshold leakage current and the output drive current share the same path through the logic gate. Thus, most circuit-level leakage reduction techniques must trade-off the amount of leakage reduction to the amount of drive current needed by the system, therefore limiting the leakage current reduction that can be achieved. Chapter 3 shows how pass transistor circuits, by decoupling gain and logic functionality, can change this trade-off.

## Chapter 3

## Pass Transistor Logic

Pass transistor logic (PTL) has been the focus of many research projects [Tak98] ranging from their use as static CMOS replacement circuits for specialized applications, to computer-aided design (CAD) methodologies that take advantage of various PTL characteristics such as area efficiency and regularity [YYN<sup>+</sup>90]. In this chapter, a sampling of various pass transistor logic implementations are described, with the intention of highlighting the relationship between logic functionality, gain stages, performance and energy.

## 3.1 Basic PTL Topologies

Various pass transistor logic implementations have been reported and can be broadly grouped into two classes based on the pass transistor network (PTN) used: (1) NMOS-only PTNs and (2) PTNs that use both NMOS and PMOS transistors [MNO00]. NMOS-only pass transistor networks are less complex, resulting in (1) lower input and signal path capacitances and (2) smaller area. However, due to the threshold voltage drop needed to keep the NMOS network conducting, the high or logic '1' output voltage will be less than the supply voltage,  $V_{DD}$ . In order to recover a rail-to-rail output swing, a simple inverter or buffer can be added at the output of the PTN.

One common form of the NMOS-only PTL topology is the complementary pass transistor logic (CPL) [YYN<sup>+</sup>90]. CPL has complementary inputs and outputs, and usually has CMOS inverters at its outputs to restore the degraded PTL voltage swing due to the NMOS threshold voltage ( $V_{TH}$ ) drop. Fig. 3.1b shows a CPL implementation of an OR/NOR gate. A number of arithmetic building blocks have been reported using CPL [YYN<sup>+</sup>90, AKBE96, CSB<sup>+</sup>97], taking advantage of the low input capacitance and reduced transistor count to increase performance.

A variation of CPL is the double pass transistor logic (DPL) [SOS<sup>+</sup>93, CSB<sup>+</sup>97]. It is composed of an NMOS PTN and its PMOS equivalent, as shown in Fig. 3.1c. The additional

Figure 3.1: OR/NOR implementations in (a) CMOS, (b) CPL, (c) DPL and (d) DVL.

PMOS PTN (1) doubles the signal transmission path, compensating for the performance degradation due to increased path capacitance and (2) allows full swing at the output of the PTN, improving the performance at low supply voltage even with limited threshold voltage scaling. DPL however, has increased input capacitance due to the redundant signal paths present.

Dual value logic (DVL) [OD95, OD97], shown in Fig. 3.1d, is a pass transistor-based logic style derived from DPL by eliminating redundant and slower branches while still maintaining full-rail voltage swing at the output of the PTN. Note that since DPL and DVL circuits use both NMOS and PMOS PTNs, no buffering or voltage swing restoration circuitry is required at their outputs.

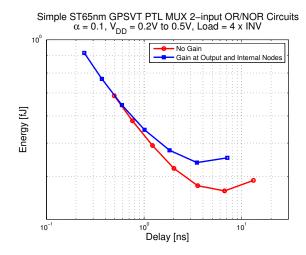

The energy-delay characteristics of 65nm two-input CPL, DPL and DVL OR/NOR PTL gates, as well as the equivalent static CMOS gate (Fig. 3.1a) are shown in Fig 3.1, for two different activity factors,  $\alpha = 0.1$  and  $\alpha = 0.01$  and for two different capacitive loads. All the inputs to these gates are driven by a minimum-sized inverter. Two versions of the CPL are presented, one with and one without an inverter at the output. The energy numbers include the energy of the driving gates since without these gates, the CPL without inverters at the output, being completely passive, would consume no energy from the supply rails. The supply voltage,  $V_{DD}$  is swept from 200 mV to 500 mV and the PTL gate outputs are terminated with equal load capacitances.

Figure 3.2: PTL 2-input OR/NOR energy-delay characteristics: (a)  $\alpha = 0.1$  and loaded with a 1X INV, (b)  $\alpha = 0.01$  and loaded with a 1X INV, (c)  $\alpha = 0.1$  and loaded with a 4X INV and (d)  $\alpha = 0.01$  and loaded with a 4X INV.

As expected, at very low performance, leakage energy due to the gain stages dominates, and is smallest in the CPL circuit without inverters, i.e., the circuit with the least number of supply rail connections, as shown in Fig. 3.2a. This leakage energy becomes more prominent at lower activity factors (Fig. 3.2b).

Gain, however, plays a very important role in driving larger capacitive loads. Figs. 3.2c and 3.2d shows how an increase in fan-out adversely affects the energy-delay characteristics of circuits without gain. Without gain, the PTL circuits incur significant increases in delay, resulting in a corresponding increase in energy. The inherent gain, and thus drive current of the static CMOS gate, on the other hand, reduces the delay impact of increasing the load capacitance. This smaller delay results in a lower overall energy for high fanout situations.

For low to moderate performance, reducing the amount of gain could lead to a reduction in

Figure 3.3: The pass transistor multiplexer tree (a) with  $N_{depth} = 2$  and (b) a sneak path.

energy. In static CMOS circuits, gain can be lowered by increasing the complexity of a gate, while in PTL circuits, gain elements have to be explicitly added.

### 3.2 PTL Operation and Circuit Gain

The NMOS-only CPL circuit is purely passive and therefore, does not regenerate the input through gain elements such as inverters or pull-up/pull-down circuitry. This particular topology is of interest since (1) there are no supply rail connections, (2) functionality is achieved without gain and (3) energy is consumed solely through the gain elements and dissipated mostly by the pass transistor network.

#### 3.2.1 Leakage in PTL Circuits

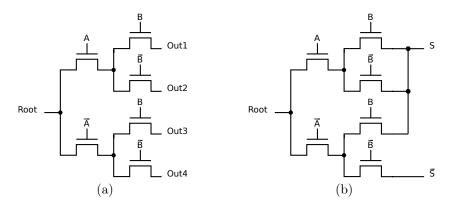

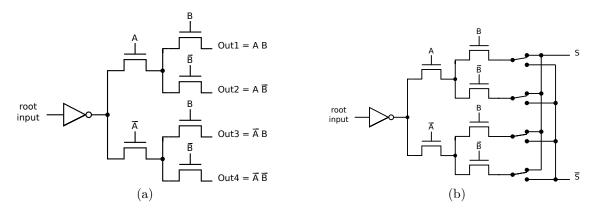

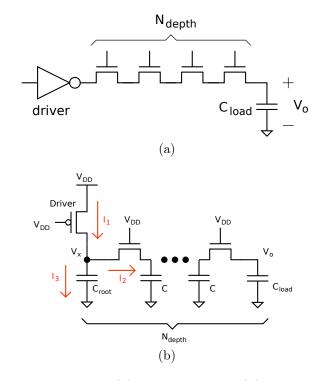

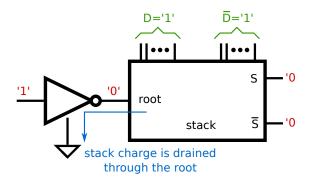

The fact that there are no supply rail connections implies that there are no inherent subthreshold leakage paths from  $V_{DD}$  to ground. Consider a simple CPL-based multiplexer PTN shown in Fig. 3.3a, which is a commonly used PTN topology, due to the fact that any logic function can be expanded into multiplexer functions using Shannon's expansion [Sha49].

Leakage currents can, however, still flow via sneak paths, one of which is shown in Fig. 3.3b. These paths form when two mutually exclusive inputs of a pass transistor network have opposite polarities. This behavior is similar to a static CMOS inverter, where leakage current flows through the transistor in the OFF state. The depth of the multiplexer tree,  $N_{depth}$ , increases as the number of inputs and leads to an exponential increase in the number of potential leakage paths.

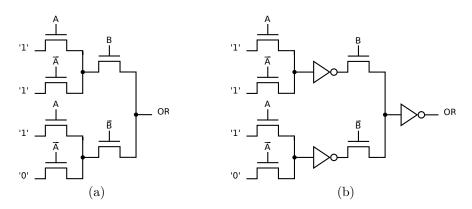

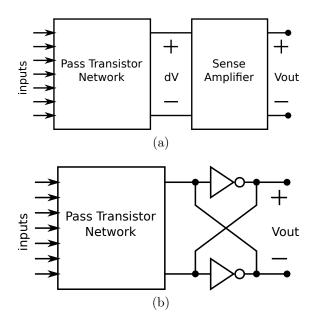

Figure 3.4: A pass transistor network (a) with no gain elements and (b) with gain at the output and internal nodes.

#### 3.2.2 The Effect of Adding Gain

Unlike static complementary CMOS logic, the PTL logic network that determines functionality is decoupled from gain, allowing the selective addition or removal of gain elements as needed. Fig. 3.4a shows a pass transistor multiplexer tree-based OR gate without gain elements added, while Fig. 3.4b shows the same circuit but with additional gain added internally and at the output.