# Design of a system for cm-range wireless communication

Simone Gambini Jan M. Rabaey Elad Alon

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2009-184 http://www.eecs.berkeley.edu/Pubs/TechRpts/2009/EECS-2009-184.html

December 18, 2009

Copyright © 2009, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Design of a system for cm-range wireless communications

by

Simone Gambini

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Electrical Engineeing and Computer Sciences

in the

### GRADUATE DIVISION

of the

### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Jan Rabey, Chair Professor Elad Alon Professor Paul K. Wright

Fall 2009

The dissertation of Simone Gambini is approved.

Chair

Date

Date

Date

University of California, Berkeley Fall 2009 Design of a system for cm-range wireless communications

Copyright © 2009

by

Simone Gambini

#### Abstract

Design of a system for cm-range wireless communications

by

Simone Gambini

Doctor of Philosophy in Electrical Engineeing and Computer Sciences

University of California, Berkeley

Professor Jan Rabey, Chair

The continuous growth in the number of mobile phone subscribers, which exceeded 3 billions by 2007, and of the number of wireless devices and systems, led to visions of a near future in which wireless technology is so ubiquitous that *1000 Radios* per person will exist. In this context, ad-hoc area networks between several consumer electronic devices located within a meter of each other will be necessary in order to reduce traffic towards the base station and reduce power consumption and interference generation. As existing air interfaces still both radiate and dissipate an order of magnitude higher power than what this future scenario requires, a new, low-power radio technology must be developed. In this thesis, we develop a low-power transceiver with range of a few centimeters targeted to mobile-mobile data exchange. The same transceiver could also be employed in some implanted applications, as well as in distributed industrial control environments.

The design of the air-interface for this cm-range communication system at the propagation, system and circuit levels. First, we describe an optimization methodology that enables the designer to choose, for any given antenna design, which carrier frequency results in the maximum receiver Signal-To-Noise-Ratio (SNR). We then show how by using impulse-radio signaling, the chosen high-SNR channel can be leveraged to simplify the radio receiver architecture to the simplest possible RF receiver-consisting only of an RF rectifier. To mitigate the known issues of sensitivity to interference for these rectifier-based receivers, a technique to improve selectivity that uses only baseband processing and requires no RF prefilter is introduced.

These techniques are demostrated by a transceiver test chip, implemented in a 65nm CMOS process . The transceiver dissipates  $250\mu W$  in receive mode, and  $25\mu W$  in transmit mode when operating at 1Mbps , and it integrates a timing-recovery loop that achieves jitter lower than 2nS while consuming  $45\mu W$ . This figures correspond to

an energy per bit of 300pJ, which compares favorably with current state-of-the art.

Professor Jan Rabey Dissertation Committee Chair To my mother Silvia, my brother Francesco and my father Diego.

If I have seen a little further it is by standing on the shoulders of Giants I.Newton

## Contents

| Li                                                                                 | ist of Figures vi |        |                                                                                                |      |  |  |

|------------------------------------------------------------------------------------|-------------------|--------|------------------------------------------------------------------------------------------------|------|--|--|

| $\mathbf{Li}$                                                                      | st of             | Tables | 5                                                                                              | xii  |  |  |

| A                                                                                  | cknov             | wledge | ments                                                                                          | xiii |  |  |

| 1 1000 Radios per Person And the Case for Ad-Hoc Networking                        |                   |        |                                                                                                |      |  |  |

|                                                                                    | 1.1               | Short  | range wireless systems today                                                                   | 4    |  |  |

|                                                                                    |                   | 1.1.1  | Commercially available, low-power <i>short range</i> bi-directional commu-<br>nication devices | 4    |  |  |

| 1.1.2 Bi-directional, narrowband short range radios resulting from academic papers |                   |        |                                                                                                |      |  |  |

| 1.1.3 Impulse Ultra-wideband radios resulting from a<br>cademic papers             |                   |        |                                                                                                |      |  |  |

|                                                                                    |                   | 1.1.4  | Other short-range, low energy communication systems $\ldots \ldots \ldots$                     | 7    |  |  |

|                                                                                    | 1.2               | Thesis | structure                                                                                      | 8    |  |  |

| <b>2</b>                                                                           | Linl              | k Marg | gin Modeling for cm-range radios                                                               | 9    |  |  |

|                                                                                    | 2.1               | Improv | ving path loss modeling                                                                        | 10   |  |  |

|                                                                                    |                   | 2.1.1  | Electromagnetic wave propagation at short range                                                | 10   |  |  |

|                                                                                    |                   | 2.1.2  | Magnetic Coupling                                                                              | 15   |  |  |

|                                                                                    |                   | 2.1.3  | Model Verification                                                                             | 16   |  |  |

|                                                                                    |                   | 2.1.4  | Comparison with power transfer $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 23   |  |  |

|                                                                                    |                   | 2.1.5  | Chosen design point and channel measurements with cm-scale antennas                            | 24   |  |  |

|                                                                                    |                   | 2.1.6  | Channel impulse response                                                                       | 24   |  |  |

|                                                                                    | 2.2               | Anten  | na Design for a 3-10GHz wideband system                                                        | 25   |  |  |

|                                                                                    |                   | 2.2.1  | Slotted Bowtie Antenna Design                                                                  | 27   |  |  |

|          |      | 2.2.2 Monopole antenna design                                              | 30        |

|----------|------|----------------------------------------------------------------------------|-----------|

|          | 2.3  | Conclusions                                                                | 31        |

| 3        | Low  | Power RF System Design for a cm-range Transceiver                          | <b>34</b> |

|          | 3.1  | Radio Dynamic Range-Power Tradeoff                                         | 34        |

|          |      | 3.1.1 Overhead power components                                            | 36        |

|          |      | 3.1.2 Summary                                                              | 38        |

|          | 3.2  | Effect of duty-cycling on power dissipation                                | 39        |

|          |      | 3.2.1 Overhead Costs in duty-cycled systems                                | 41        |

|          |      | 3.2.2 Duty cycling optimization                                            | 41        |

|          |      | 3.2.3 Inherent Asymmetry of duty-cycled systems                            | 44        |

|          |      | 3.2.4 Power consumption of VCO and baseband: a more critical look $\ldots$ | 44        |

|          | 3.3  | Radio Architecture Design                                                  | 45        |

|          |      | 3.3.1 Technological Constraints                                            | 46        |

|          |      | 3.3.2 Transmitter section and link budget                                  | 46        |

|          |      | 3.3.3 Receiver section                                                     | 47        |

|          | 3.4  | Conclusions                                                                | 51        |

| 4        | Bas  | eband and Timer Subsystem Design                                           | 53        |

|          | 4.1  | Baseband architectures for UWB systems                                     | 53        |

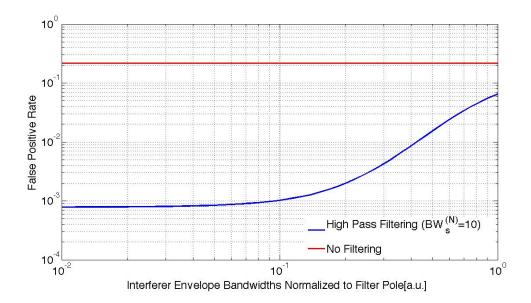

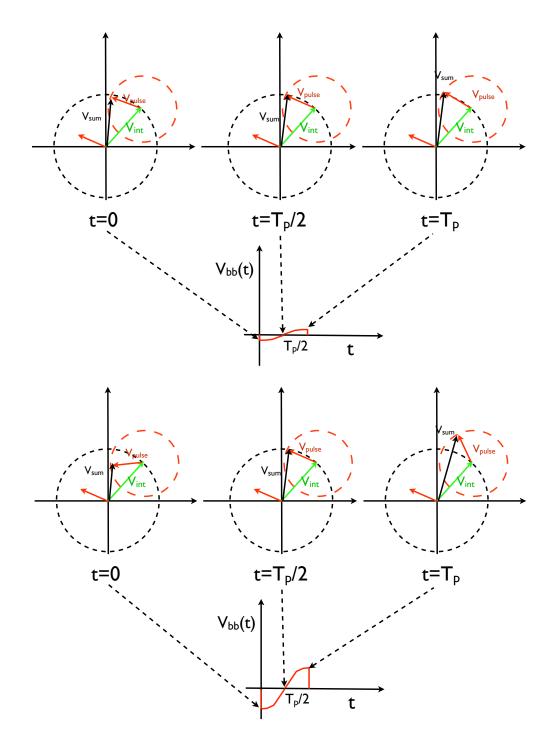

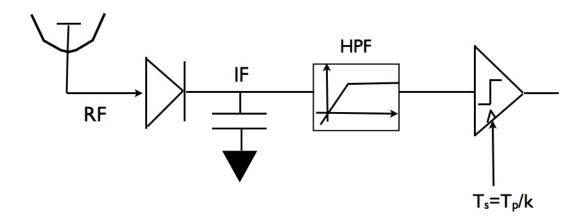

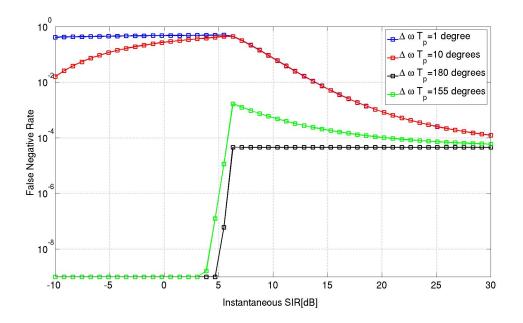

|          | 4.2  | Improving Interferer Performance in Self-Mixing Radios                     | 55        |

|          | 4.3  | Synchronizer and modulation scheme design                                  | 66        |

|          | 4.4  | Summary                                                                    | 76        |

| <b>5</b> | Circ | cuit Design                                                                | 78        |

|          | 5.1  | Introduction                                                               | 78        |

|          | 5.2  | Transmitter Circuits                                                       | 79        |

|          |      | 5.2.1 Architecture selection                                               | 79        |

|          |      | 5.2.2 Oscillator                                                           | 81        |

|          |      | 5.2.3 Divider                                                              | 83        |

|          |      | 5.2.4 PSK Modulator and Driver                                             | 85        |

|          | 5.3  | Receiver Circuits                                                          | 88        |

|          |      | 5.3.1 Matching network/duplexer                                            | 88        |

|              |     | 5.3.2  | Reconfigurable mixer/diode                       |

|--------------|-----|--------|--------------------------------------------------|

|              |     | 5.3.3  | Baseband Filter                                  |

|              |     | 5.3.4  | Comparators                                      |

|              |     | 5.3.5  | Layout and summary                               |

|              |     | 5.3.6  | Bias Circuits and power gating strategy 107      |

|              | 5.4 | Timir  | ng Circuits                                      |

|              |     | 5.4.1  | Baseband oscillator                              |

|              |     | 5.4.2  | Baseband divider and comparator                  |

|              |     | 5.4.3  | Pulse detection and retiming logic               |

|              |     | 5.4.4  | Controller                                       |

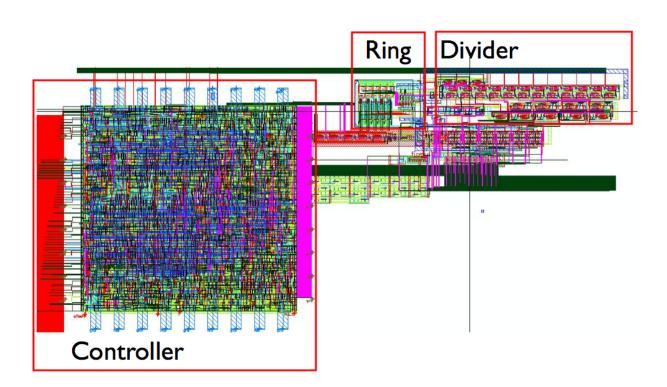

|              |     | 5.4.5  | Block Layout and summary 116                     |

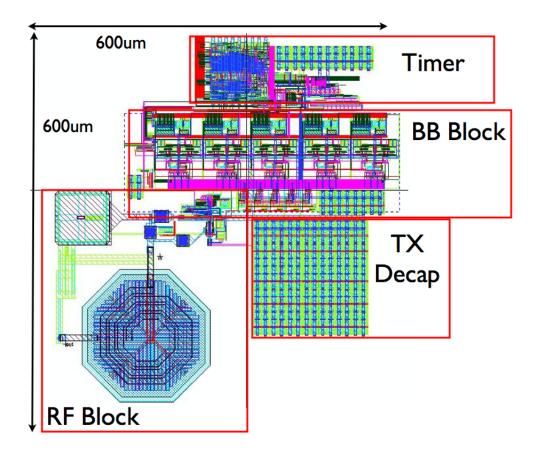

|              | 5.5 | System | n Layout and summary 116                         |

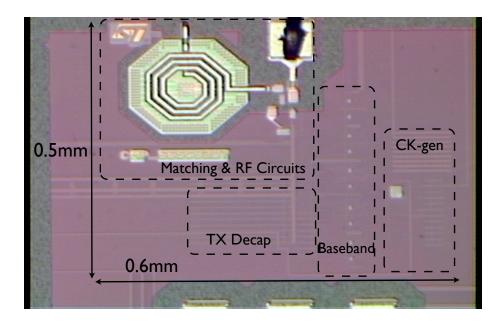

| 6            | Mea | asurem | ent Results 121                                  |

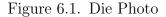

|              | 6.1 | FIB Is | sue                                              |

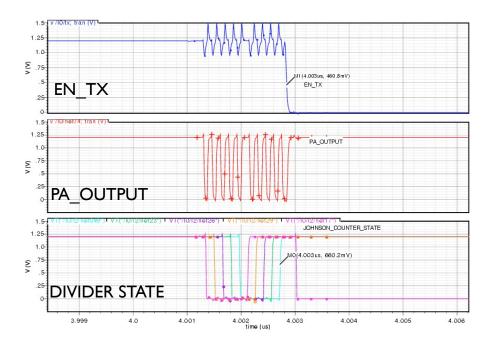

|              | 6.2 | Transr | nitter measurements                              |

|              | 6.3 |        | er Measurements                                  |

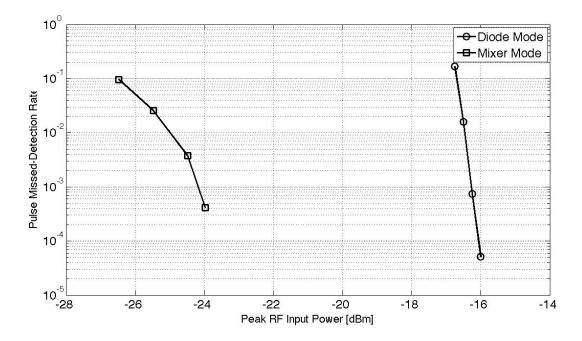

|              |     | 6.3.1  | Sensitivity Measurements                         |

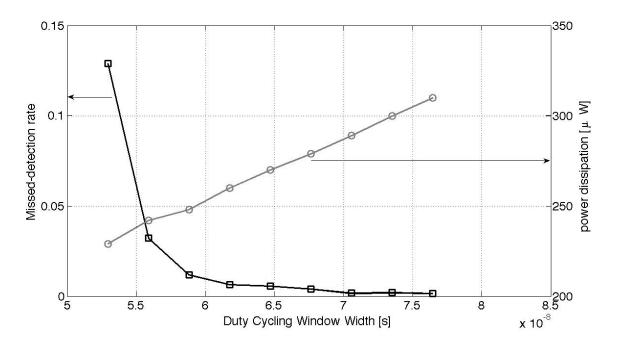

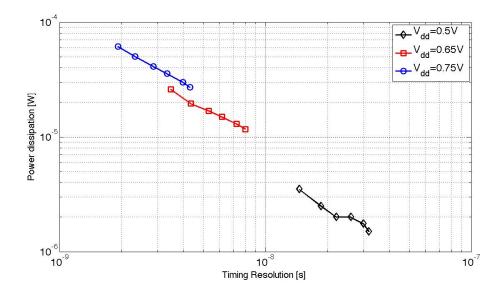

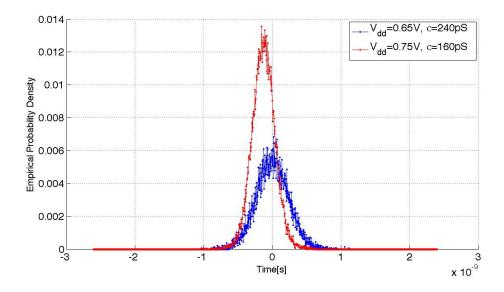

|              |     | 6.3.2  | Duty-cycled Measurements                         |

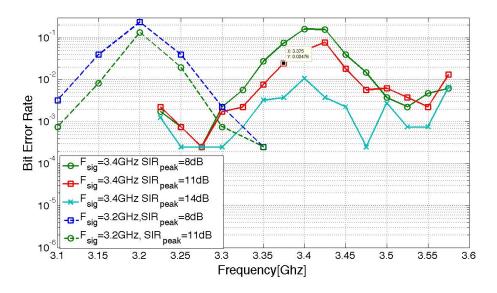

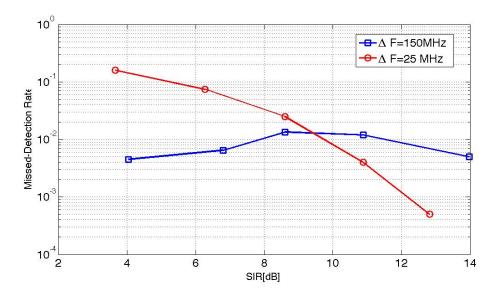

|              |     | 6.3.3  | Interference Rejection Measurements              |

|              |     | 6.3.4  | Wireless Tests                                   |

|              |     | 6.3.5  | Receiver Performance Summary                     |

|              |     | 6.3.6  | Comparison with prior art                        |

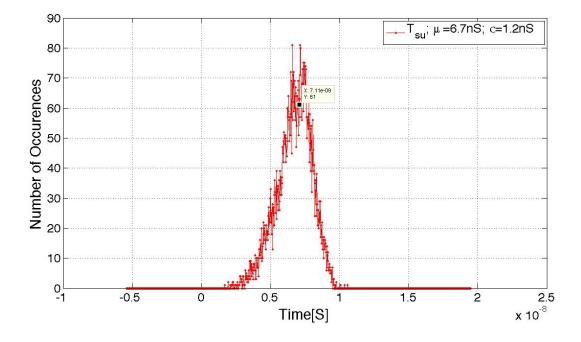

|              | 6.4 |        | Measurements                                     |

| 7            | Con | clusio | ns 142                                           |

| •            | 7.1 |        | ch Directions                                    |

|              | 1.1 | 7.1.1  | Power-efficient TCM for wireless sensor networks |

|              |     | 7.1.2  | Circuit Implementation                           |

|              |     | (.1.2  | Circuit implementation                           |

| $\mathbf{A}$ | Mat | ching  | Network Impedance Calculations 144               |

|              | A.1 | Receiv | er Side Impedance                                |

|              | A.2 | Transr | nit Side Impedance                               |

### **B** Statistical Jitter Transfer Analysis

# List of Figures

| 1.1  | Pushpin nodes, a first implementation of the paintable computing concept [66]. Approximate node size is $3.24cm^2$           | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Schematic of electrical dipoles and frame of reference                                                                       | 10 |

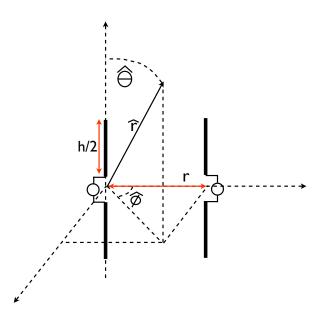

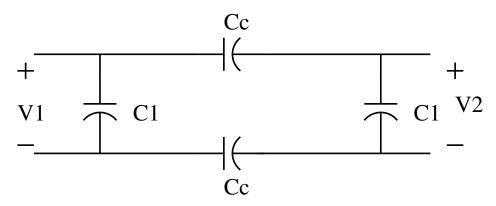

| 2.2  | Equivalent circuit for monopoles in the near-field operating range $\ldots$ .                                                | 13 |

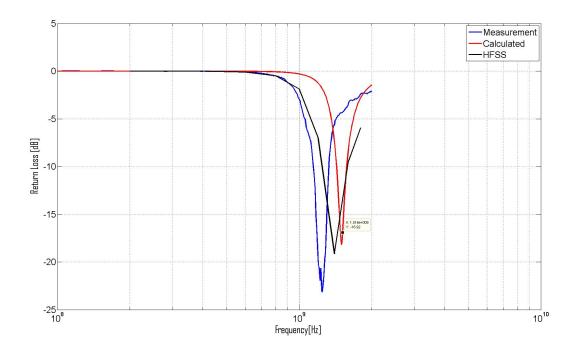

| 2.3  | Measured, calculated and simulated return loss for wire monopoles                                                            | 17 |

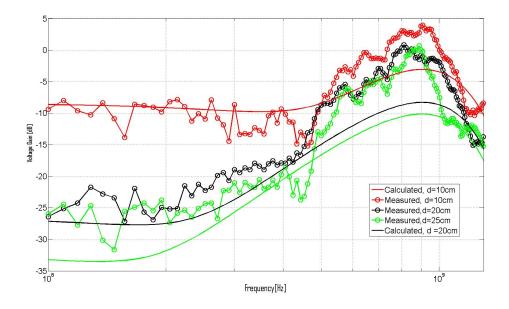

| 2.4  | Calculated and measured path loss as a function of frequency                                                                 | 17 |

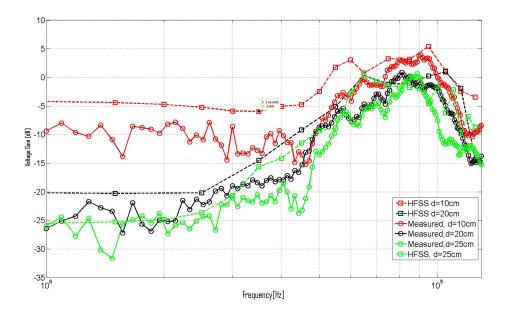

| 2.5  | Measured and simulated path loss as a function of frequency $\ldots$                                                         | 18 |

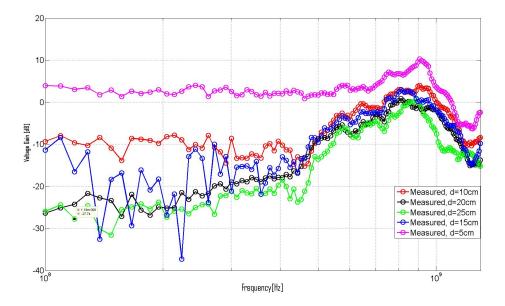

| 2.6  | Measured path loss (including matching network) for the TX-RX Antenna pair at different separations                          | 18 |

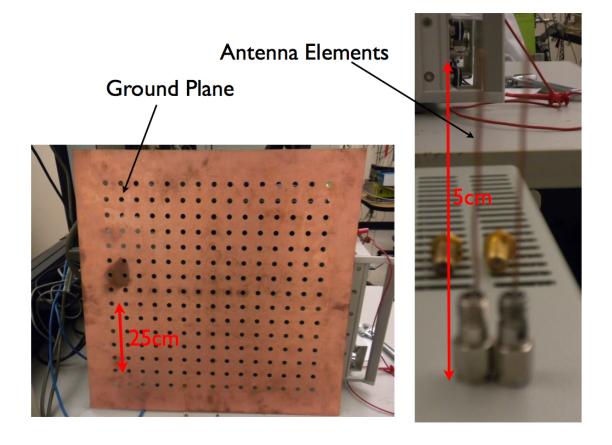

| 2.7  | Experimental setup in the BWRC Lab                                                                                           | 19 |

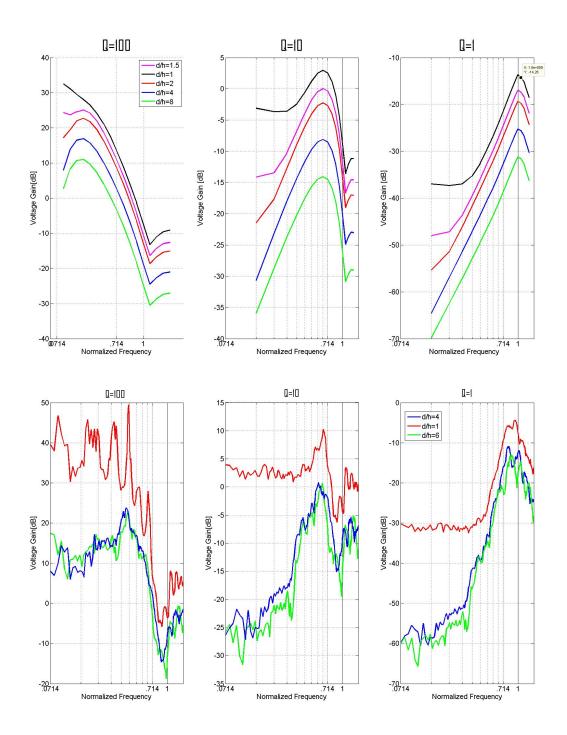

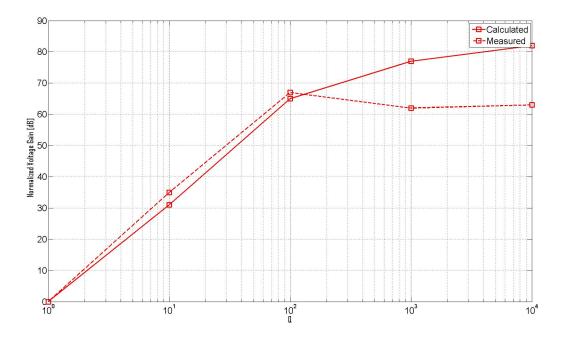

| 2.8  | Calculated(top) and measured(bottom) loss as a function of frequency for different antennas separations and quality factors  | 20 |

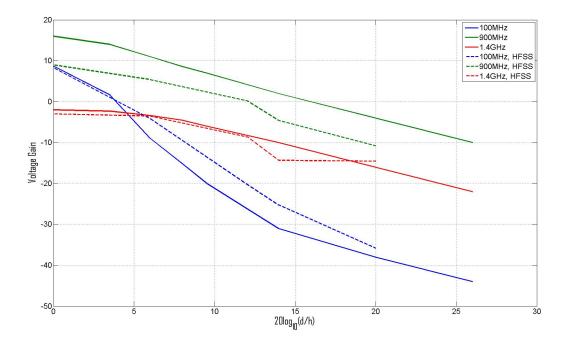

| 2.9  | Effect of matching network quality factor on voltage gain $\ldots \ldots \ldots \ldots$                                      | 21 |

| 2.10 | Measured and simulated path loss as a function of range for different frequencies                                            | 21 |

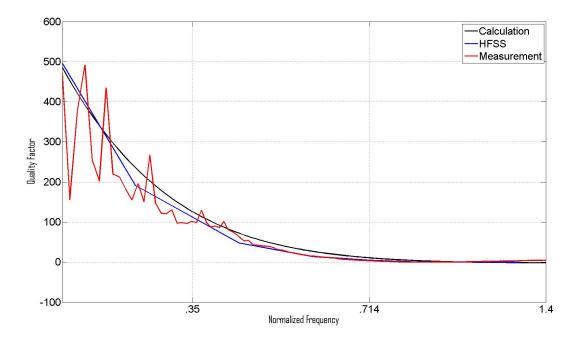

| 2.11 | Antenna impedance quality factor as a function of frequency $\ldots \ldots \ldots$                                           | 22 |

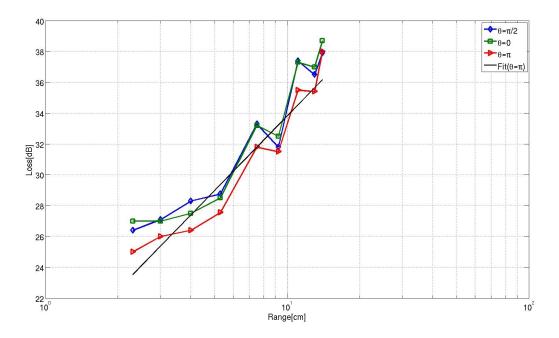

| 2.12 | Measured Channel $S_{21}$ as a function of TX-RX separation $\ldots \ldots \ldots \ldots$                                    | 25 |

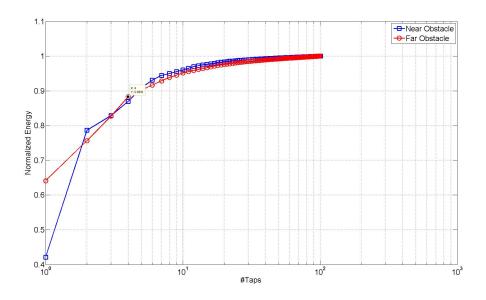

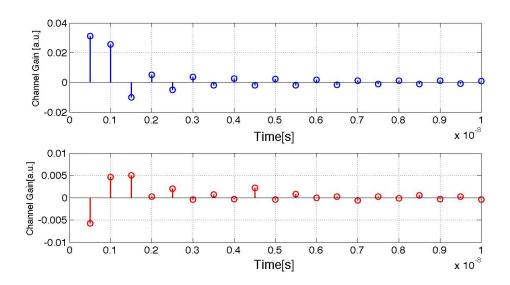

| 2.13 | Received energy as a function of tap number $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                               | 26 |

| 2.14 | Channel Impulse Response Sampled at 2GS/s for good channel: I-component (top) and Q component (bottom)                       | 26 |

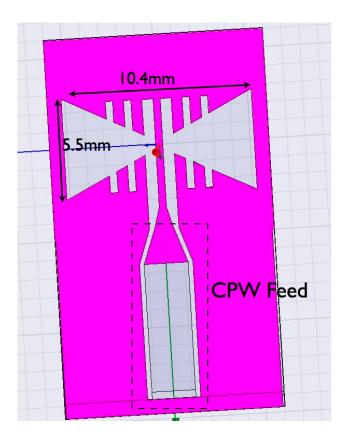

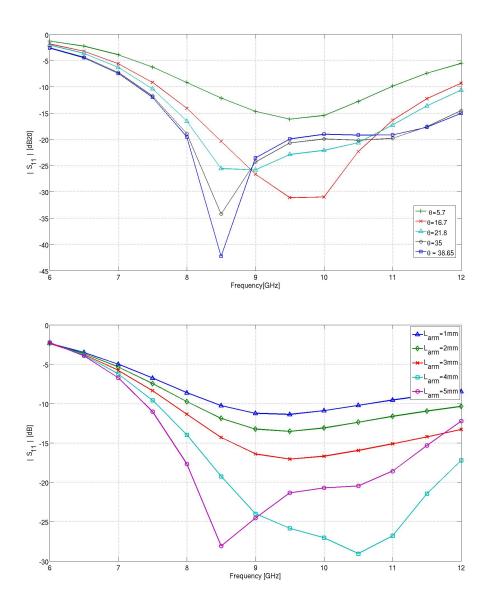

| 2.15 | Annotated Bowtie Antenna Schematic                                                                                           | 28 |

| 2.16 | Bowtie Antenna Simulations: Effect of varying the expansion angle (top); effect of varying the inductive stub length(bottom) | 29 |

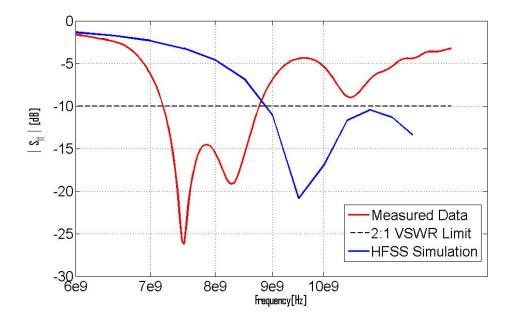

| 2.17 | Bowtie Antenna Measured Reflection versus HFSS Simulations                                                                   | 30 |

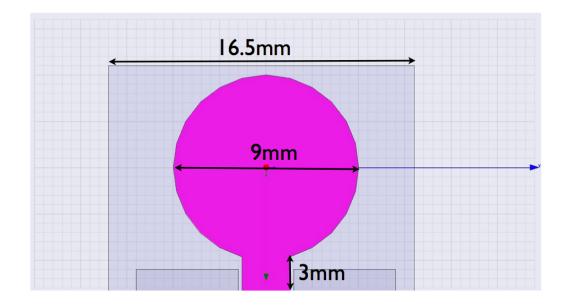

| 2.18 | Monopole antennas annotated schematic:full monopole(top) and loaded hol-<br>low monopole (bottom)                            | 32 |

|      |                                                                                                                              |    |

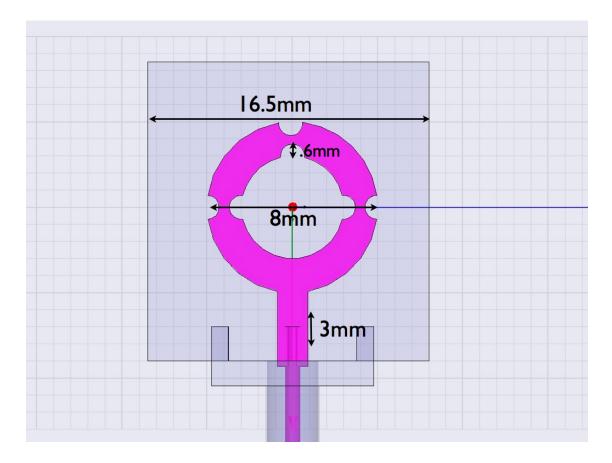

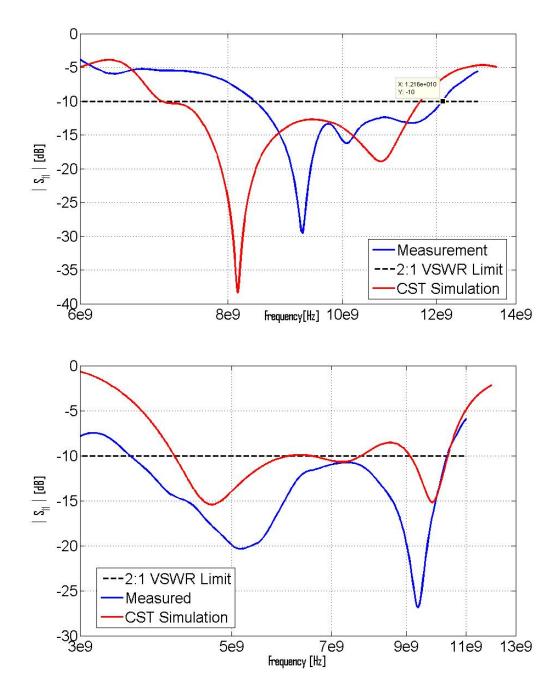

| 2.19 | Measured results from monopole antennas (Full monopole (top) and loaded hollow monopole (bottom)                  | 33 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

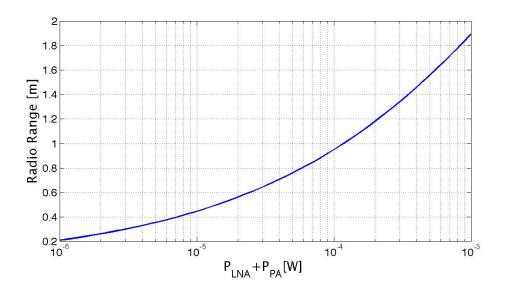

| 3.1  | Optimal Radio Range as a function of total radio power budget                                                     | 35 |

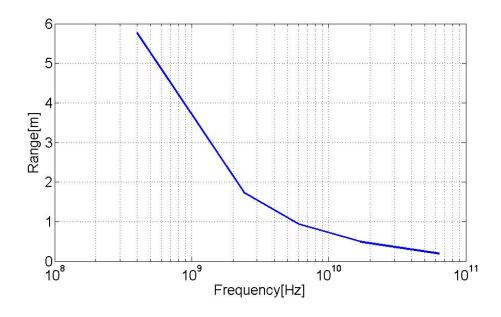

| 3.2  | Maximum Radio Range as a function of carrier frequency                                                            | 36 |

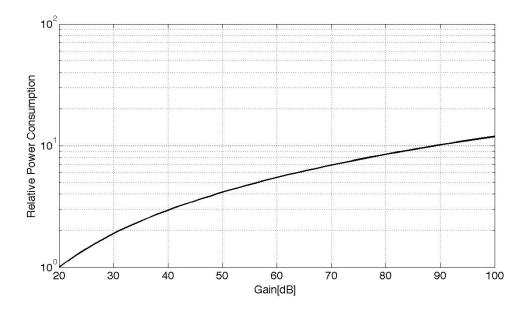

| 3.3  | Power dissipation versus total baseband gain                                                                      | 37 |

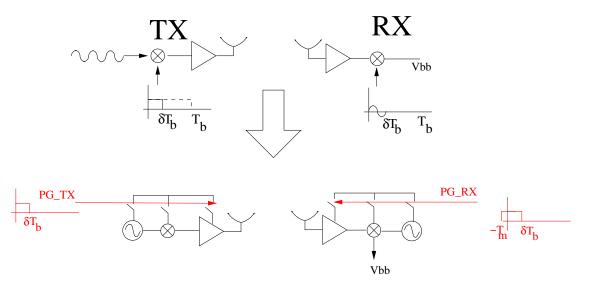

| 3.4  | Transceiver duty cycling concept                                                                                  | 39 |

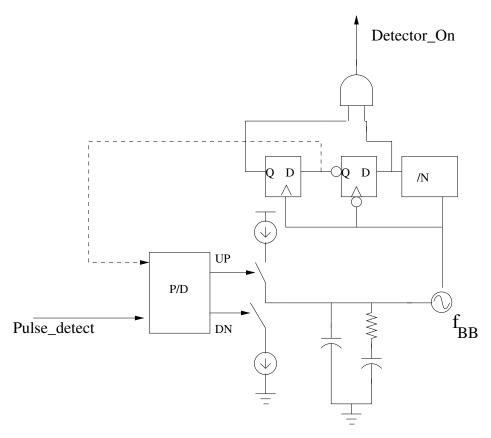

| 3.5  | Analog Synchronizer                                                                                               | 42 |

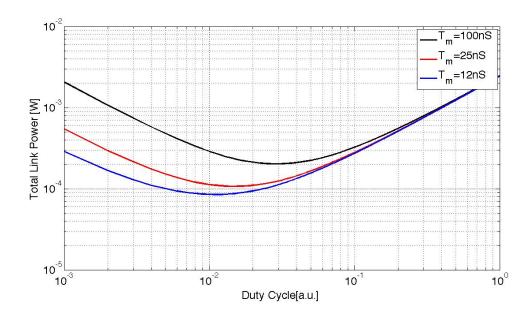

| 3.6  | Power Dissipation of TX+RX as a function of duty-cycling $\ldots$                                                 | 42 |

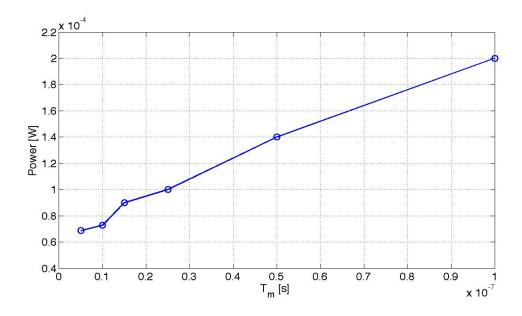

| 3.7  | Minimum Power Dissipation as a function of receiver turn-on-time $T_m$                                            | 43 |

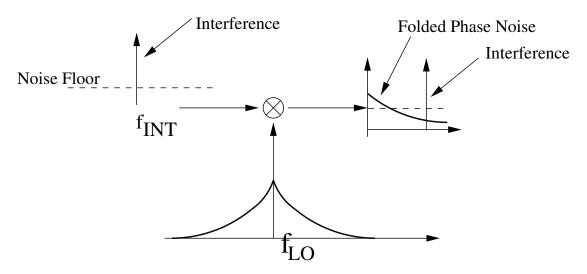

| 3.8  | Desensitization due to reciprocal mixing                                                                          | 45 |

| 3.9  | Comparison between a receiver comprising of LNA+AM detection (left), and lo power oscillator+passive mixer(right) | 48 |

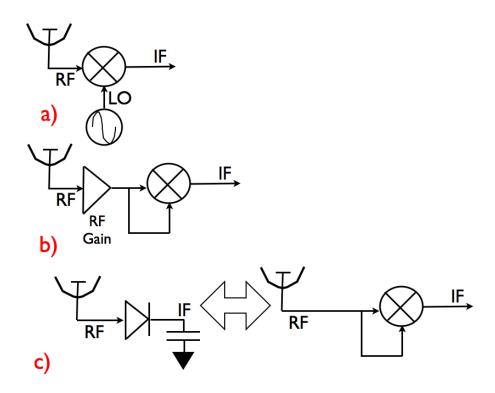

| 3.10 | Low Power Radio Architectures: a) Heterodyning b) RF Gain plus AM-<br>Detection c) Direct AM Detection            | 49 |

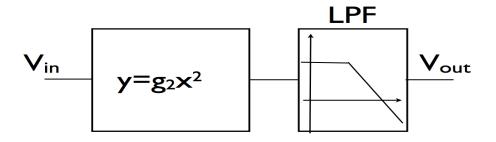

| 3.11 | Behavioral model of AM detector                                                                                   | 49 |

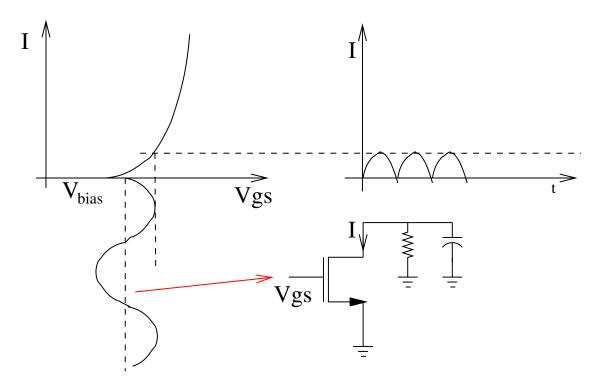

| 3.12 | Operation of a single transistor MOS AM Detector                                                                  | 50 |

| 3.13 | Minimum Input Amplitude s.t. AM-Detector is more power efficient solution                                         | 52 |

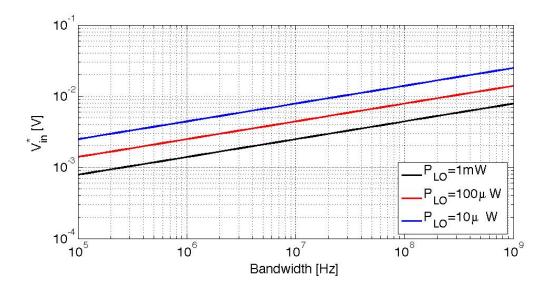

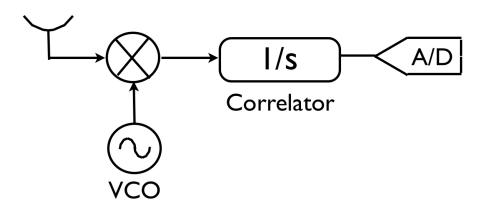

| 4.1  | Receiver architecture with linear downconversion and analog correlation                                           | 54 |

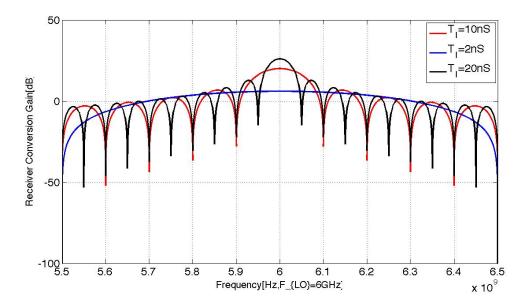

| 4.2  | Conversion gain for receivers with different baseband integration times $\ldots$                                  | 55 |

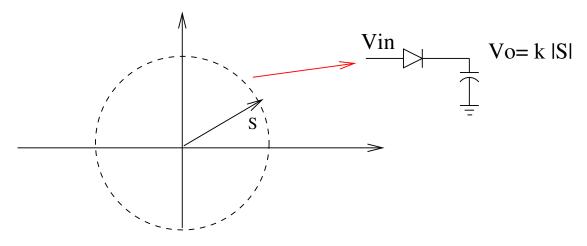

| 4.3  | AM Detection as phasor domain length-measurement $\hdots$                                                         | 56 |

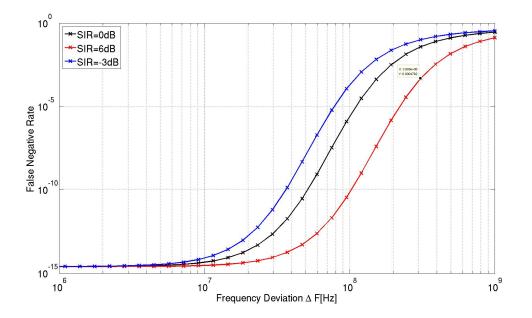

| 4.4  | False Positives Rate for system employing high pass filter versus conventional      case                          | 51 |

| 4.5  | Graphical Interpretation of the worst case angle                                                                  | 59 |

| 4.6  | Complete Baseband architecture for false-negative rate calculation                                                | 60 |

| 4.7  | Bit-Error Rate as a function of power for different frequency offset values                                       | 60 |

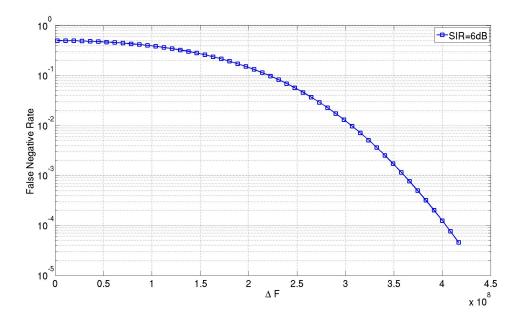

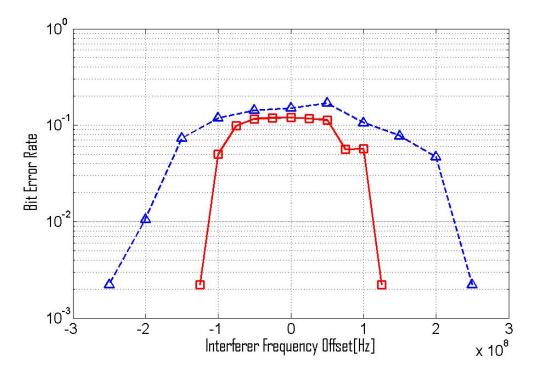

| 4.8  | Bit-Error Rate as a function of interferer offset of SIR=6dB                                                      | 62 |

| 4.9  | Simulated error of the receiver in diode mode for pulse durations of 2nS (blue) and 8nS (red). SIR=6dB            | 62 |

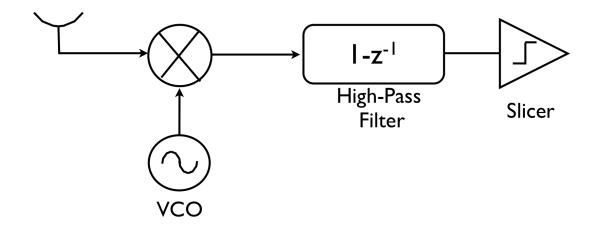

| 4.10 | Receiver with linear down converter and high-pass filtering at baseband                                           | 64 |

| 4.11 | Bit-error rate performance in a linear downconverter as a function of interferer frequency offset                 | 64 |

| 4.12 | Proposed dual-mode receiver with real-time quality of service control(top) and overlaid false negative rates response of linear and AM-detecting down-converters(bottom) | 65 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.13 | Conceptual Synchronizer Diagram                                                                                                                                          | 67 |

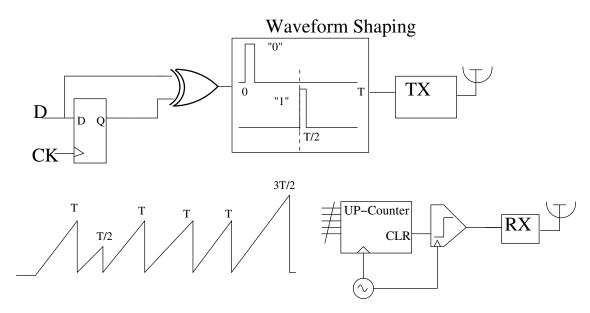

| 4.14 | Block DIagram of Modem employing differential-PPM modulation and merged synchronizer/demodulator                                                                         | 68 |

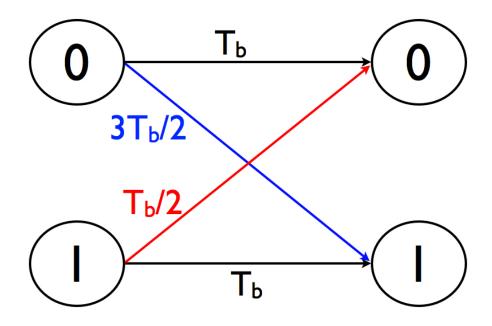

| 4.15 | Trellis diagram for differentially demodulated PPM                                                                                                                       | 69 |

| 4.16 | Effect of jitter on digital timing measurement                                                                                                                           | 70 |

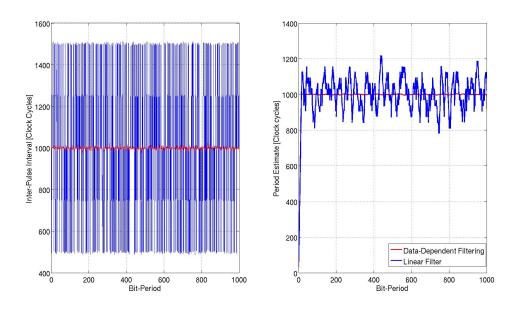

| 4.17 | Period Estimate in the synchronizer with (red) and without (blue) data-<br>dependent rescaling: input to the filter (left) and period estimate(right)                    | 72 |

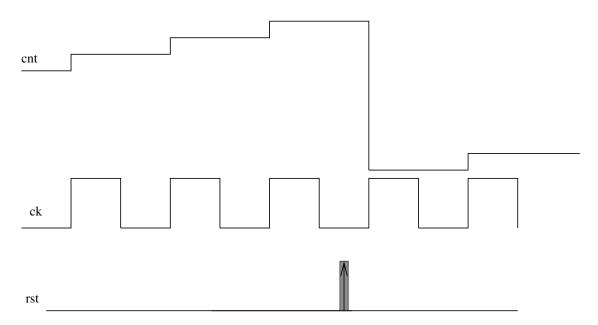

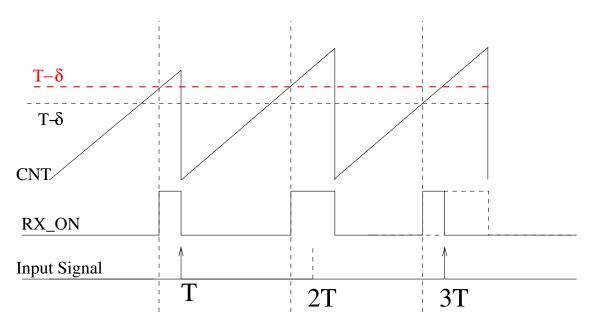

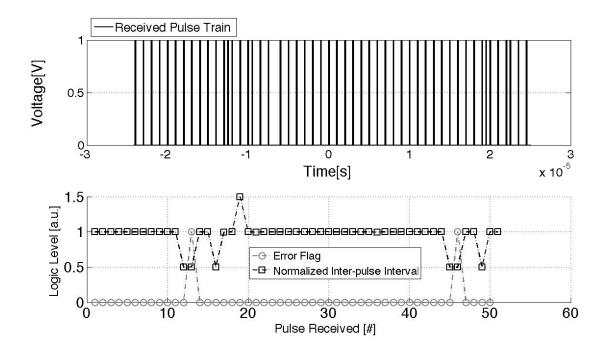

| 4.18 | Waveforms in the synchronizer in the event of a missing pulse                                                                                                            | 73 |

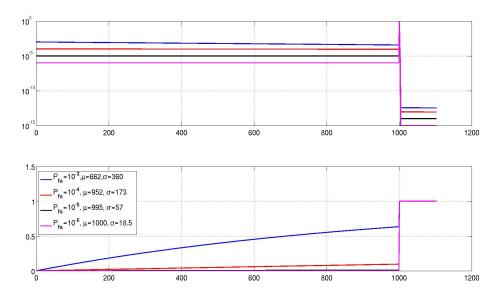

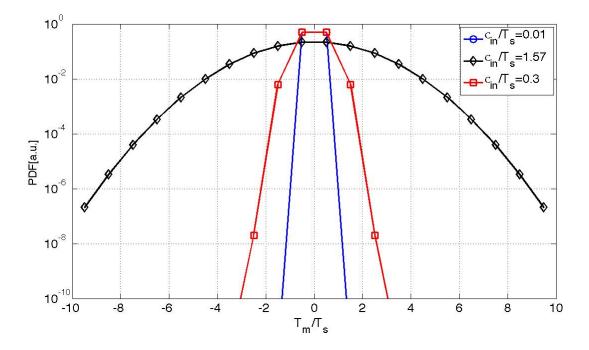

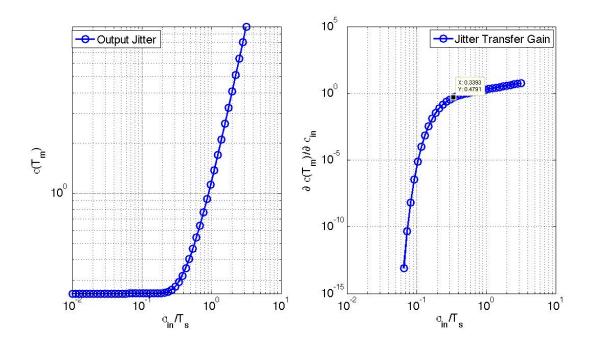

| 4.19 | $\label{eq:probability} Probability density function (top) and cumulative distribution of input transition$                                                              | 74 |

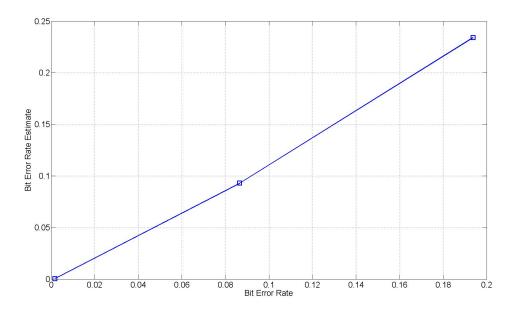

| 4.20 | Simulated BER Estimate versus real BER                                                                                                                                   | 76 |

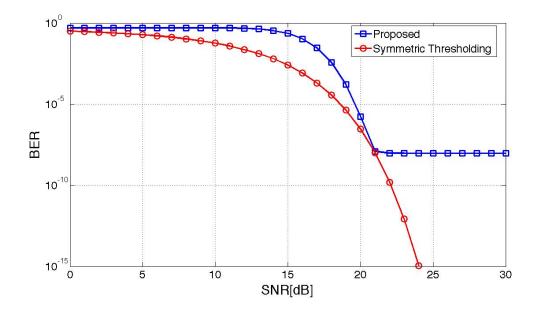

| 4.21 | Comparison of waterfall curves with conventional and proposed amplitude estimation algorithm                                                                             | 77 |

| 5.1  | Block diagram of transceiver architecture                                                                                                                                | 79 |

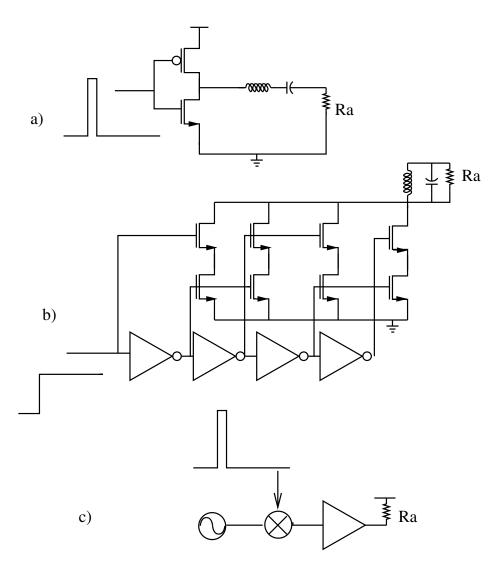

| 5.2  | Bandpass Pulse Generation Architectures: a) filtering; b) Edge Combining;<br>c) Gated Oscillator                                                                         | 80 |

| 5.3  | Digitally Controlled Oscillator Schematic                                                                                                                                | 82 |

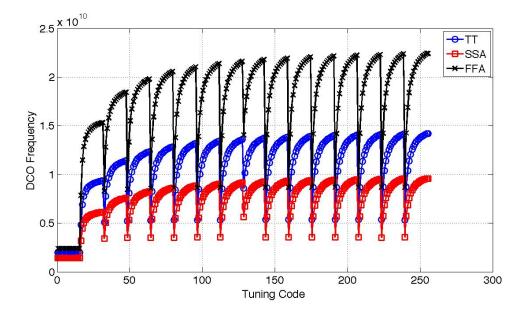

| 5.4  | Simulated tuning range                                                                                                                                                   | 82 |

| 5.5  | Impedance network model                                                                                                                                                  | 83 |

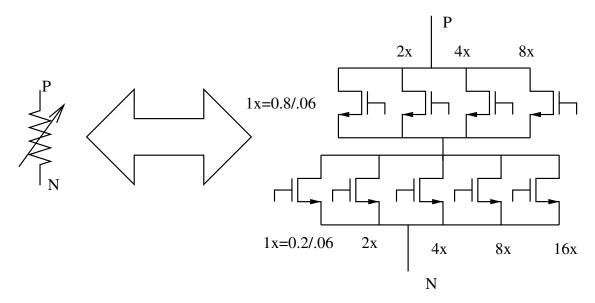

| 5.6  | Tuning control shown for the bottom rail. Top rail is symmetric but uses PMOS transistor with 2x width                                                                   | 84 |

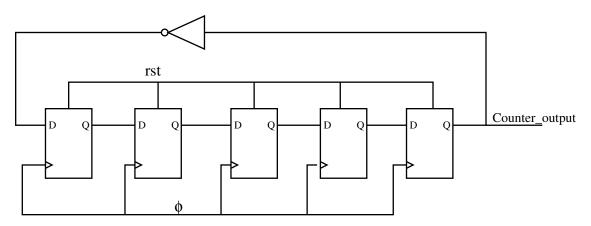

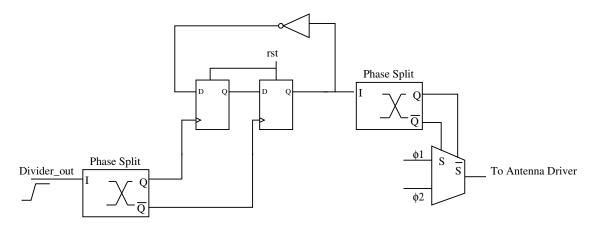

| 5.7  | Johnson divider architecture                                                                                                                                             | 84 |

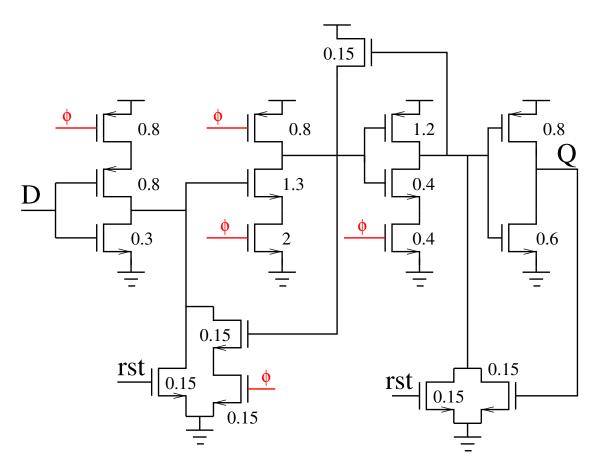

| 5.8  | TSPC Flip Flop circuit details and transistor sizes                                                                                                                      | 85 |

| 5.9  | PSK Modulator/multiplexer and control circuits                                                                                                                           | 86 |

| 5.10 | Simulated Pulser Waveforms                                                                                                                                               | 86 |

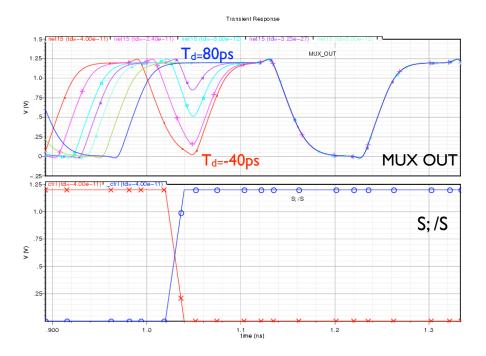

| 5.11 | Effect of delayed inputs on glitching at the output of the multiplexer $\ldots$                                                                                          | 87 |

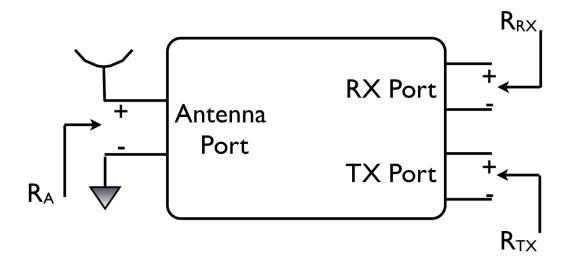

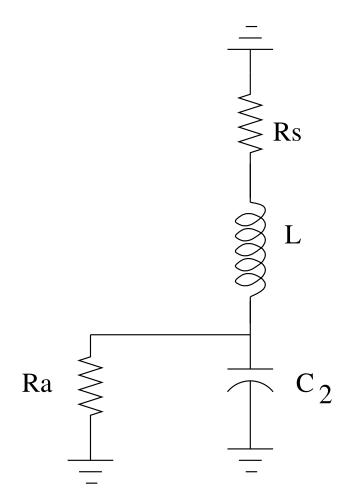

| 5.12 | High-level matching network view                                                                                                                                         | 89 |

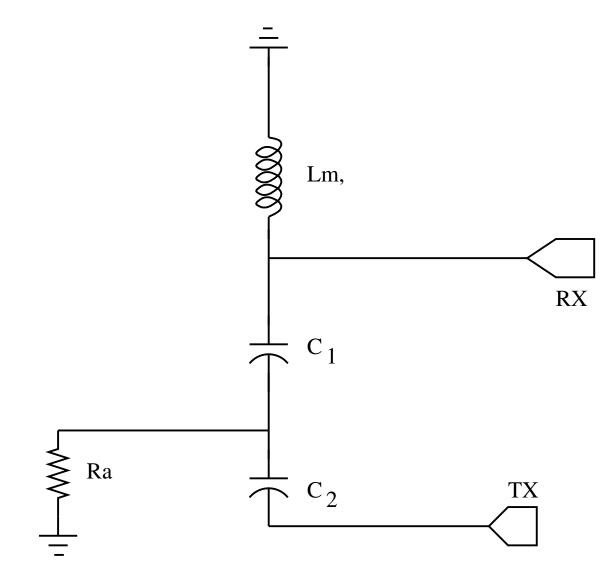

| 5.13 | Matching Network Used in The Design                                                                                                                                      | 91 |

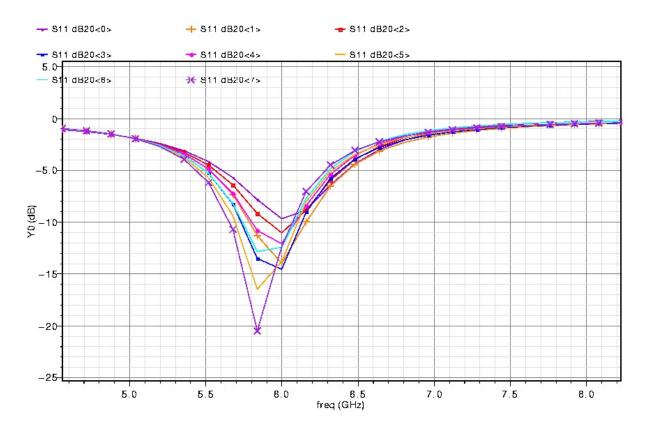

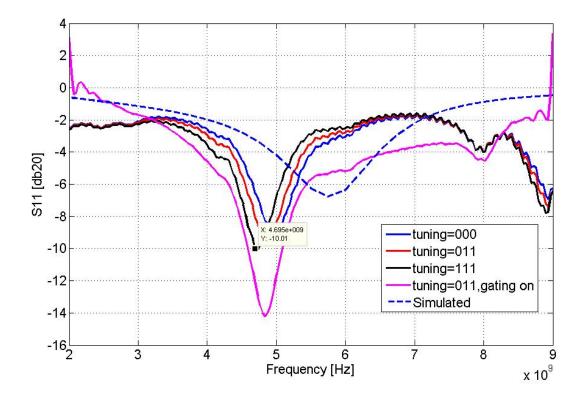

| 5.14 | Simulated input matching network for different values of digitally controlled capacitor $C_2$                                                                            | 92 |

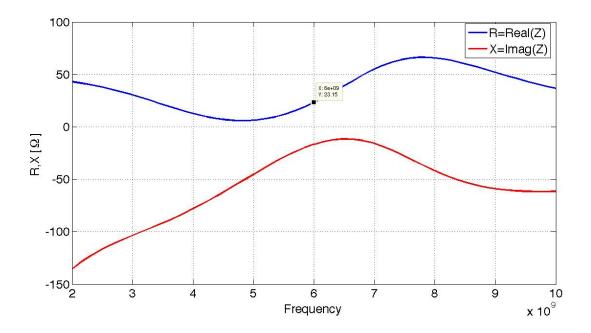

| 5.15 | Simulated impedance at the transmitter port                                                                                                                              | 92 |

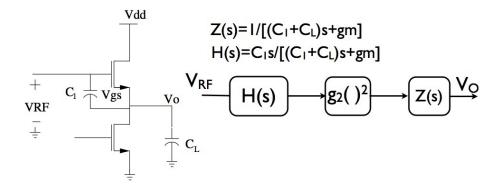

| 5.16 | Envelope Detector topology of $[52]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

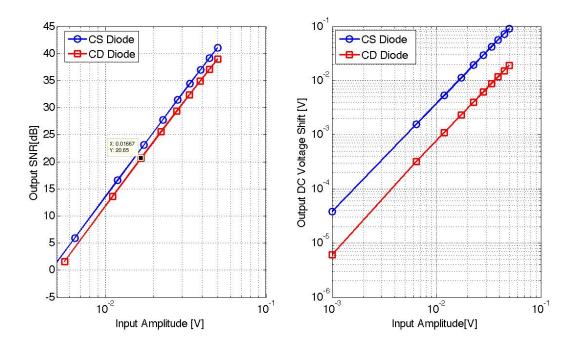

| 5.17 | Output SNR and Amplitude level comparison for CS and CD diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94  |

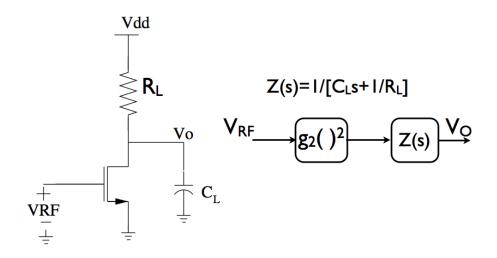

| 5.18 | Common-source diode $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95  |

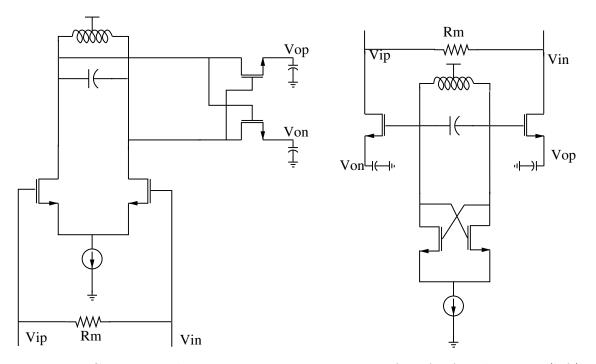

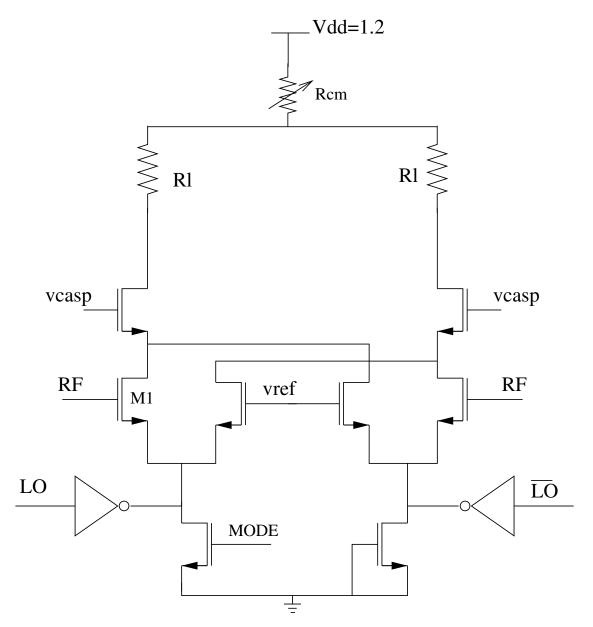

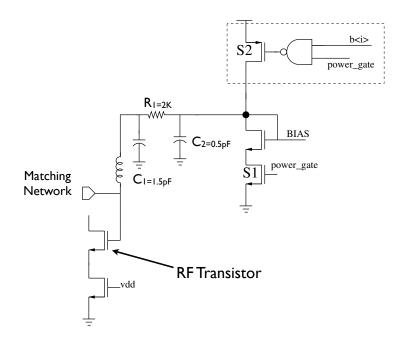

| 5.19 | Implemented Mixer-Diode stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96  |

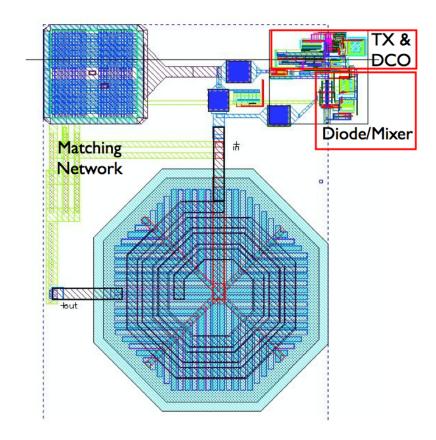

| 5.20 | CAD Layout of RF Front-end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97  |

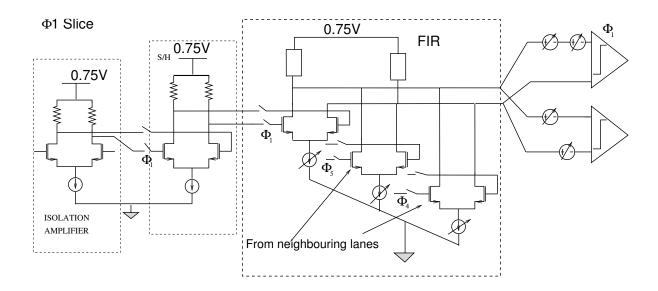

| 5.21 | Circuit diagram for lane of interleaved baseband $\hdots \hdots $ | 98  |

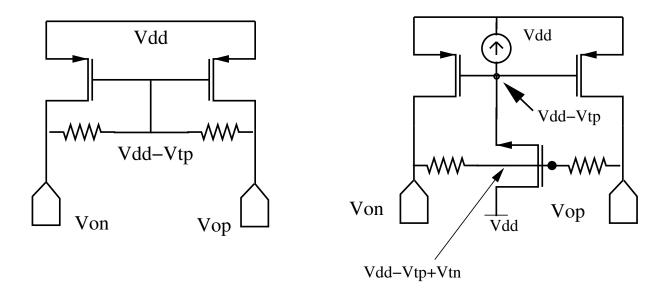

| 5.22 | Loads with high common-mode compliance: diode (left); and diode with level shift(right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 99  |

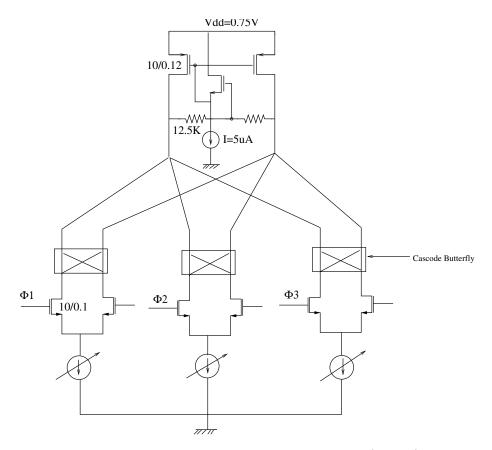

| 5.23 | Distributed filter schematic (1 lane)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100 |

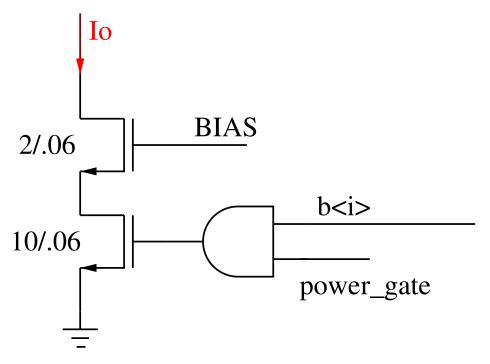

| 5.24 | Dac Unit Cell Schematic. Nominal LSB current is $1.5\mu A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100 |

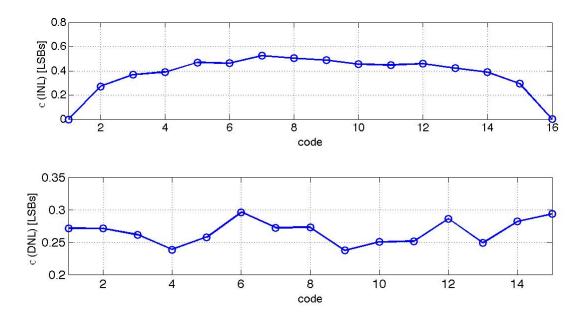

| 5.25 | INL and DNL standard deviation for one the FIR filter bias-DACs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 101 |

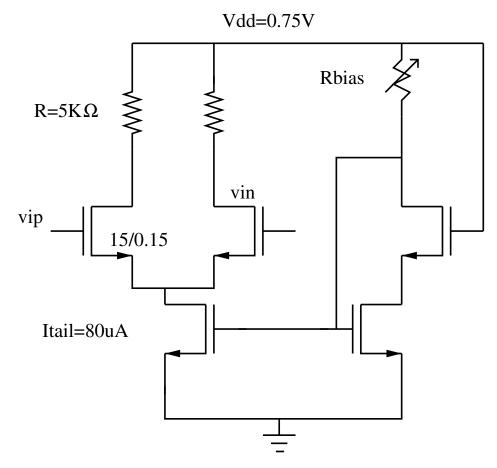

| 5.26 | Track and Hold Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 102 |

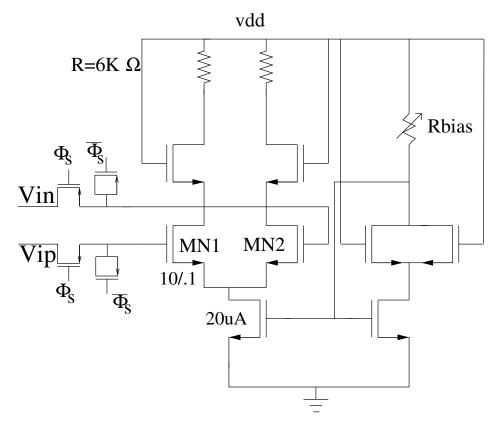

| 5.27 | Isolation Amplifier Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 103 |

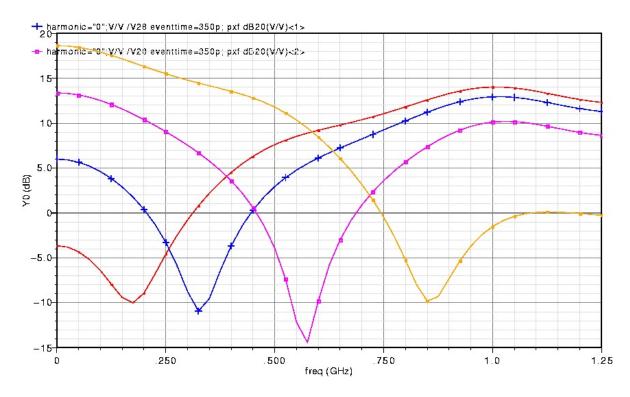

| 5.28 | Simulated FIR Filter frequency response for different settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 104 |

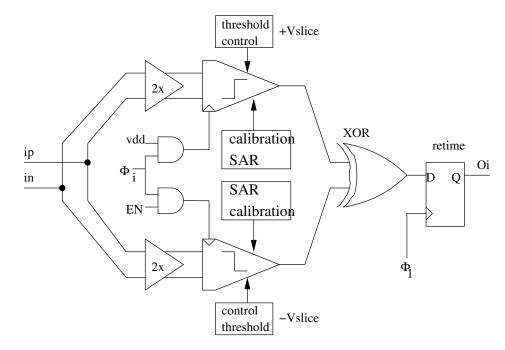

| 5.29 | Block diagram of slicing chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 104 |

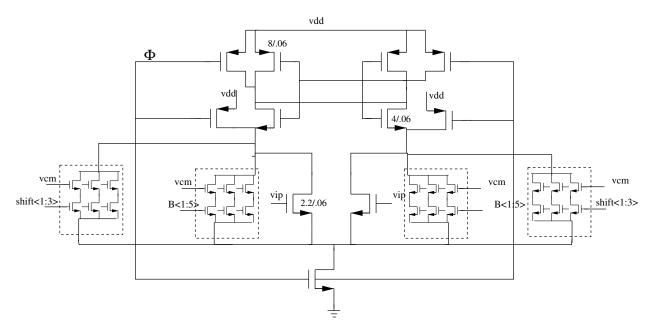

| 5.30 | Annotated Comparator Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 105 |

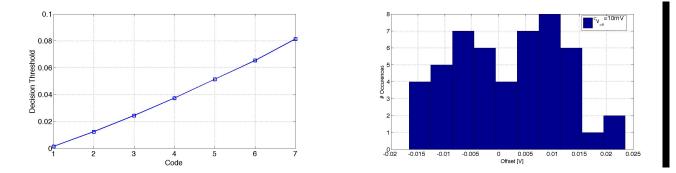

| 5.31 | Comparator simulations: decision threshold versus digital code(left) and un-<br>calibrated input-referred offset distribution (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 106 |

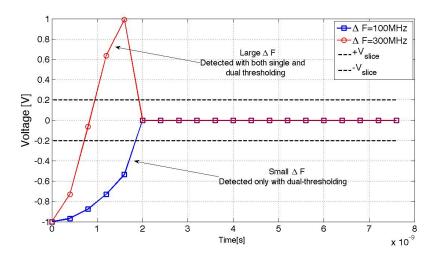

| 5.32 | Example of the effect of dual-thesholding and equivalence between dual thresholding and absolute value thresholding: the blue waveform, corresponding to $\delta F = 100MHz$ and initial phase of $\pi$ , never crosses the positive threshold, and goes undetected by single-comparator scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 106 |

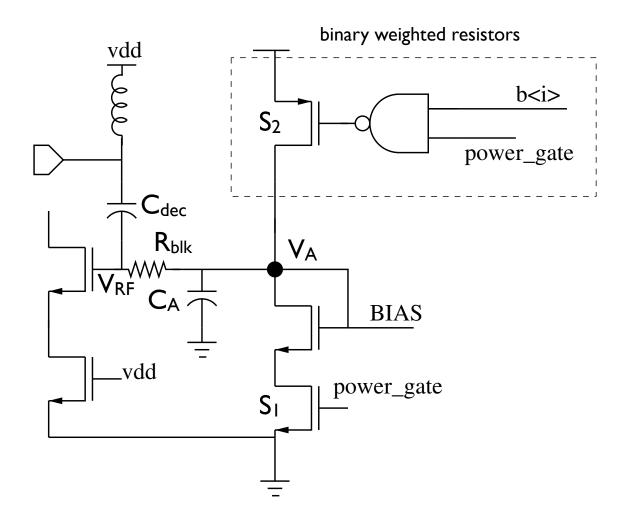

| 5.33 | Schematic of bias circuit for RF front-end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 108 |

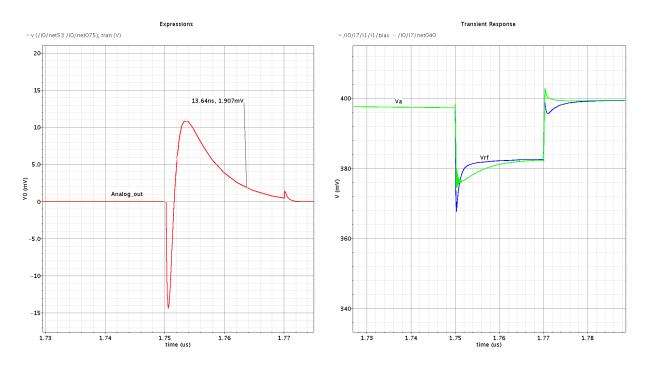

| 5.34 | Simulation of bias settling:mixer differential output (left) and bias lines shown in Fig.5.33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 109 |

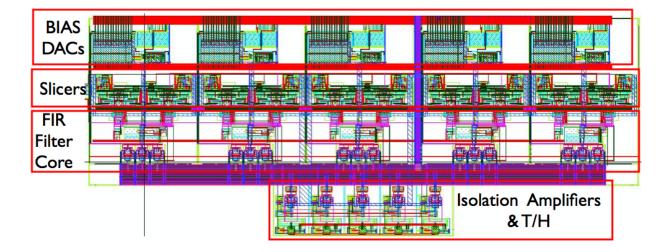

| 5.35 | CAD Layout of analog baseband                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 109 |

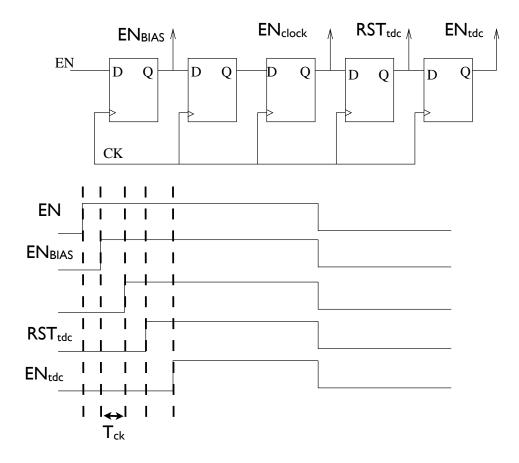

|      | Power-on sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 110 |

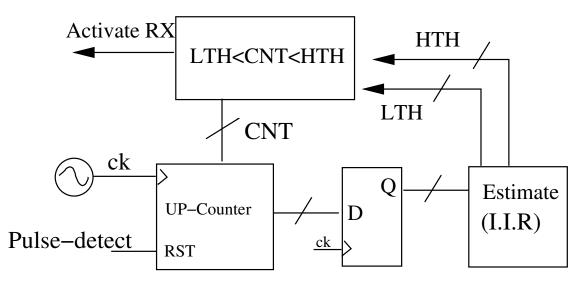

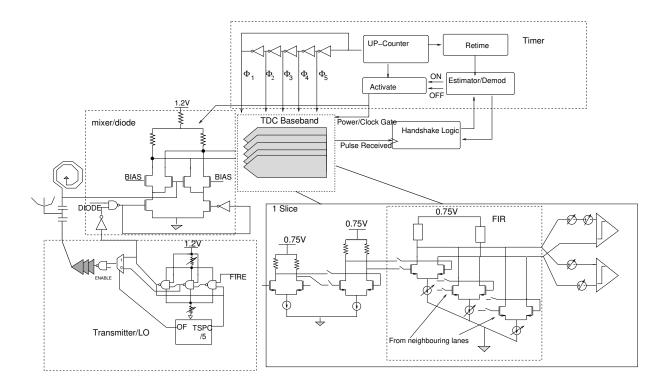

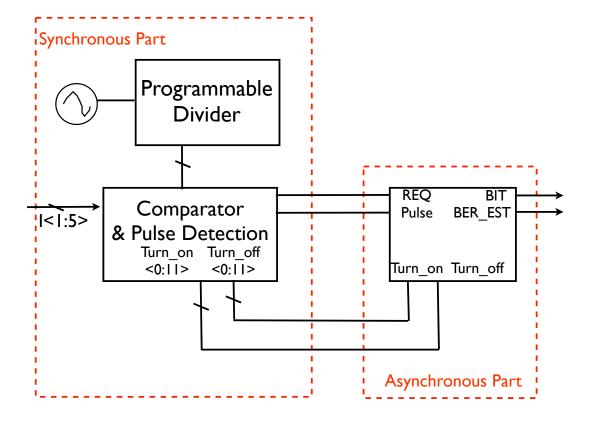

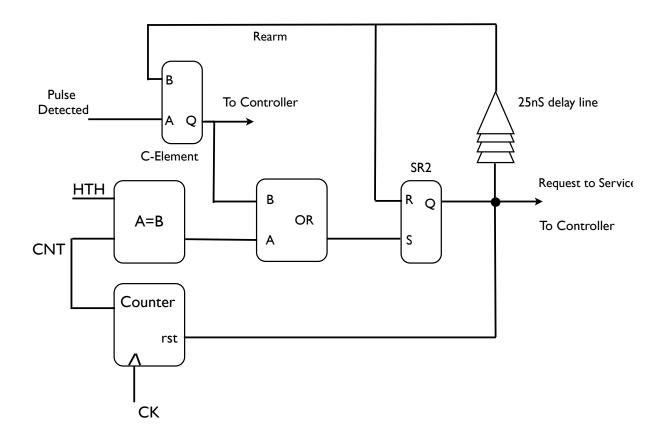

| 5.37 | Synchronizer Architecture and Synchronous-Asynchronous Partition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111 |

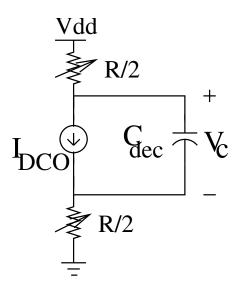

| 5.38 | Baseband DCO and driver schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 113 |

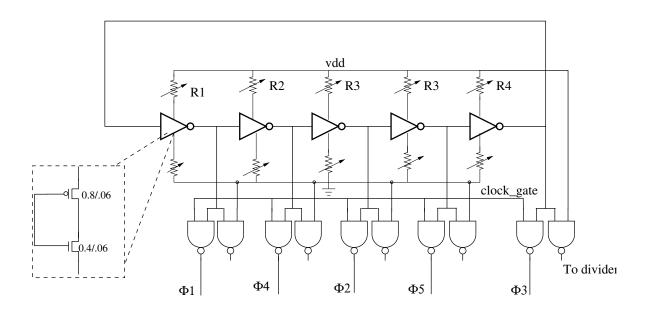

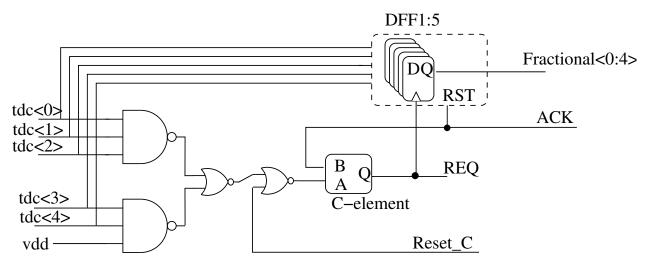

| 5.39 | Baseband divider architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 114 |

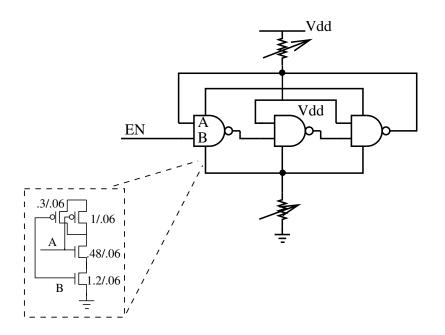

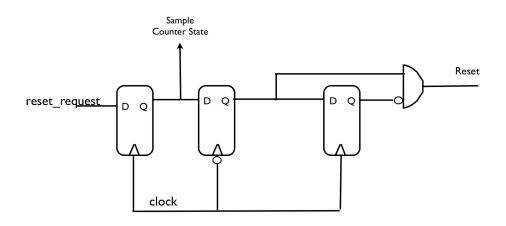

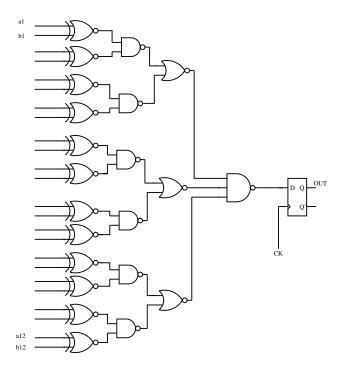

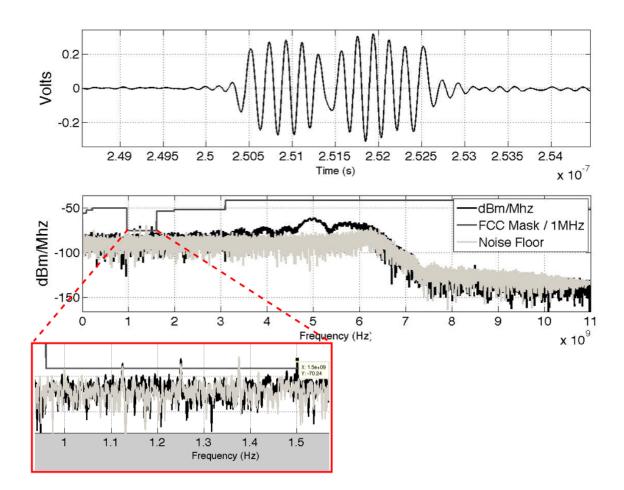

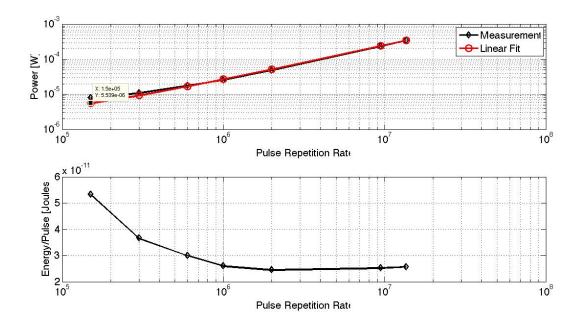

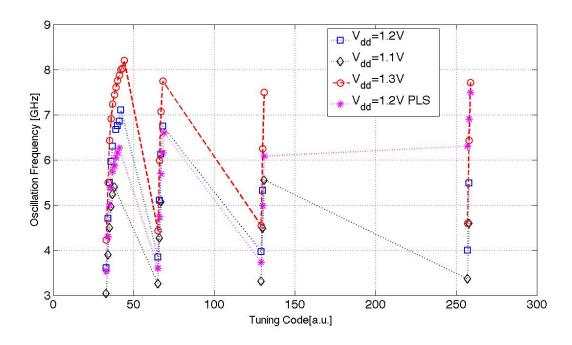

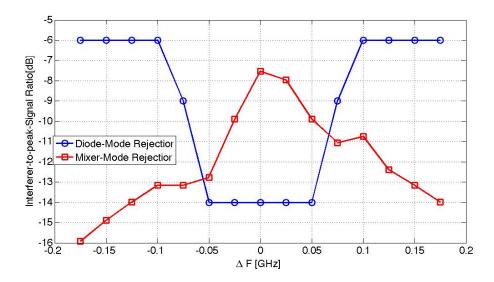

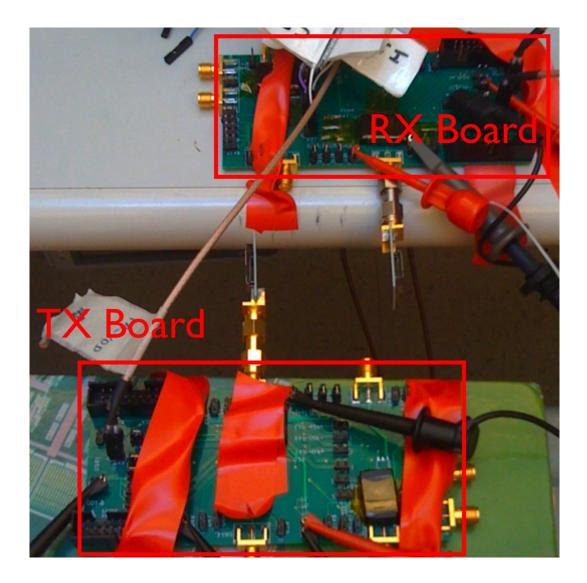

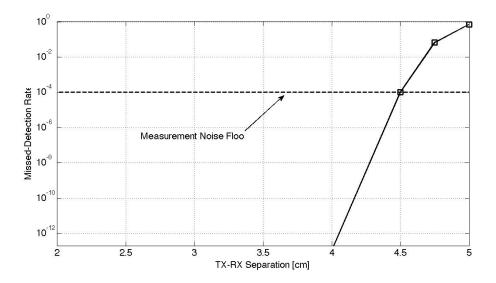

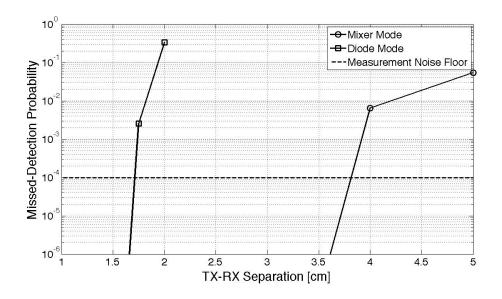

| 5.40 | Counter Reset Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 115 |