## Measuring the Performance of Multimedia Instruction Sets

Nathan T. Slingerland and Alan Jay Smith

### Report No. UCB/CSD-00-1125

December 2000

Computer Science Division (EECS)

University of California

Berkeley, California 94720

### Measuring the Performance of Multimedia Instruction Sets

Nathan Slingerland and Alan Jay Smith {slingn, smith}@cs.berkeley.edu

Computer Science Division EECS Department University of California at Berkeley

December 21, 2000

#### Abstract

Many microprocessor instruction sets include instructions for accelerating multimedia applications such as DVD playback, speech recognition and 3D graphics. Despite general agreement on the need to support this emerging workload, there are considerable differences between the instruction sets that have been designed to do so. In this paper we study the performance of five instruction sets on kernels extracted from a broad multimedia workload. Each kernel was recoded in the assembly language of the five multimedia extensions. We compare the performance of each extension against other architectures as well as to the original compiled C performance. From our analysis we determine how well multimedia workloads map to current architectures, what was useful and what was not. We also propose two enhancements to current architectures: strided memory operations, and superwide registers.

#### 1 Introduction

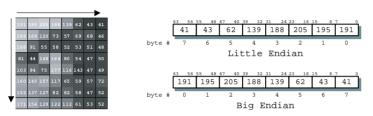

Specialized instructions have been introduced by microprocessor vendors in order to support the specialized computational demands of multimedia applications. The mismatch between wide data paths and the relatively short data types found in multimedia applications has lead the industry to embrace SIMD (single instruction, multiple data) style processing. Unlike traditional forms of SIMD computing in which multiple individual processors execute the same instruction, multimedia instructions are executed by a single processor, and pack multiple short data elements into a single wide (64 or 128-bit) register, with all of the subelements being operated on in parallel.

The goal of this paper is to quantify how architectural differences between multimedia instruction sets translate into differences in performance. Prior studies have primarily focused on a single instruction set in isolation and have measured the performance on sets of kernels taken from vendor provided libraries [Nguy99], [Bhar98], [Allen99], [Chen96], [Rice96], [Naka96], [Rang99]. Our contribution is unique as we do not focus exclusively on a single architecture, and we study the performance of kernels derived from a real measured workload rather than those that have been established a priori. Our results are obtained from actual hardware measurements rather than through simulation, instilling confidence in our results.

Section 2 summarizes the multimedia workload we studied, and details the sixteen computationally important kernels which we extracted from it. Our methodology for recoding the kernels with multimedia instructions and their measurement is described in Section 3. An overview of the five instructions sets, and their implementations, is given in Section 4.

Our analysis is divided into two parts. Section 5 reflects our experience in coding the kernels, and gives insight into the useful and less than useful features of the multimedia instruction sets studied. In Section 6 we compare the performance of the five instruction sets both against one another, as well as their relative improvement over compiled (optimized) C code. Finally, in Section 7 we propose two new directions for multimedia architectures on general purpose microprocessors: strided memory operations and superwide registers.

#### 2 Workload

The lack of a standardized multimedia benchmark has meant that workload selection is the most difficult aspect of any study of multimedia. It was for this reason that we developed the Berkeley multimedia workload [Sling00a]. In selecting the component applications we strove to cover as many types of media processing as possible: image compression (DjVu, JPEG), 3D graphics (Mesa, POVray), document rendering (Ghostscript), audio synthesis (Timidity), audio compression (ADPCM, LAME, mpg123), video compression (MPEG-2 at DVD and HDTV resolutions), speech synthesis (Rsynth), speech compression (GSM), speech recognition (Rasta) and video game (Doom) applications. Open source software was used both for its portability (allowing for cross platform com-

Funding for this research has been provided by the State of California under the MICRO program, and by Cisco Corporation, Fujitsu Microelectronics, IBM, Intel Corporation, Maxtor Corporation, Microsoft Corporation, Sun Microsystems, Toshiba Corporation and Veritas Software Corporation.

parisons) and the fact that we could analyze the source code directly.

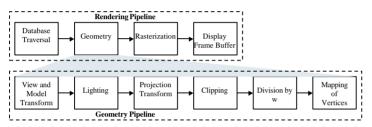

In order to evaluate the various multimedia instruction sets, we hand coded kernels selected from the elements of the Berkeley multimedia workload. Those kernels were chosen based on their computational significance and their suitability for SIMD optimization. Table 1 lists the kernel codes examined. Both Mesa kernels appear to take up a relatively small amount of application CPU time, as software rendering (computing all stages of a rendering pipeline) was used in the portable version of these applications. It was for this reason that rasterization kernels were not included in the kernels studied due to the ubiquity of 3D accelerator cards which offload this from the CPU, and will continue to do so in the foreseeable future. Although we expect that when enough CPU cycles become available, much of the 3D rendering workload will be moved back onto the CPU and done in software (for cost savings), the current trend is moving in the opposite direction. First generation 3D accelerator cards took care of the rasterization stage, but not 3D geometry computations. Current 3D accelerator cards have also taken on the burden of geometry computations, indicating that the growth in complexity of 3D environments is outpacing that of CPU performance, despite the best efforts of multimedia extensions.

### 3 Methodology

#### 3.1 Berkeley Multimedia Kernel Library

Our goal is to measure the performance of existing multimedia instruction sets on our set of important multimedia kernels. Our first step was to we distill from our Berkeley multimedia workload [Sling00a] a set of computationally important kernel functions, from which we formed the Berkeley multimedia kernel library (BMKL). All of the parent applications in the Berkeley multimedia workload were modified to make calls to BMKL rather than internal functions. From a performance standpoint, no piece of code can be realistically extracted and studied in isolation. By measuring a piece of code from within a real system we can realistically see how the shared resources of a computer system, such as CPU, caches, TLB, memory, and registers, affect the code and are affected by it.

Encapsulating the kernels within a library with a well defined interface allowed for: 1) low overhead measurement code to be placed around library functions in order to make measurements as non-invasive as possible, 2) different versions of the library to be quickly substituted in order to aid testing, 3) the addition of new architectures to our study by starting with a copy of the C reference library and then implementing and debugging replacement SIMD assembly functions one at a time.

#### 3.2 Coding Process

As with DSPs, the most efficient way to program with multimedia extensions is to have an expert programmer tune software using assembly language [Kuro98]. Although this

is more tedious and error prone than other methods such as hand coded standard shared libraries or automatic code generation by a compiler, it is a method that is available on every platform, and allows for great flexibility and precision when coding. We chose to code each kernel in assembly language ourselves rather than measure vendor supplied optimized libraries in order to prevent differences in programmer ability and time spent coding between the vendors' from potentially skewing our comparison.

All of the assembly codes in our study were written by the same programmer (Slingerland) with an approximately equal amount of time spent on each platform. Programming tools for cycle-accurate instruction scheduling through simulation were not used in order to equalize differences between the tools available on each platform. Instructions were scheduled sanely by keeping data consumption as far from data use as possible, unrolling loops when of performance benefit, and manually scheduling instructions so as to take advantage of multiple functional units.

For reasons of practicability, we limited our optimizations to the kernel level; we did not rewrite entire applications. This had ramifications for data alignment and data structure layout on some architectures. In some cases it was not practical to code a SIMD version of a kernel if an instruction set lacked the requisite functionality. For example, Sun's VIS and DEC's MVI do not support partitioned floating point, so floating point kernels were not recoded for these platforms. DEC's MVI also does not contain any data communication (e.g. permute, mix, merge) or partitioned integer multiply instructions. If there was no compelling opportunity for performance gain, kernels were not recoded from C. The C version was considered to be a particular platform's "solution" to a kernel when the needed SIMD operations were not provided. It might be supposed that hand coding would be superior to compiler generated code anyway, even without SIMD instructions. Although this may have been true at one time when instruction set architectures were designed with assembly language programmers in mind, modern instruction sets are targeted at compilers [Lawl92], [Patt96].

#### 3.3 Measurement

Performance Monitoring Counters All of the microprocessors studied include performance monitoring counters to allow for interesting architectural events to be counted in real time during program execution. Although performance counters were sometimes used to guide our optimizations, their primary purpose was to be nearly cycle-accurate timers with which to measure the very short execution times of the kernels in the BMKL.

C Compilers and Optimization Flags The most architecturally tuned compiler on each architecture was used to compile the C reference version of the Berkeley Multimedia Kernel library. The optimization flags used were those which give the best general speedup and highest level of optimization without resorting to tuning the compiler flags to a particu-

| Kernel Name                 | Source        | Data       | Sat          | Native                    | Src   | Satic | %Static | % CPU  |

|-----------------------------|---------------|------------|--------------|---------------------------|-------|-------|---------|--------|

|                             | Application   | Туре       | Arith        | $\mathbf{W}\mathbf{idth}$ | Lines | Instr | Instr   | Cycles |

| Add Block                   | MPEG-2 Decode | 8-bit (U)  | √            | 64-bits                   | 46    | 191   | 0.1%    | 13.7%  |

| Block Match                 | MPEG-2 Encode | 8-bit (U)  |              | 128-bits                  | 52    | 294   | 0.4%    | 59.8%  |

| Clip Test and Project       | Mesa*         | FP         |              | limited                   | 95    | 447   | 0.1%    | 0.8%   |

| Color Space Conversion      | JPEG Encode   | 8-bit (U)  |              | limited                   | 22    | 78    | 0.1%    | 9.8%   |

| DCT                         | MPEG-2 Encode | 16-bit (S) |              | 128-bits                  | 14    | 116   | 0.1%    | 12.3%  |

| FFT                         | LAME*         | FP         |              | limited                   | 208   | 981   | 4.4%    | 14.5%  |

| Inverse DCT                 | MPEG-2 Decode | 16-bit (S) | √            | 128-bits                  | 75    | 649   | 0.3%    | 29.7%  |

| Max Value                   | LAME*         | 32-bit (S) |              | unlimited                 | 8     | 39    | 0.2%    | 12.0%  |

| Mix                         | Timidity      | 16-bit (S) | $\checkmark$ | unlimited                 | 143   | 829   | 1.0%    | 35.7%  |

| Quantize                    | LAME*         | FP         |              | unlimited                 | 55    | 312   | 1.4%    | 15.3%  |

| Short Term Analysis Filter  | GSM Encode    | 16-bit (S) | $\checkmark$ | 128-bits                  | 15    | 79    | 0.1%    | 20.2%  |

| Short Term Synthesis Filter | GSM Decode    | 16-bit (S) | $\checkmark$ | 128-bits                  | 15    | 114   | 0.2%    | 72.7%  |

| Subsample Horizontal        | MPEG-2 Encode | 8-bit (U)  | $\checkmark$ | 88-bits                   | 35    | 244   | 0.3%    | 2.6%   |

| Subsample Vertical          | MPEG-2 Encode | 8-bit (U)  | $\checkmark$ | unlimited                 | 76    | 478   | 0.6%    | 2.1%   |

| Synthesis Filtering         | mpg123*       | FP         | $\checkmark$ | 512-bits                  | 67    | 348   | 0.4%    | 39.6%  |

| Transform and Normalize     | Mesa*         | FP         |              | limited                   | 51    | 354   | 0.1%    | 0.7%   |

Table 1: **Multimedia Kernels Studied** - from left to right, the colums list 1) primary data type specified as N-bit ({Unsigned,Signed}) integer or floating point (FP), 2) if saturating arithmetic is used, 3) native width; the longest width which does not load/store/compute excess unused elements, 4) static C source line count (for those lines which are executed), 5) percentage of total static instructions, 6) percentage of total CPU time spent in the kernel. The later three statistics are machine specific and are for the original C code on a Compaq DS20 (dual 500 MHz Alpha 21264, Tru64 Unix v5.0 Rev. 910) machine, compiled with GCC v2.8.1 (\*) or DEC C v5.6-075.

lar kernel. The specific compiler and associated optimization flags used on each platform are listed given in the Appendix.

#### 4 Instruction Sets

In this paper we study five architectures with different multimedia instruction sets (Table 2 lists the parameters for the exact parts we used). Most of the instruction sets (AMD'S 3DNow!, DEC's MVI, Intel's MMX, Sun's VIS) use 64-bit wide registers, while Motorola's AltiVec and Intel's SSE are 128-bits wide. The size of the register file available on each architecture varied widely, ranging from 8 64-bit registers on the x86 based AMD Athlon and Intel Pentium III to 32 128-bit wide registers with Motorola's AltiVec extension.

All of the multimedia extensions support integer operations, although the types and widths of available operations vary greatly. The earliest multimedia instruction sets (e.g. Sun's VIS and DEC's MVI) had design goals limited by the immaturity of their target workload and unproven benefit to performance. Because of this, any approach which greatly modified the overall architecture or significantly affected die size was out of the question. Leveraging as much functionality as possible from existing chip architectures was a high priority. Thus, the Sun and DEC extensions do not implement partitioned floating point instructions. Witness also the difference between Intel's first multimedia extension, MMX (1997), which had as one of its primary design goals to not require any new operating system support, and Intel's SSE (1999) which added new operating system maintained state (8 128-bit wide registers) for the first time since the introduction of the Intel386 instruction set (1985).

The processors studied vary in terms of instruction latency as well as the throughput per cycle. Processor clock rates were all 500 MHz, with the exception of the Sun UltraSPARC IIi, for which only a 360 MHz system was available. Although multimedia extensions primarily focus on extracting data level parallelism, most modern microprocessors are also superscalar, and thereby allow for multiple multimedia instructions to be issued every cycle. All of the architectures we looked at are fully pipelined, so barring any data dependencies, one new SIMD instruction can begin per functional unit each clock cycle. Typically, there are separate functional units for SIMD integer and SIMD floating point processing, although on the x86 architectures they are combined. [Sling00c] surveys existing multimedia instruction sets in more detail.

Sun Sun's UltraSPARC IIi processor incorporates the VIS multimedia extension, which implements a set of SIMD integer instructions that share the existing UltraSPARC floating point register file. Partitioned multiplication is done through 8-bit multiplication primitive instructions. A graphics status register (GSR) is used to support data alignment and scaling for pack operations.

Intel Intel's Pentium III processor includes their original SIMD integer MMX extension, as well as the newer SIMD floating point SSE instruction set. MMX is a 64-bit wide SIMD integer extension, which is mapped onto the existing x87 floating point architecture and registers and introduces no new architectural state (registers or exceptions). SSE is a

|                                                 | AMD Athlon                                                                  | DEC Alpha 21264 | Intel Pentium III        | Motorola G4    | Sun UltraSPARC IIi |

|-------------------------------------------------|-----------------------------------------------------------------------------|-----------------|--------------------------|----------------|--------------------|

| Clock [Current] (MHz)                           | 500 [1000]                                                                  | 500 [667]       | 500 [1000]               | 500 [500]      | 360 [480]          |

| SIMD Extension(s)                               | MMX/3DNow!+                                                                 | MVI             | MMX/SSE                  | AltiVec        | VIS                |

| SIMD Instructions                               | 57/24                                                                       | 13              | 57/70                    | 162            | 121                |

| First Shipped                                   | June 1999                                                                   | February 1998   | February 1999            | August 1999    | November 1998      |

| Transistors $(x10^6)$                           | 22.0                                                                        | 15.2            | 9.5                      | 6.5            | 5.8                |

| Process $(\mu \mathbf{m})$ [Die Size $(mm^2)$ ] | 0.25 [184.0]                                                                | 0.25 [225.0]    | 0.20 [104.6]             | 0.20 [83.0]    | 0.25 [147.5]       |

| L1 \$I Cache, \$D Cache (Kbytes)                | 64, 64                                                                      | 64, 64          | 16, 16                   | 32, 32         | 32, 64             |

| L2 Cache (Mbytes)                               | 0.5                                                                         | 4               | 0.5                      | 1              | 2                  |

| Register File (# x width)                       | $\mathrm{FP}(8\mathrm{x}64\mathrm{b})/\mathrm{FP}(8\mathrm{x}64\mathrm{b})$ | Int (31x64b)    | FP(8x64b)/8x128b         | 32x128b        | FP(32x64b)         |

| Reorder Buffer Entries                          | 72                                                                          | 35              | 40                       | 6              | 12                 |

| Int, FP Multimedia Units                        | 2 (combined)                                                                | 2, 0            | 2 (combined)             | 3, 1           | 2, 0               |

| Int Add Latency                                 | 2 [64b/cycle]                                                               | =               | 1 [64b/cycle]            | 1 [128b/cycle] | 1 [64b/cycle]      |

| Int Multiply Latency                            | 3 [64b/cycle]                                                               | =               | 3 [64b/cycle]            | 3 [128b/cycle] | 3 [64b/cycle]      |

| FP Add Latency                                  | 4 [64b/cycle]                                                               | =               | 4 [64b/cycle]            | 4 [128b/cycle] | <del>-</del>       |

| FP Multiply Latency                             | 4 [64b/cycle]                                                               | =               | 5 [64b/cycle]            | 4 [128b/cycle] | -                  |

| FP ~1/sqrt Latency                              | 3 [32b/cycle]                                                               | =               | $2~[64\mathrm{b/cycle}]$ | 4 [128b/cycle] | -<br>-             |

Table 2: **Microprocessors Studied** - All parameters are for the actual chips used in this study. Clock lists the speed for the specific part studied as well as the current (December 2000) maximum shipping clock speed. A SIMD register files may be shared with existing integer (Int) or floating point (FP) registers, or be separate. Note that some of the processors implement several multimedia extensions (e.g. Pentium III has MMX and SSE) - the corresponding parameters for each are separated with "/". A dash (-) indicates that a particular operation is not available on a given architecture, and so no latency and throughput numbers are given. DEC's MVI extension (on the 21264) does not include any of the listed operations, but all MVI instructions have a latency of 3 cycles [64b/cycle].[Burd] [Noer] [AMD99] [AMD00] [AMDWP] [Carl97] [Comp00] [Intel97] [Intel99a] [Kesh99] [Kohn95] [Moto00] [Norm98] [Sun97]

follow on to MMX which is primarily a SIMD floating point extension but also incorporates feedback on MMX from software vendors in the form of new integer instructions. Unlike MMX, the floating point side of SSE does add new architectural state to the Intel architecture with the addition of an 8 x 128-bit register file and exceptions to support IEEE compliant floating point operations. Although the SSE instruction set architecture and register file are defined to be 128-bits wide, the Pentium-III SSE execution units are actually 64-bits (two single precision floating point elements) wide in hardware. The instruction decoder translates 4-wide (128-bit) SSE instructions into pairs of 2-wide (64-bit) internal micro-ops.

AMD The AMD Athlon processor implements MMX (which was licensed from Intel), in addition to AMD's own 3DNow! extension which utilizes the same x87 floating point registers and basic instruction formats as MMX, but adds a partitioned single precision floating point data type. The Athlon processor actually extends 3DNow! with Enhanced 3DNow! that adds floating point and integer operations to make 3DNow! functionally equivalent to Intel's SSE extension.

**DEC** The DEC (now Compaq, but we will refer to it as DEC for historical consistency) Alpha 21264A processor includes the SIMD integer Motion Video Instructions (MVI) multimedia extension. It is the smallest of the multimedia instruction sets, weighing in with only 13 instructions. MVI shares the existing Alpha 32-register integer register file. No-

tably, no SIMD saturating addition/subtraction, multiplication, or shift instructions are included.

Motorola Motorola's MPC7400 (also known as the G4) processor utilizes their 128-bit wide SIMD AltiVec extension which supports a wide variety of integer data types, as well as partitioned single precision floating point. A dedicated 32 x 128-bit register file is implemented, along with four non-identical parallel, pipelined vector execution units. Hardware assisted software prefetching is implemented, where by a prefetch stream is set up by software, and fetched into the cache independently by hardware.

### 5 Analysis

In the next section we use our experience coding each of the sixteen kernels with five different multimedia extensions to determine: 1) existing architectural features that are useful, 2) features that have been implemented, but don't appear to be useful, and 3) significant bottlenecks in current multimedia architectures. Illustrating our discussion are code fragments both from the original C source code of each kernel algorithm, as well as the different SIMD implementations. The code fragments consist of a few of the key central lines of code from a given kernel. This gives an idea about the types of operations and data types used. The data types of all of the variables in our sample C code are specified in a platform independent way such that the prefix indicates the type: INT: signed integer, UINT: unsigned integer, FP: floating point, followed by

N, the number of bits. The complete original C source code for each kernel can be found in Appendix B. Source code for the SIMD implementations of the BMKL are available on the web at http://www.cs.berkeley.edu/~slingn/research/.

#### 5.1 Register File and Data Path

Multimedia instruction sets can be broadly categorized according to the location and geometry of the register file upon which SIMD instructions operate. Alternatives include the reuse of the existing integer or floating point register files, or implementing an entirely separate one. The type of register file affects the width and therefore the number of packed elements that can be operated on simultaneously (vector length).

Integer Data Path Implementing multimedia instructions on the integer data path has the advantage that the functional units for shift and logical operations need not be replicated. Partitioned addition and subtraction are easily created by blocking the appropriate carry bits. Modifications to the integer data path to accommodate multimedia instructions can potentially adversely affect the critical path of the integer data-path pipeline [Kuro98]. On the x86 (AMD, Intel) and PowerPC (Motorola) architectures the integer data path is 32-bits wide, making a shared integer data path approach less compelling due to the limited amount of data level parallelism possible.

Floating Point Data Path The reuse of floating point rather than integer registers has the advantage of not being shared with pointers and loop and other control flow variables. In addition, multimedia and floating point instructions are not typically used simultaneously [Kuro98]. All of the architectures examined have floating point data paths which support at least double-precision (64-bit wide) operations, which for many architectures is wider than the integer data path.

Separate Data Path A separate data path has the advantage of simplifying pipeline control and increasing the overall number of registers. Disadvantages include the need for saving and restoring the new registers on context switches, as well as the relative difficulty and high overhead of moving data between register files.

SIMD Register Width Perhaps one of the most critical factors in SIMD instruction set design is deciding how long vectors will be. If an existing data path is to be reused, there is little choice, but when a new data path is to be designed it makes sense to ask how wide is wide enough. Too short of a vector length limits the ability to exploit data parallelism, while an excessively long vector length can degrade performance and increase the amount of clean up code overhead. The "native width" column of Table 1 specifies how each of the multimedia kernels fits into one of the following three categories:

1. <u>unlimited width</u> - Kernels that operate on data elements which are truly independent and are naturally arranged

so as to be amenable to SIMD processing. The inner loops of these kernels can be strip mined at almost any width, with the increase in performance of a longer vector being directly proportional to the increase in vector length.

- 2. <u>limited width</u> Although data elements are independent, there is overhead involved in rearranging input data so that it may be operated on in a SIMD manner with longer vectors. Thus, the performance advantage of longer vectors is limited by the overhead (which typically increases with vector length) required to employ them.

- 3. <u>exact width</u> A kernel which has a precise natural width which can be considered to be the right match for the kernel. This width is the longest width which does not load, store, or compute excess unused elements.

Long vectors can be a problem when their length exceeds the natural width of an algorithm. A good example of this problem is the add block kernel, which operates on MPEG subblocks (8 x 8 arrays of pixels). One input array (bp) consists of signed 16-bit integer values and the other (rfp) of unsigned 8-bit integer (Algorithm 1).

Algorithm 1 Add Block - computed for each pixel in a subblock

```

INT16 *bp; UINT8 *rfp; INT32 tmp;

tmp = *bp++ + *rfp; /* Add */

*rfp = tmp>255 ? 255 : (tmp<0 ? 0 : tmp); /* Clip */

```

During the block reconstruction phase of motion compensation in the decoder, a block of pixels is reconstituted by summing the pixels in different subblocks. Consider the AltiVec implementation of the add block kernel (Algorithm 2). Motorola's AltiVec is the only SIMD integer extension examined which is 128-bits wide; Intel's SSE is only 128-bits wide for packed floating point operations. Each time a row of the 8x8 rfp subblock is loaded on a 128-bit wide architecture, one half of the vector is useless data which will be thrown away when the rfp values are expanded to 16-bits.

#### Algorithm 2 AltiVec Add Block Fragment

```

;; unaligned vector load

v3, 0, r3

; v3: vector MSQ for initial bp0..bp7 vector

lvx

lvx

v4, r11, r3

; v4: vector LSQ

;; unaligned vector load

lvx

v0, 0, r4

; v0: vector MSQ

lvx

v1, r11, r4

; v1: vector LSQ

lvsl

v2, 0, r4

; v2: vector alignment mask for vperm

v10, v10, v10

; v10: 0

vxor

; v0: rfp: |0|1|2|3|4|5|6|7|X|X|X|X|X|X|X|X|

v0, v0, v1, v2

vperm

; v3: | bp0 | bp1 | bp2 | bp3 | bp4 | bp5 |

v3, v3, v4, v5

vperm

bp6 | bp7 |

addi

r3, r3, 16

; r3: bp += 8 (pointer to INT16)

vmrghb v1, v10, v0

; v0: | rfp0| rfp1| rfp2| rfp3| rfp4| rfp5|

rfp6| rfp7|

vaddshs v1, v3, v1

v1: bp + rfp [0..7]

; v1: rfp: |0|1|2|3|4|5|6|7|0|1|2|3|4|5|6|7|

vpkshus v1, v1, v1

stvewx v1. 0. r4

; store rfp [0..3]

; store rfp [4..7]

v1, r12, r4

stvewx

; r4: rfp += (iincr + 8) (pointer to UINT8)

add

r4, r4, r5

; move current LSQ to next \ensuremath{\mathtt{MSQ}}

v mo v

v3, v4

```

As we saw in Table 1, most multimedia kernels are either unlimited/limited or have most often have an exact required

width of 128-bits. The remaining exact native widths (64-, 88- and 512-bits) came up only once each. Thus, we consider a total vector length of 128-bits to be best.

Number of Registers Multimedia applications (and their kernels) can generally take advantage of quite large register files. Not coincidentally, MicroUnity's dedicated media processor chip has a  $64 \times 64$ -bit register file, which can also be accessed as  $128 \times 32$ -bits [Hans96], while the Philips Trimedia TM-1 has a  $128 \times 32$ -bit register file [Rath96].

As an example of where large numbers of registers are useful in our workload, consider the DCT and IDCT kernels (fragments of the original codes are given in Algorithms 3 and 4). The discrete cosine transform (DCT) is the algorithmic centerpiece to many lossy image compression methods. It is similar to the discrete Fourier transform (DFT) in that it maps values from the time domain to the frequency domain, producing an array of coefficients representing frequencies [Kien99]. The inverse DCT maps in the opposite direction, from the frequency to the time domain.

#### Algorithm 3 DCT

```

extern FLOAT64 c[8][8]; /* transform coefficients */

INT16 block[8][8]; FLOAT64 sum; FLOAT64 tmp[8][8];

for (INT32 i=0; i<8; i++)

for (int j=0; j<8; j++) {

sum = 0.0;

for (int k=0; k<8; k++)

sum += c[j][k] * block[i][k];

tmp[i][j] = sum;

}</pre>

```

#### Algorithm 4 Inverse DCT - only row computation shown

```

INT32 x0,x1,x2,x3,x4,x5,x6,x7,x8

x7 = x8 + x3;

x8 -= x3;

x3 = x0 + x2;

x0 -= x2;

x2 = (181*(x4+x5)+128)>>8;

x4 = (181*(x4-x5)+128)>>8;

```

A 2D DCT or IDCT is efficiently computed as 1D transforms on each row followed by 1D transforms on each column and then scaling appropriately. A SIMD approach requires that multiple data elements from several iterations be operated on in parallel for the greatest efficiency. This is straightforward for the 1D column DCT, since the corresponding elements of each loop iteration are adjacent in memory (assuming a row-major storage format). A 1D row DCT is more problematic since the corresponding elements of adjacent rows are not. A matrix transposition (making corresponding "row" elements adjacent in memory), then performing the desired computation, and transposing the matrix back again (to put the resulting data back in the correct configuration) can be an effective way to compute the 1D row step of a 2D transform. However, this was only of performance benefit for those architectures whose register files were able to hold the entire 16-bit 8x8 matrix at once. Since the DCT and IDCT both operate on 8x8 2D matrices of 16-bit signed values, they require at least 16 64-bit registers, or 8 128-bit registers.

#### 5.2 Data Types

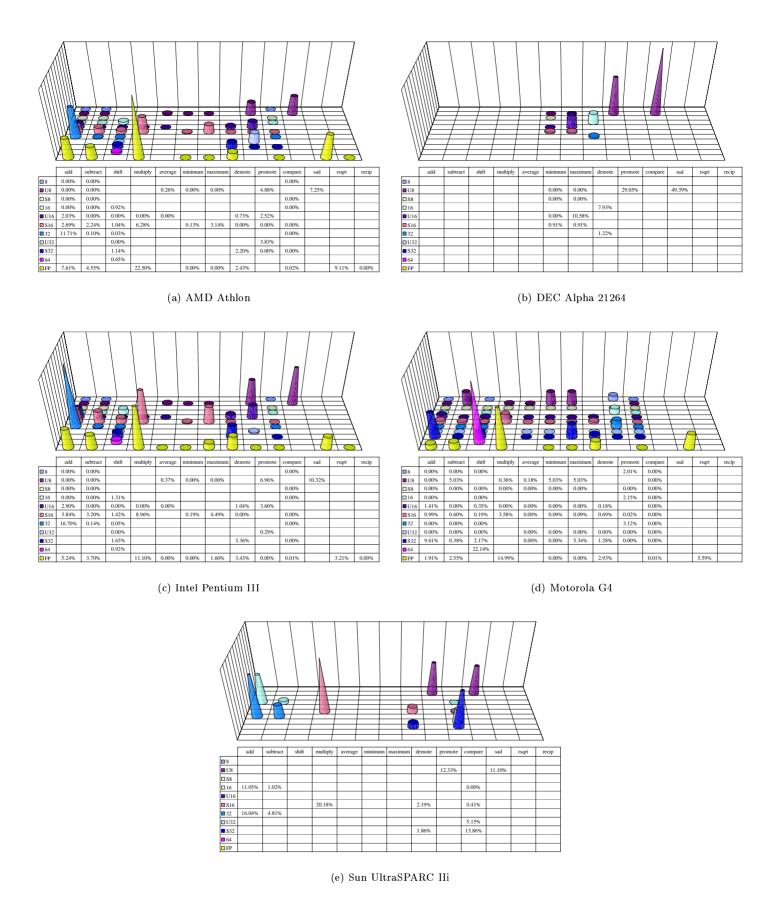

The data types supported by the different multimedia instruction sets include {signed, unsigned} {8, 16, 32, 64} bit values, as well as single precision floating point. Most of the instruction sets do not support all of these types, and usually only a subset of operations on each. In order to determine which data types and operations are useful, we broke down the dynamic SIMD instruction counts on each architecture in two ways: 1) data type distribution per instruction class (e.g. add, multiply) and 2) data type distribution per kernel. Tables of these categorizations are available in the Appendix.

In general, the video and imaging kernels (add block, block match, color space, DCT, IDCT, subsample horizontal, subsample vertical) utilize 8- and 16-bit operations. Audio kernels (FFT, max val, mix stereo, quantize, short term analysis filtering, short term synthesis filtering, synthesis filtering) either use 16-bit values or floating point, while the 3D kernels (clip test, transform) are limited almost exclusively to floating point.

**Integer** Although image and video data is typically stored as packed unsigned 8-bit values, intermediate processing usually requires precision greater than 8-bits. Other than for width promotion, most 8-bit functionality is wasted on our set of multimedia kernels. In general, storage data types (how data is stored in memory or on disk), although narrow and therefore potentially offering the greatest degrees of parallelism, are simply too narrow for intermediate computations to occur without overflow. A few operations inherently produce results that can not overflow the input data type. For example, although an N-bit average operation internally utilizes N+1 bits of precision to sum its two operands, the result is rounded and shifted back to N-bits before being stored to a register. Other operations such as the sum of absolute differences (SAD) produce a scalar result which fits in a destination register of the same width as the packed operands or a scalar register.

The signed 16-bit data type is the most heavily used because it is both the native data type for audio and speech data, as well as the typical intermediate data type for video and imaging. On the wide end of the spectrum, 32-bit and longer data types are typically only used for accumulation and simple data communication operations such as alignment. Operations tend to be limited to addition and subtraction (for accumulation), width promotion and demotion (for converting to a narrower output data type) and shifts (for data alignment).

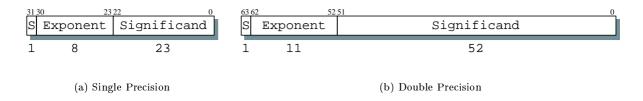

Floating Point Single precision floating point plays an important role in many of the multimedia kernels such as the geometry stage of 3D rendering (the clipping and transform kernels) and the FFT, where the wide dynamic range of floating point is required. Only Intel's recently announced SSE2 extension will offer a packed double precision data type, to be targeted at applications other than multimedia such as scientific and engineering workloads, as well as advanced 3D geometry such as is used in raytracing [Intel00a], [Intel00b].

#### 5.3 Operations

One of our primary goals is to separate useful SIMD operations from those that are not. The large differences in current multimedia instruction sets for general purpose processors are fertile ground for making such a determination because many different design choices have been made. In the Appendix we provide a table of SIMD instruction set functionality broken down per kernel, the important points of which we discuss here. Our analysis assumes that SIMD extensions are targeted solely at the domain of multimedia applications. In some cases, the targeted applications during the design of a multimedia extension included DSP applications and others which are not reflected in the Berkeley multimedia workload.

#### 5.3.1 Arithmetic

Modulo/Saturation Modulo arithmetic "wraps around" to the next representable value when overflow occurs, while saturating arithmetic clamps the output value to the highest or lowest representable value for positive and negative overflow respectively. Saturating arithmetic is useful both because of its desirable aesthetic result in pixel based computations (video and imaging) as well as the fact that it allows for overflow in multiple packed elements to be dealt with efficiently. When adding pixels, modulo addition is undesirable since if overflow occurs a small change in operand values may result in a glaring visual difference (e.g. adding two white pixels results in a black pixel). If overflow within packed elements were to be handled similar to traditional scalar arithmetic, an overflowing SIMD operation would have to be repeated and tested serially to determine which element overflowed. The added cost of saturating arithmetic is that unlike modulo operations, for which the same instruction works for both unsigned and signed (2's complement) values, saturating arithmetic necessarily requires separate instructions since the values must be interpreted by the hardware as a particular data type.

Modulo computations are important because they allow for the results of SIMD optimized codes to be numerically identical to existing scalar algorithms. This is sometimes an important consideration for the sake of compatibility and comparability. The kernels in the BMKL which employ saturating arithmetic are noted in Table 1. From this it is clear that the most important types for saturating arithmetic are unsigned 8-bit and signed 16-bit integers. The IDCT kernel clamps to a signed 9-bit range [-256..+255], which can be accomplished through a pair of max/min operations; we discuss these in more detail later. Saturating 32-bit operations are of little value since overflow is usually not a concern for such a wide data type.

**Shift** SIMD shift operations are extremely important for supporting fixed point integer arithmetic. A common sequence of operations is the multiplication of an N-bit integer by an M-bit fixed point fractional constant, producing an (N+M)-bit result, with a binary point at the  $M^{th}$  most significant bit. At the end of computation, the final result is rounded by adding the fixed point fraction representing  $\frac{1}{2}$ ,

and then shifting the sum right M-bits to eliminate the fractional bits. Shifts are important operations for all data types, and are critical for fixed point integer arithmetic, as well as providing an inexpensive way to perform multiplication and division by powers of two.

Min/Max Min and max output the minimum or maximum values of the corresponding elements in two partitioned input registers, respectively. A max instruction is clearly useful in the maximum value search kernel, which searches through an array of signed 32-bit integers for the greatest maximum absolute value in the array. Max and min instructions have other less obvious uses as well. Signed minimum and maximum operations are often used with a constant second operand to saturate results to arbitrary ranges. The IDCT kernel clips its output value range to -256...+255 (9-bit signed integer), which does not correspond to the data types supported by any of the multimedia extensions. Algorithm 5 demonstrates clamping to arbitrary boundaries for the Intel implementation of the IDCT.

#### Algorithm 5 Intel MMX/SSE IDCT

```

pmaxsw

mmO, [CLIP_MIN] ;; compute first element

mmO, [CLIP_MAX] ;; in order to free mmO

pminsw

movq

[esi

+ 0], mm0

; store x0 [0..3]

mmO, [CLIP_MIN]; clip to -256

movq

pmaxsw

mm1. mmO

pmaxsw

mm2, mm0

pmaxsw

mm3. mm0

mm4, mm0

pmaxsw

pmaxsw

mm5. mmO

mm6, mm0

pmaxsw

mm7,

pmaxsw

movq

mmO, [CLIP_MAX]; clip to +255

pminsw

mm1, mm0

mm2, mm0

pminsw

mm3, mm0

pminsw

pminsw

mm4, mm0

mm5, mm0

pminsw

mm6, mm0

pminsw

pminsw

mm7, mm0

```

Although max and min can be synthesized through simpler operations (operations which are useful in their own right), the additional execution cost is simply too great to be practical. Rather than a single independent instruction, three dependent instructions are required. An arbitrary clamping operation can also be simulated with packed signed saturating addition. The representable range of a signed fixed point number (a bits to the left of the binary point, b bits to the right) is  $-2^a \le x \le 2^a - 2^{-b}$ . For example, if we need to limit a value, X, to the range -j..+k:

- 1.  $(2^a 2^b) k \longrightarrow T_{pos}$

- 2.  $X + T_{pos \Longrightarrow X}$

- 3.  $X T_{pos} \longrightarrow X$

These three steps limit X to +K. (A  $\Longrightarrow$  represents saturating overflow, where as a  $\longrightarrow$  symbolizes modulo overflow.) Three more operations are required to limit X to the desired floor value:

1.

$$-2^a + j \longrightarrow T_{neg}$$

```

2. X + T_{neg} \Longrightarrow X

```

3.

$$X - T_{neg} \longrightarrow X$$

Architecturally, the implementation cost of max and min instructions should be low since the necessary comparators must already exist for saturating arithmetic. The only difference is that instead of comparing to a constant, a register value is used instead. An added advantage that we have found is that in many cases where comparisons are required, max and min instructions are sufficient.

Comparisons We have found that integer control flow instructions (e.g. packed comparisons) are seldom needed, except on architectures without max/min operations (e.g. Sun's VIS). We found one instance where a specialized floating point comparison was useful. In the project and clip test kernel, 3D objects are first mapped to 2D space through a matrix multiplication of 1x4 vectors and 4x4 matrices. Objects are then clipped to the viewable area to avoid unnecessary rendering. The code fragment listed in Algorithm 6 is computed for each vertex in a 3D scene every time a frame is rendered.

#### Algorithm 6 Clip Test and Project

```

FLOAT32 ex = vEye[i][0], ey = vEye[i][1], ez = vEye[i][2], ew = vEye[i][3];

FLOAT32 cx = m0 * ex + m8 * ez, cy = m5 * ey + m9 * ez;

FLOAT32 cz = m10 * ez + m14 * ew, cw = -ez;

UINT8 mask = 0;

vClip[i][0] = cx; vClip[i][1] = cy; vClip[i][2] = cz; vClip[i][3] = cw;

if (cx > cw) mask |= CLIP_RIGHT_BIT;

else if (cx < -cw) mask |= CLIP_LEFT_BIT;

if (cy > cw) mask |= CLIP_TOP_BIT;

else if (cy < -cw) mask |= CLIP_BOTTOM_BIT;

else if (cz < -cw) mask |= CLIP_BETT_BIT;

else if (cz < -cw) mask |= CLIP_BETT_BIT;

else if (cz < -cw) mask |= CLIP_BETT_BIT;

```

Motorola's AltiVec includes a specialized comparison instruction, vcmpbfp, which deals with boundary testing. This is done by testing all of the clip values in parallel to see if any clipping is needed, and branching to act as a fast out if no clipping is necessary. This technique is extremely effective because no clipping is the common case, with most vertices within the screen boundaries. An example of this is shown in the clip test kernel from Mesa's 3D rendering pipeline (Algorithm 6). For the Mesa "gears" application, the fast out case held true for 61946 of the 64560 (96.0%) clipping tests performed in our application run of 30 frames rendered at 1024x768 resolution.

Sum of Absolute Differences A sum of absolute differences (SAD) instruction operates on a pair of packed 8-bit unsigned input registers, summing the absolute differences between the respective packed elements in two registers and placing (or accumulating) the scalar sum in another register. The block match kernel is the only one in which sum of absolute differences (SAD) instructions is used. Algorithm 8 lists the core lines of the block match kernel utilized by MPEG-2 encoding. Block match sums the absolute differences between the corresponding pixels of two 16x16 macroblocks. The original application code also includes three other variations on

#### Algorithm 7 Motorola G4 Clip Test and Project

```

cy | cz |

v2, v1, 3

v2:

cw | cw

vcmpbfp. v3, v1, v2

; v3: bit mask of clip comparisons

;; set cr6 to 0x2 if all test values are within boundaries

r12. 0

mcrf

cr0, cr6

COND_TRUE, 0x2, fast_out

vcmpgtsw

v4, v0, v3

; v4: > test, - mask if clipping

vcmpgtsw v5, v3, v0

; v5: < test, + mask if clipping

vand

v4, v4, v27

v5, v5, v28

vand

v4, v4, v5

; v4: | mask0| mask1| mask2| mask3|

vor

vsldoi

v5, v4, v4, 8

v4, v4, v5

vor

vsldoi

v5, v4, v4, 4

vor

v4. v4. v5

: v4:

| mask | mask | mask |

vspltb

v4, v4, 15

; v4:

| M| M|...| M| M| [O..15]

v4, 0, r5

stvebx

; store mask to mask_temp

1bz

r12, 0(r5)

; r12: mask

r15, 0(r7)

clipMask[i]

1bz

: r15:

r15, r15, r12

or

stb

; r15:

clipMask[i] |= mask

r15, 0(r7)

tmpOrMask |= mask

or

r13, r13, r12; r13:

fast out:

; r7: clipMask++ (pointer to UINT8)

addi

r7, r7, 1

r14, r14, r12; r14:

tmpAndMask &= mask

and

addic.

r3, r3, -1

; n--

bc COND_FALSE, ZERO_RESULT, loop

```

block match which compute horizontal, vertical or both horizontal and vertical interpolation before calculating the sum of absolute differences.

#### Algorithm 8 Block Match

```

UINT8 blk_1[16][16]; UINT8 blk_2[16][16]; INT32 sad=0; INT32 diff;

for(j=0; j<h; j++)

for(i=0; i<16; i++) {

if ((diff = blk_1[j][i] - blk_2[j][i])<0)

diff = -diff;

sad+=diff;

}</pre>

```

Although DEC's MVI extension is quite small (only 13 instructions), one of the few operations that DEC did include was SAD. DEC architects found (in agreement with our experience) that this operation provides the most performance benefit of all multimedia extension operations [Rubi96]. Intel's MMX, although a much richer set of instructions, did not include this operation (it was later included in both AMD's 3DNow!+ and Intel's SSE extensions to MMX). Sun's VIS also includes a sum of absolute differences instruction.

The Motorola G4 microprocessor was the only CPU in our survey which did not include some form of SAD operation, forcing us to synthesize the SAD operation from other instructions (Algorithm 9). Although Intel's SSE extension (see Algorithm 10) includes the psadbw instruction, this offers only a one cycle performance advantage when compared to the AltiVec implementation. In some ways this comparison is misleading since Intel's extension is 64-bits wide, while Motorola's is 128-bits; the question of performance should be absolute, not relative to Intel. In order to estimate the latency of a hypothetical SAD instruction for a 128-bit extension such as AltiVec, we examine the latency of this instruction on the other (64-bit) architectures:

| Processor          | Instruction | Latency:Throughput          |

|--------------------|-------------|-----------------------------|

| Intel Pentium III  | PSADBW      | 5 cycles : 1 every 2 cycles |

| AMD Athlon         | PSADBW      | 3 cycles : 1 every 1 cycle  |

| Sun UltraSPARC IIi | PDIST       | 3 cycles : 1 every 1 cycle  |

| DEC Alpha 21264    | PERR        | 2 cycles : 1 every 1 cycle  |

The latency of a 128-bit instruction would be higher than the 64-bit instructions listed in the table because this instruction requires a cascade of adders to sum (reduce) the differences between the elements. An N-bit SAD instruction (M=N/8) can be broken down into steps: 1) calculate M 8-bit differences, 2) calculate the absolute value of the differences, 3) perform  $log_2M$  cascaded summations. The architects of the 64-bit DEC MVI extension comment that a 3-cycle implementation of PERR would have been easily achievable, but in the end the architects achieved a more aggressive 2-cycle instruction [Carl97]. If a SAD operation were to be implemented in Motorola's AltiVec, we estimate it would have a latency of 4 cycles. This would certainly be a superior solution compared to the 9 cycle solution shown in Algorithm 9.

## Algorithm 9 Motorola G4 Block Match - SAD portion (starting with vmaxub instruction) takes 9 cycles

```

block #1, line #1, pixels [0..F]

block #1, line #2, pixels [0..F]

block #2, line #1, pixels [0..F]

vavgub v1, v1, v4

vertically interpolated p0..pF

; v1:

max [0..F]

vmaxub v7, v1, v4

vminub v8, v1, v4

; v8:

min [O..F]

; v7:

vsububs v7, v7, v8

abs_diffs [0..F]

vsum4ubs v31, v7, v31; v31:

SAD_O | SAD_1

SAD_2 | SAD_3

vsumsws v31, v31, v0

; v31:

0

0

0

SAD

```

# Algorithm 10 Intel Pentium III Block Match - SAD portion (starting with first psadbw instruction) takes 8 cycles

```

block #1, line #1, pixels [0..7]

;; mm1:

;; mm5:

block #1, line #1, pixels [8..F]

;; mm3:

block #1, line #2, pixels [0..7]

block #1, line #2, pixels [8..F]

;; mm4:

block #2, line #1, pixels [0..7]

;; mm2:

;; mm6:

block #2, line #1, pixels [8..F]

pavgb mm1, mm3

; mm1:

vertically interpolated p0..p7

pavgb mm5, mm4

; mm5:

vertically interpolated p8..pF

psadbw mm1, mm2

; mm1:

0 |

0 | 0 |SADO| Pixels 0..7

psadbw mm5, mm6

; mm5:

0

0 | 0 |SAD1| Pixels 8..F

0

0

SAD

paddd mm1, mm5

```

Average. In addition to compute the sum of absolute differences, half-pixel interpolation, for which MPEG-2 encoding offers three varieties, is also important; vertical interpolation is shown in Algorithms 9 and 10. Interpolation is done by averaging a set of pixel values with pixels offset by one horizontally, vertically or both. The original C MPEG-2 code first performs the interpolation, and then computes the sum of absolute differences on the result. SIMD interpolation can be performed through 8-bit unsigned average instructions (again see Algorithms 9 and 10). DEC's MVI extension does not include a packed average instruction, but a similar interpolation operation can be done by averaging the result of several SAD operations using scalar integer arithmetic (since the result of a SAD instruction is a scalar value).

Integer average operations were only used in the block match kernel. This kernel operates on 8-bit unsigned values, so this is the only type of "average" instruction that was useful within our workload.

High Latency Function Approximation. Applications such as 3D rendering have kernels which use floating point mathematical functions, such as reciprocal and squareroot, that are very high latency. On some architectures these scalar functions are computed in software, while others have hardware instructions. Full IEEE compliant operations return 24-bits of mantissa. The computation of these functions is iterative, so the number of bits of precision returned is directly proportional to an operation's latency. It is for this reason that all of the SIMD floating point extensions (AMD's 3DNow!, Intel's SSE and Motorola's AltiVec) include approximation instructions for  $\frac{1}{x}$  and  $\frac{1}{\sqrt{x}}$ . These are typically implemented as hardware lookup tables, returning k-bits of precision. In Intel's SSE, for example, approximate reciprocal (rcp) and reciprocal square root (rsqrt) return 12-bits of mantissa. Motorola's AltiVec also returns 12-bits of precision for both the reciprocal and reciprocal square root approximation instructions.

In the transform and normalize kernel, graphics primitives are transformed to the viewer's frame of reference through matrix multiplications. The code shown in Algorithm 11 is computed for each vertex in a 3D scene.

#### Algorithm 11 Transform and Normalize

```

FLOAT64 tx, ty, tz, len, scale;

FLOAT32 ux = u[i][0], uy = u[i][1], uz = u[i][2];

tx = ux * m[0] + uy * m[1] + uz * m[2];

ty = ux * m[4] + uy * m[5] + uz * m[6];

tz = ux * m[8] + uy * m[9] + uz * m[10];

len = sqrt( tx*tx + ty*ty + tz*tz );

scale = (len>1E-30) ? (1.0 / len) : 1.0;

v[i][0] = tx * scale;

v[i][2] = tz * scale;

```

The transform kernel has at its heart a floating point reciprocal square root operation  $(\frac{1}{\sqrt{x}})$ . One unique aspect of Intel's SSE instruction set is that not only does it include 22-bit precise (mantissa) approximations of  $\frac{1}{x}$  and  $\frac{1}{\sqrt{x}}$ , but it also includes full precision (24-bits of mantissa) versions of division and  $\sqrt{x}$ . Of course, this added precision comes at a price - namely much higher latency (their full precision instructions are not pipelined) than the pipelined 22-bit approximations derived from processor internal lookup tables. All of the floating point multimedia extension vendors, including Intel, point out the Newton-Raphson method for improving the accuracy of approximations through specially derived functions. In the case of  $\frac{1}{\sqrt{x}}$  it is possible to iteratively increase the precision of an initial approximation through the equation:

$$x_1 = x_0 - (0.5 \cdot a \cdot x_0^3 - 0.5 \cdot x_0) = 0.5 \cdot x_0 \cdot (3.0 - a \cdot x_0^2) \tag{1}$$

Employing an approximation instruction in conjunction with the Newton-Raphson method to achieve full precision is actually faster than the full precision version of the instruction that Intel provides. Compare the code fragments in Algorithms 12 and 13, which have execution times of 25 vs.

36 cycles. One iteration of the Newton-Raphson method is enough to improve a 22-bit approximation to the full 24-bit precision of IEEE single precision.

## Algorithm 12 Intel Approximated Square Root - 25 cycles

```

xmm3:

tx^2+ty^2+tz^2 [0..3] (len=sqrt(tx^2+ty^2+tz^2))

; xmm7:

0.5 [0..3]

3.0 [0..3]

: xmm5:

xmm4, xmm3

rsqrtps

; xmm4:

rsqrtps(a)

xmm6. xmm3

movaps

: xmm6:

xmm6, xmm4

a*rsgrtps(a)

mulps

xmm6:

xmm6, xmm4

a*rsgrtps(a)*rsgrtps(a)

mulps

0.5*rsqrtps(a)

xmm4, xmm7

: xmm4:

mulps

xmm5:

3.0 - a*rsgrtps(a)*rsgrtps(a)

subps

xmm5, xmm6

|1/len1|1/len2|1/len1|1/len0|

mulps

xmm4, xmm5

xmm4:

;; sqrt(a) = a*(1/sqrt(a))

xmm3, xmm4

| len3 | len2 | len1 | len0 |

mulps

: xmm3:

```

## Algorithm 13 Intel Full Precision Square Root - 36 cycles

The added cost of the Newton-Raphson method is of the additional register space needed to hold intermediate values and constants. AMD's 3DNow! extension circumvents this by including instructions to internally perform the Newton-Raphson method, rather than having the programmer implement it (Algorithm 14). The only odd thing about AMD's reciprocal square root instructions are that they are actually scalar; they only produce one result value, based on the lower packed element.

## **Algorithm 14 AMD Approximated Square Root** - 20 cycles

```

; mm3:

tx^2+ty^2+tz^2 [0]

(len=sqrt(tx^2+ty^2+tz^2))

pfrsqrt

mm4, mm7

. mm4: |~1/len0 |~1/len0 |

movq

mm5, mm4

pfmul

mm4, mm4

pfrsqit1

mm4, mm7

pfrcpit2

; mm4: | 1/len0

1/len0

mm4, mm5

; mm7: |

pfmul

mm7, mm4

len0

len0

```

#### 5.3.2 Exceptions

Techniques for handling exceptions that occur during SIMD processing are very similar to those employed when dealing with packed overflow. Checking result flags or generating an exception from a packed operation requires considerable time to determine which packed element caused the problem. In most cases where an exception might be raised it is possible to fill in a value which will give reasonable results for most applications. This speeds execution because no error condition checking need be done, and is is similar to saturating integer arithmetic where maximum or minimum result values are substituted rather than checking for and reporting positive or negative overflow. Both AMD's 3DNow! and Motorola's AltiVec extensions do not implement IEEE compliant floating point exceptions. Only Intel's SSE implements

full IEEE compliant SIMD floating point exceptions, and includes a control/status register (MXCSR) to mask or unmask packed floating point numerical exceptions.

#### 5.3.3 Floating Point Rounding

Intel's SSE offers two modes of rounding: IEEE compliant and another, faster, flush to zero (FTZ) mode. Flush to zero (FTZ) clamps to a minimum representable result in the event of underflow (a number too small to be represented in single precision floating point). Fully compliant IEEE floating point supports four rounding modes. Most real time 3D applications use the FTZ rounding mode since they are not particularly sensitive to a slight loss in precision [Thak99]. 3DNow! supports only truncated rounding (round to zero). All of Motorola's AltiVec floating point arithmetic instructions use the IEEE default rounding mode of round to nearest. The IEEE directed rounding modes are not provided.

#### 5.3.4 Type Conversion

Width promotion is the expansion of an N-bit value to some larger width. For unsigned fixed point numbers this requires zero extension or filling any additional bits with zeros. Zero extension is usually not specified as such in a multimedia architecture because it overlaps in functionality with data rearrangement instructions such as unpack or merge. If packed values are merged with another register which has been zeroed prior to merging the result is zero extension. Signed element unpacking is not as simple, but is rarely supported directly by hardware; only the AltiVec instruction set includes it. It can be synthesized with multiplication by one since a multiplication yields a result that is the overall width of both its operands.

Video and imaging algorithms use an 8-bit unsigned data type. Audio and speech algorithms, on the other hand, typically employ signed 16-bit values, but because multiplication by a fractional fixed point constant is a common operation, these values are often unpacked as a natural consequence of computation. So, although a signed unpack operation would likely be faster than multiplication by 1, it is seldom necessary to resort to this in practice.

All data types that occur in multimedia should be supported for packing and unpacking even for those widths not directly supported by arithmetic operations. It should always be possible to convert to a width that is supported for computation. Although we do not otherwise examine HP's MAX-1/MAX-2 extensions, as no hardware employing them was available to us at the time of this work, they are good examples of where not following this guidline can cause problems. We have noted the importance of the 16-bit data width. HP's MAX-1/MAX-2 instruction sets only support operations on 16-bit wide values. Partitioned 8-bit operations were considered, but rejected due to insufficient precision. Wider packed data types (e.g. 32-bit) were not included due to insufficient parallelism. What this approach overlooks is that fact that even though many intermediate computations require greater precision than 8-bits, many types of video and imaging data are stored this way in existing multimedia file formats. Thus, packing and unpacking to and from 8-bit precision is a very common operation, which is not supported in hardware, making HP's extensions inefficient at processing this type of data.

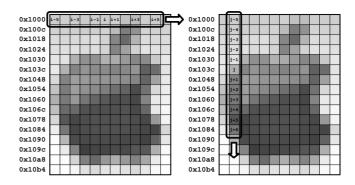

#### 5.3.5 Data Rearrangement

SIMD instructions perform the same operation on multiple data elements. Because all of the data within a register must be treated identically, the ability to efficiently rearrange data bytes within and between registers is critical for performance. We will refer to these types of operations as "data communication" instructions. Interleave instructions (also referred to as mixing, unpacking or merging) merge alternate data elements from the upper or lower half of the elements in each of two source registers. Align or rotate operations allow for arbitrary byte-boundary data realignment of the data in two source registers; essentially a shift operation that is done in multiples of 8-bits at a time. Both interleave and align type operations have hard coded data communication patterns. *Insert* and extract operations allow for a specific packed element to be extracted as a scalar or a scalar value to be inserted to a specified location. Shuffle (also called permute) operations allow greater flexibility than those operations with fixed communication patterns, but this added flexibility requires that the communication pattern be specified either in a third source register or as an immediate value in part of the instruction encoding.

The sufficiency of simpler data communication operations is to some degree dependent on the vector length employed. For example, 128-bit AltiVec vectors contain up to sixteen elements, while a shorter extension such as Intel's 64-bit MMX contain at most eight of the same type of element. This means that simple data rearrangement operations (e.g. merge) cover a relatively larger fraction of all possible mappings in the case of the shorter vector length. [Lee00] presents a novel set of simple data communication primitives which can perform all 24 permutations of a 2x2 matrix in a single cycle on a processor with dual data communication functional units. This is useful because any larger data communication problem can be decomposed into 2x2 matrices. Although this approach might make some very complex data communication patterns slow to compute, we have found that most multimedia algorithms have patterns which are relatively simple. Because of this we endorse [Lee00]'s technique for covering the data communication needs of multimedia applications.

A related class of instructions that the AltiVec extension included, that was quite useful, was a set of "splat" instructions, which place either an immediate scalar or specified element from a source register into every element of the destination register. This was very useful when constants were required; on other architectures it is necessary to statically store these types of values in memory, and then load them to a register when required.

#### 5.3.6 Prefetching

Prefetching is a hardware or software technique which tries to predict data access needs in advance, overlapping memory access with useful computation. Although we will not otherwise examine the performance implications of prefetch instructions (which would be a useful extension to this study), we mention them briefly because they are often a part of multimedia instruction sets due to the highly predictable nature of data accesses in multimedia applications.

Software prefetch instructions are used to fetch data into the cache from main memory without blocking true load/store instruction accesses. Determining the ideal location for prefetch instructions in a piece of code depends on many architectural parameters. Unfortunately, these include such things as the number of CPU clocks for memory latency and the number of CPU clocks to transfer a cache line, which are both highly machine dependent and not readily available to the programmer.

Rather than issuing an explicit prefetch instruction for each desired data prefetch, Motorola's AltiVec uses a single data stream touch instruction (dst) which indicates the memory sequence or pattern that is likely to be accessed. We will refer to this hybrid of hardware and software prefetching as software directed prefetching to indicate that a separate prefetch instruction need not be issued for each data element. A data stream is defined by a sequence starting address, size of each unit (up to 32 128-bit blocks), total number of units (up to 256), bytes between units (-32768..+32767) and a 2-bit ID tag for the stream. Hardware optimizes the number of cache blocks to prefetch so it is not necessary for the programmer to know the parameters of the cache system. A stream is fetched either until all of the requested blocks have been brought into the cache or another dst instruction is issued with the same tag ID. The stream construct eliminates the instruction issue overhead as well as the problem of determining the optimal prefetch distance.

#### 5.4 Bottlenecks and Unnecessary Features

In this section we discuss those features which appear in multimedia instruction sets, do not appear to be useful, and are not "free"; i.e. they aren't a low (or no) cost side effect of some other useful feature.

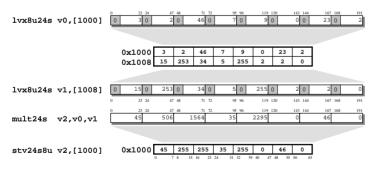

Instruction Primitives The VIS instruction set does not include full 16-bit multiply instructions. It instead offers multiplication primitives, the results of which must be combined through addition (see Algorithms 15 and 16).

# Algorithm 15 Sun VIS 16-bit x 16-bit $\rightarrow$ 16-bit Multiply

fmul8sux16 %f0, %f2, %f4 fmul8ulx16 %f0, %f2, %f6 fpadd16 %f4, %f6, %f8

The Mix stereo kernel is a good example of the high cost of synthesizing needed instruction functionality from other primitives. Audio mixing consists of multiplying a vector of

## Algorithm 16 Sun VIS 16-bit x 16-bit →32-bit Multi-

```

fmuld8sux16

%f0.

%f2, %f4

%f2, %f6

fmuld8ulx16

%f0.

fpadd32

%f4.

%f6.

%f8

```

count input signals (sp[]) by a vector of mixing coefficients  $chan_1, chan_2$  and summing the result (Algorithm 17). In the Timidity MIDI music synthesis application, fixed point integer computations are used to mix the various signed 16-bit instrument sounds into a 32-bit output buffer.

#### Algorithm 17 Mix Stereo

```

INT16 **sp_p; INT32 **lp_p; INT32 count; INT32 chan_1; INT32 chan_2;

INT16 s, *sp = *(sp_p); INT32 *lp = *(lp_p);

while (count--) {

s = *sp++;

*lp++ += s*chan_1;

*lp++ += s*chan_2;

*(sp_p) = sp;

*(lp_p) = lp;

```

Comparing the code snippet in Algorithm 18 to Algorithm 19 we can see that Sun's approach of synthesizing functionality from primitives (especially in the case of synthesizing a 16-bit merge) is much more costly than using a single instruction.

#### Algorithm 18 Intel Mix

```

mm0, [esi]

movq

mmO:

s3

s2

s1

s0

mm1, [edi]

mm1:

lp1

1p0

movq

movq

mm2, [edi +

mm2:

1p3

1p2

pshufw

mm5, mm0, 00000000b

mm5:

] s0

s0

s0

:

pshufw

mm6, mm0,

01010101b

mm6:

s1 |

s1

s1

s1

mm5:

pmaddwd mm5, mm7

s0*right

s0*left

pmaddwd mm6, mm7

mm6:

s1*left

s1*right

lp1'

1p0'

paddd

mm1, mm5

; mm1:

1p3'

paddd

mm2:

1p2

mm2,

```

The reason that the architects of VIS divided up 16-bit multiplication in this way was to decrease die area. Not providing a full 16x16 multiplier subunit cut the size of the arrays in half [Trem96b]. Unfortunately, dividing an operation into several instructions (which are not otherwise useful in and of themselves) increases register pressure, decreases instruction decoding bandwidth and creates additional data dependencies. Splitting SIMD instructions (which have been introduced for their ability to extract data parallelism) can actually cripple a superscalar processor's ability to extract instruction level parallelism. A multi-cycle operation can be a better solution than a multi-instruction operation because instruction latencies can be transparently upgraded in future processors, while poor instruction semantics can not be repaired without adding new instructions.

#### Unused High Latency Approximation Instructions

Floating point approximation of  $\frac{1}{x}$  instructions, although available on several platforms, did not find application in any of the kernels we studied. AltiVec also includes approximate  $log_2$  and  $exp_2$  instructions, which find application in the lighting stage of a 3D rendering pipeline; this is currently handled by 3D accelerator cards, and not the CPU.

```

Algorithm 19 Sun Mix

%g0,

%gsr

!set alignment for right shift by 16

0], %f16

! %f 16 : |

XXXXXXXXXX

1p0

[%11 +

4], %f17 !%f17:|

ld

1p0

lp1

ld

[%11 +

8], %f18

!%f18:

1p2

XXXXXXXXXX

[%11 + 12], %f19

1p2

1p3

simulate 16-bit merge

%f28, %f28, %f4

fpmerge

!%f4: |s0_|s0_|_s0|_s0|s1_|s1_|_s1|_s1|

fpmerge

%f29, %f29, %f10

!%f10:|s2_|s2|_s2|_s2|s3_|s3_|_s3|_s3|

faligndata %f4, %f4, %f6

!%f6: |_s1|_s1|s0_|s0_|_s0|_s0|s1_|s1_

faligndata

%f10, %f10, %f12

!%f12:|_s3|_s3|s2_|s2_|_s2|_s2|s3_|s3_|

%f6, %f4, %f8

!%f8: |XXX|XXX|XXX|XXX|

fpmerge

s0

%f12, %f10, %f14

! %f 14 : | XXX | XXX | XXX | XXX |

s2

s2

fomerge

%f7, %f5, %f2

!%f2: |XXX|XXX|XXX|XXX|

fpmerge

s1

s1

%f13, %f11, %f26

!%f26: |XXX|XXX|XXX|XXX|

s3

s3

fomerge

%f9, %f2

!%f2: | s0

s0

s1

fsrc1s

s1

fsrc1s

%f15, %f26

!%f26:|

s2 |

s2

s3

s3

simulate 16x16 -> 32-bit multiply

fmuld8sux16 %f0, %f2, %f4

fmuld8ulx16 %f0, %f2, %f6

simulate 16x16 -> 32-bit multiply

fmuld8sux16 %f0, %f3, %f8

fmuld8ulx16 %f0, %f3, %f10

fpadd32

%f4. %f6. %f4

%f4:

s0*chan1

s0*chan2

fpadd32

%f8, %f10, %f6

%f6:

s1*chan1

s1*chan2

1p0'

lp1'

```

%f16:

%f18:

1p2'

1p3'

fpadd32

fpadd32

%f16, %f4,

%f18, %f6.

%f16

%f18

Unused Pixel Conversion Instructions Motorola's AltiVec extension includes pixel pack (vpkpx) and pixel unpack (vupkhpx, vupklpx) instructions for converting between 32-bit true color and 16-bit color representations. These did not find application within the BMKL, although it is possible that they might be of utility in situations where AltiVec needs to operate on 16-bit color data; many video games use 16-bit textures, for example.

Unused Memory Access Instructions Sun's VIS includes two sets of instructions for accelerating multimedia operations with sophisticated memory addressing needs. The first, edge8, edge16, and edge32, produce bit vectors to be used in conjunction with partial store instructions to deal with the boundaries in 2D images. The second group of addressing instructions include array8, array16 and array32 which find use in volumetric imaging (the process of displaying a two dimensional slice of a three dimensional data). An array instruction converts (x, y, z) coordinates into a memory address. The Berkeley multimedia workload does not include any volumetric imaging applications, so it is unsurprising that these instructions found no utility in our workload.

Singular, Highly Utilized Resources Although we usually think of SIMD architectures as extracting data level parallelism, all of the implementations of the instruction sets we have examined are also superscalar, with multiple parallel SIMD functional units. In fact, unless the SIMD vector length is long enough to hold the entire data set being operated on, there is almost always the potential to extract instruction level parallelism as well. In coding the kernels with Sun's VIS extension, it became clear that instruction level parallelism was being compromised by the over utilized graphics status register (GSR).

Sun's VIS architecture does not include partitioned shift instructions, the GSR has a 3-bit addr\_offset field which is used implicitly for byte granularity alignment, as well

as a 4-bit scale\_factor field for packing/truncation operations. The VIS GSR is a serializing bottleneck because any time packing or alignment functionality is needed, it must be pushed through the GSR. Because VIS lacks partitioned shift operations, we found ourselves synthesizing such operations with the packing and alignment operations where no other algorithmic path was possible. Even with careful planning of packing and alignment operations it was often necessary to write to the GSR several times in each iteration of the loops of our multimedia kernels. The serializing effect of this singular resource prevented VIS operations from proceeding at the fullest possible degree of parallelism.

#### 5.5 Alignment and Memory Traffic

Factors such as register file geometry (the number of registers and their width), data path location (pre-existing integer or floating point, or separate) and alignment issues are reflected in the uncached memory traffic - the data accesses as seen by the L1 data cache. Table 3 lists the average number of bytes loaded or stored per function call. This was computed by multiplying the number of dynamic load and store instructions executed by their widths in bytes.

From Table 3 we can see that Motorola's and Sun's implementations sometimes seem to transfer (load and store) more bytes in each function call than the AMD, DEC or Intel implementations of the same kernel. We would expect the Motorola and Sun implementations to spill registers to memory less frequently due to their larger register files (on average we see that the register file geometry does affect memory traffic as we might expect). This surprising result is actually an artifact of how we computed memory traffic, rather than an indication of an architectural shortcoming. Dynamic instruction counts alone are not a completely accurate predictor of actual memory traffic, since some of the architectures (AMD, DEC, Intel) support unaligned loads (hiding some loads issued by the hardware which handles unaligned memory access in the CPU) and the rest do not. Hardware support to efficiently handle memory accesses that are not aligned are expensive in both area and timing [Thak 99].

Transparently Forced Alignment The AltiVec instruction set architecture does not provide for alignment exceptions when loading and storing data. Alignment is maintained by forcing the lower four bits of any address to be zero. This is transparent to the programmer, so the programmer is responsible for guaranteeing alignment, otherwise incorrect data may be loaded or stored. We believe it is better that performance and correctness issues due to alignment be made explicit. The loading of incorrect data due to a mistaken assumption about alignment would be an extremely difficult bug to track down.

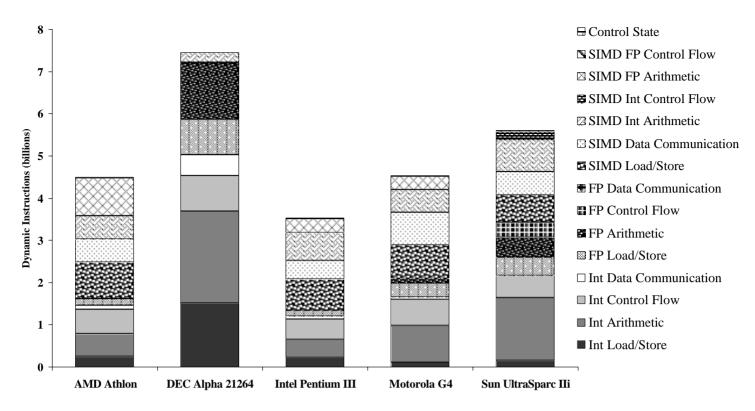

#### 5.6 Overall Instruction Mix

Table 4 shows what types of instructions comprised the total mix of dynamic instructions executed by each architecture. Counts are for the code within the kernels only, and do not include instructions from the rest of each application. Control state instructions are those which interact with special purpose machine registers (e.g. the GSR on Sun's VIS). Branches and other data dependent codes such as conditional moves are categorized as "control flow" type instructions.

We can see that SIMD kernels utilize a significant number of scalar operations for pointers, loop variables and clean up code; evidence that sharing the integer data path is not a good idea. Intel's SSE is a 128-bit wide extension, as compared to AMD's 64-bit wide 3DNow!, explaining why Intel's overall instruction count is lower by about 1 billion instructions. The same reasoning applies to Motorola's G4 which has the 128-bit wide (both packed integer and floating point) AltiVec extension. DEC's bloated instruction count is due to the fact that their MVI extension is very limited in functionality (13 instructions in total), and so many operations need to be done with scalar instructions.