## An Obstacle-Avoiding Router for Custom VLSI

Ву

## Gordon Taro Hamachi

A.B. (University of California) 1977 M.S. (University of California) 1982

#### DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of DOCTOR OF PHILOSOPHY

in

Computer Science

in the

GRADUATE DIVISION

OF THE

UNIVERSITY OF CALIFORNIA, BERKELEY

Approved: Approved: 1/23/86.

Chairman Who Date 4/23/86

Chaile Works 4/23/86

# An Obstacle-Avoiding Router for Custom VLSI

Gordon Taro Hamachi

#### Abstract

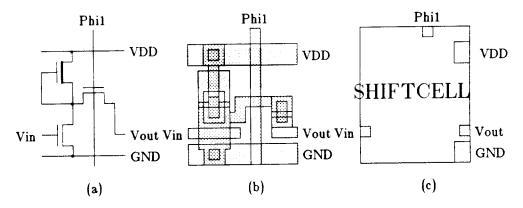

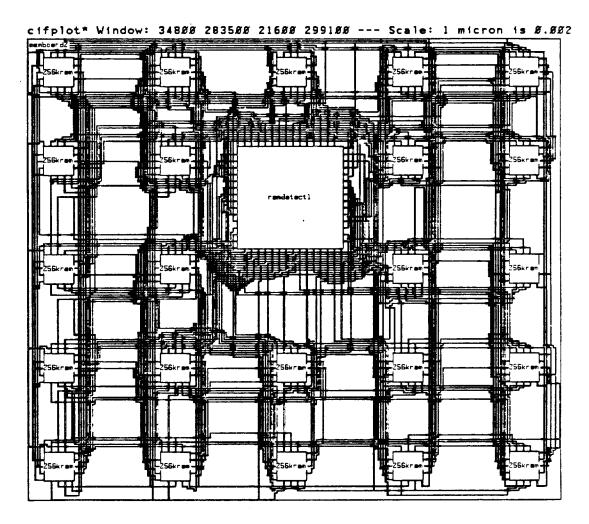

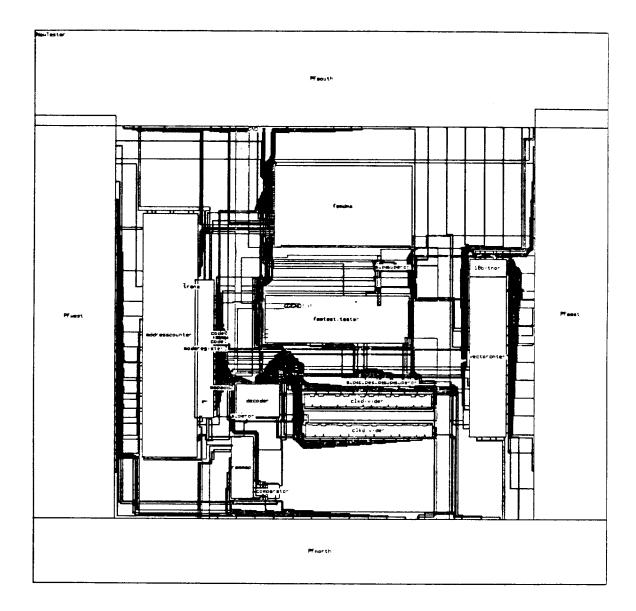

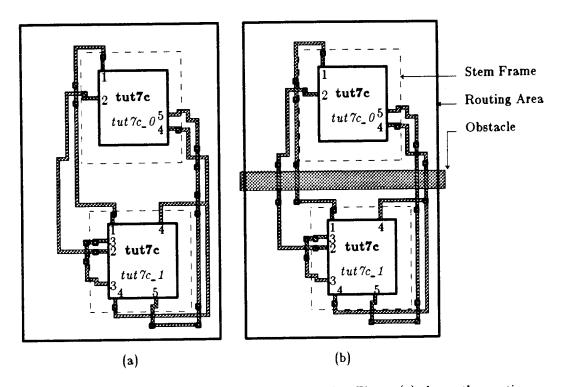

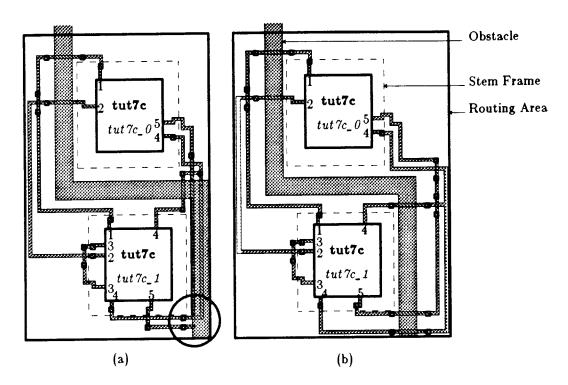

Magic's automatic routing system combines the flexibility of hand-routing with the speed and quality of automatic channel routers, by allowing chip designers to prewire selected nets by hand. The router then works around this previously-placed layout, called obstacles, to automatically wire the remaining nets. This ability to partially hand-route an integrated circuit gives designers complete control over critical paths, power and ground routing, and other special nets. At the same time the router provides a fast way to make the remaining connections in the design.

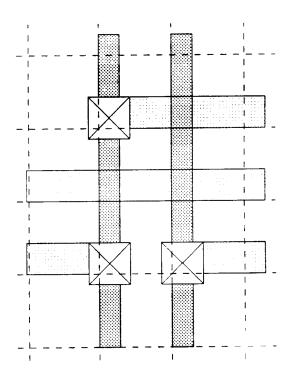

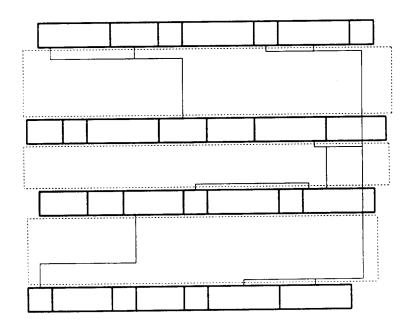

The system's novel features include a fast channel decomposer, an obstacle-avoiding global router, and an obstacle-avoiding switchbox router. The router's channel decomposition algorithm relies on a corner-stitched data structure to efficiently produce a small number of large channels. The global router considers obstacles during path generation, trading-off net length and channel complexity to simplify the subsequent channel routing task. While able to cope with obstacles, Magic's switchbox router is still comparable to the best traditional (non-obstacle-avoiding) channel routers.

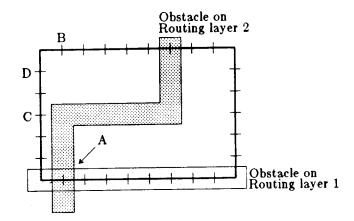

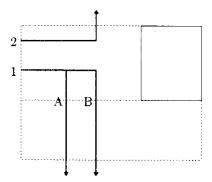

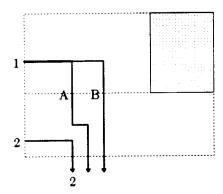

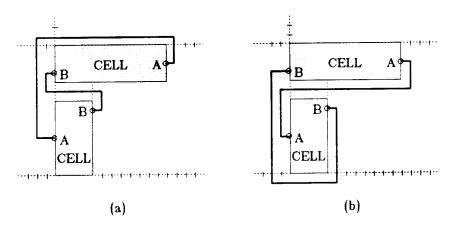

The router's obstacle-avoidance features rely on two underlying concepts: (1) a preferred direction for crossing an obstacle, and (2) hazards, or areas the routing should avoid. Crossing obstacles in the preferred direction minimizes the creation of blocked areas, which can not be crossed by other routing; this minimizes obstacles' impact on the automatic routing. Crossings in preferred directions are controlled by strategically-placed hazards adjacent to obstacles.

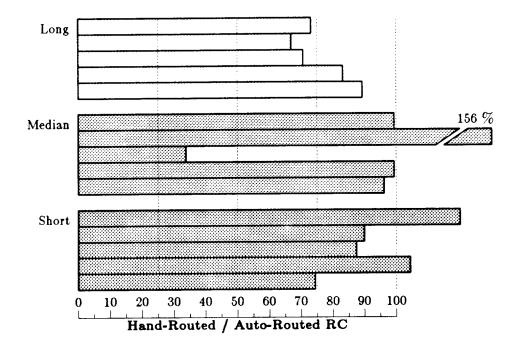

Measurements show that obstacle-avoiding routing is both useful and practical: hand-routing improves the electrical characteristics of the selected nets, while the hand-routed obstacles have only minor effects upon the routing quality of a design as a whole. The improvement in electrical characteristics is due to the decreased net length and increased attention to layer selection possible when nets are prewired by hand.

John K. Dithu

# Dedication

In memory of Arnold Philip Tapie

### Acknowledgements

Special thanks to John Ousterhout, who stresses the value of stating the most important ideas first. In his typical style, John comes very close to being the ideal research advisor. Working with him has been a very rewarding experience.

I would like to acknowledge a number of others for their technical assistance. First, it has been a great pleasure to work with the other members of the Magic group: Robert Mayo, Walter Scott, and George Taylor. Thanks to the many other tool builders for making my job easier, especially Michael Arnold, Dan Fitzpatrick, Howard Landman, and Barry Roitblat. Randy Katz served on my qualifying exam committee and provided valuable guidance. As members of my thesis committee, Alberto Sangiovanni-Vincentelli and Charles Woodson read several drafts of my dissertation and provided helpful and insightful comments on its content, organization, and presentation. Fred Obermeier and David Wallace also reviewed drafts of this thesis. David Patterson and Carlo Séquin supervised my academic progress and research early in my career as a graduate student. Franky Leung and David Ashkenas designed the chips used to debug the router and measure its performance.

Finally, I would like to express my gratitude to several persons for their important personal support and encouragement. I am indebted to my parents, Ted and Alice, who designed and fabricated me. Similar thanks to my brothers and sisters--Karolyn, Warren, Margaret, and Ken--who tested me. Thanks also to Dale Beucler, Scott Evans, David Spears, Lewis Yee, and Alan Yung, for their enduring friendship.

The work described here was supported in part by SRC under grant number SRC-82-11-008.

# Table of Contents

## CHAPTER 1. Introduction

| CH          | APTER 2. Approaches to the Routing Problem                                 | _   |

|-------------|----------------------------------------------------------------------------|-----|

| 2.1         | Introduction                                                               | 9   |

| 2.2         | Net-At-A-Time Routers                                                      | 10  |

|             | 2.2.1 The Lee Router                                                       | 11  |

|             | 2.2.2 The Hightower Router                                                 | 13  |

| 2.3         | Channel-Based Methods                                                      | 15  |

|             | 2.3.1 The Left Edge Algorithm                                              | 17  |

|             | 2.3.2 Deutsch's Dogleg Router                                              | 19  |

|             | 2.3.3 Yoshimura and Kuh                                                    | 20  |

|             | 2.3.4 YACR-II                                                              | 21  |

|             | 2.3.5 Burstein's Hierarchical Router                                       | 21  |

|             | 2.3.6 Rivest's Greedy Router                                               | 22  |

| 2 1         | Lack of Flexibility                                                        | 23  |

| 2.4         | Dack of Fickionity                                                         |     |

| СН          | APTER 3. Magic's Obstacle-Avoiding Router                                  |     |

| 3.1         | Introduction                                                               | 25  |

| 3.2         | Magic's Obstacle-Avoiding Router                                           | 25  |

| 3.2         | Obstacles and Hazards                                                      | 27  |

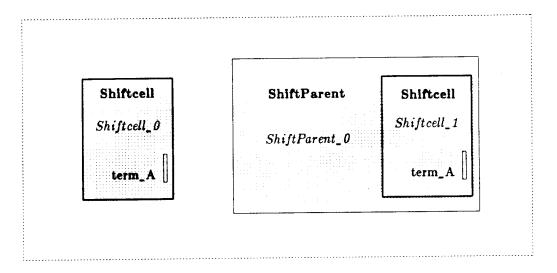

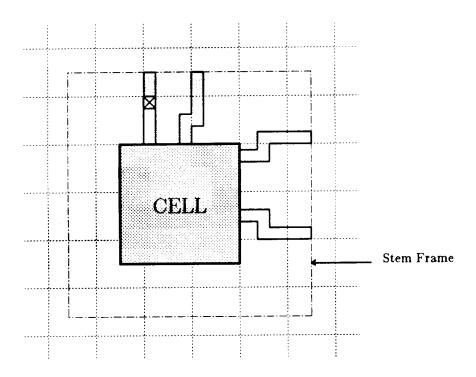

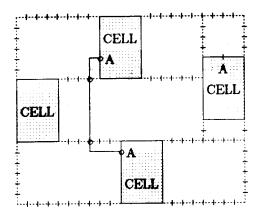

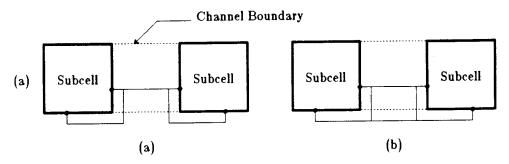

| 3.4         | Hierarchical Terminals                                                     | 31  |

| 2.5         | Netlists                                                                   | 32  |

| 2.0<br>2.8  | Automatic Grid Alignment                                                   | 33  |

| 0.0         | A Fast Channel Decomposer                                                  | 34  |

| ა. <i>(</i> | Magellan: An Obstacle-Avoiding Global Router                               | 34  |

| 3.8         | Detour: An Obstacle-Avoiding Channel Router                                | 35  |

| 3.9         | ) Visual Feedback                                                          | 3.  |

| 3.10        | Visual Feedback                                                            | 3.5 |

| 3.11        | 1 Technology Independence                                                  | 0   |

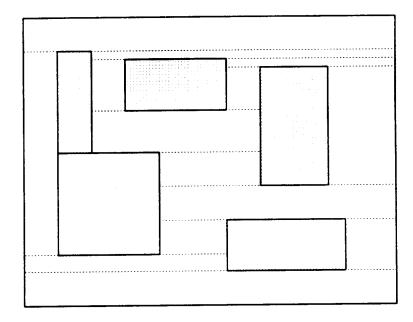

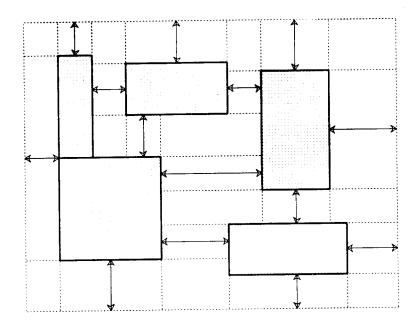

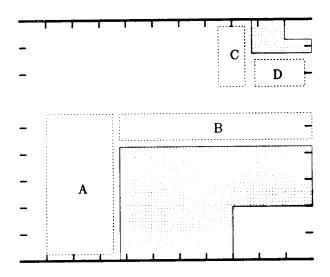

| CH          | APTER 4. Channel Decomposition                                             |     |

| 4.1         | Introduction                                                               | 37  |

| 1.1         | Background                                                                 | 38  |

| 4.2         | 4.2.1 VTI's Maximal Horizontal Strips                                      | 39  |

|             | 4.2.2 BBL's Bottlenecks                                                    | 39  |

|             | 4.2.3 The PI System                                                        | 4   |

| 4.9         | Channel Decomposition Algorithm                                            | 4   |

| 4.3         | Implementation                                                             | 4   |

| 4.4         | 4.4.1 Identifying Convex Corners                                           | 4   |

|             | 4.4.1 Identifying Convex Corners                                           | 4   |

|             | 4.4.2 Horizontal and Vertical Distances  4.4.3 Splitting and Merging Tiles | 5   |

|             | 4.4.3 Splitting and Merging Tiles                                          | 5.  |

|             | 4.4.4 Setting Horizontal Status Flags                                      | 5   |

|             | 4.4.5 Cutting Corners                                                      | U . |

| 4.5         | Analysis                                                                   | 0   |

| <b>~</b> T1 | A DODD F. Mariela Mariela Obstacle Avoiding Clobal Routes                  |     |

| CH          | IAPTER 5. MagellanMagic's Obstacle-Avoiding Global Router Introduction     | 5   |

| 5.1         | Global Router Overview                                                     | 50  |

| 5.2         | Global Router Overview                                                     | B   |

| 5.4           | Crossing Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64       |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

| 5.5           | The Penalty Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 07       |  |  |

|               | 5.5.1 Obstacles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68       |  |  |

|               | 5.5.2 Jog Avoidance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70       |  |  |

|               | 5.5.3 Pin Density and Corners                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72       |  |  |

| <b>5.6</b>    | Net Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13       |  |  |

| 5.7           | Multi-Pin Nets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14       |  |  |

| 5.8           | Equivalent Terminals and Feed-Throughs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70       |  |  |

| 5.9           | Loop Prevention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10<br>70 |  |  |

| 5.10          | Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70       |  |  |

| 5.11          | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70       |  |  |

| 5.12          | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19       |  |  |

| СН            | APTER 6. DetourMagic's Obstacle-Avoiding Switchbox Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |  |  |

| 8 1           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 81       |  |  |

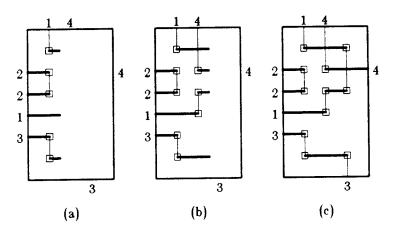

| 6.2           | The Column Sweep Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82       |  |  |

| 6.3           | Obstacle-Avoidance Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85       |  |  |

| 6.4           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86       |  |  |

| 8.5           | Hazards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88       |  |  |

| 0.0           | 6.5.1 Hazards for Obstacle-Avoidance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88       |  |  |

|               | 8.5.9 Havards for End Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89       |  |  |

| A A           | Revised Vertical Wiring Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90       |  |  |

| 6.7           | Metal Maximization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92       |  |  |

| 8 R           | Channel Rotation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 93       |  |  |

| 8 Q           | Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 93       |  |  |

| 0.5<br>R 10   | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 94       |  |  |

| 0.10          | , itosures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |  |  |

| СН            | APTER 7. Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |  |  |

| 7 1           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102      |  |  |

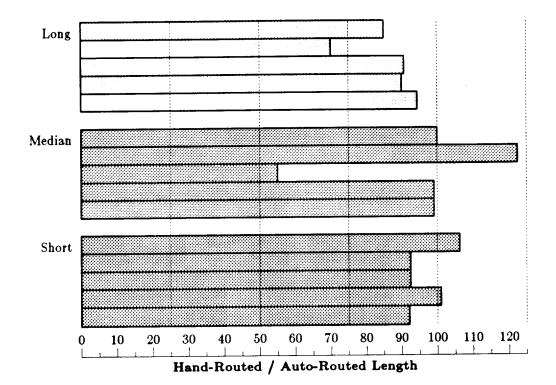

| 7.2           | Hand-Routing Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 102      |  |  |

| • • •         | 7 2 1 Net Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105      |  |  |

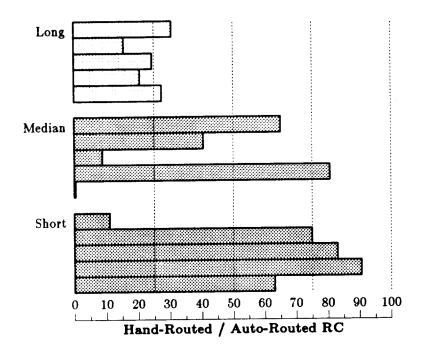

|               | 7 2 2 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107      |  |  |

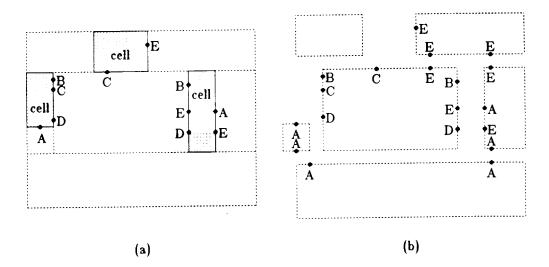

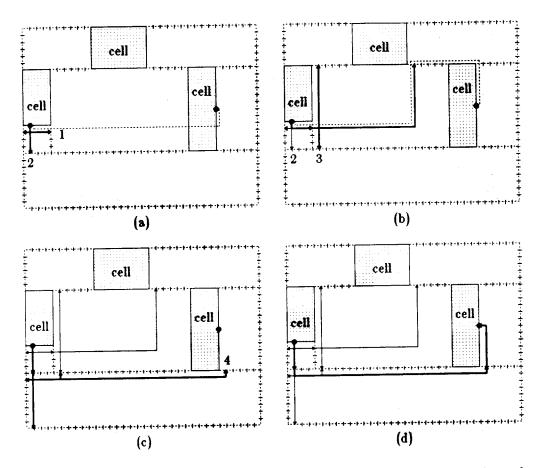

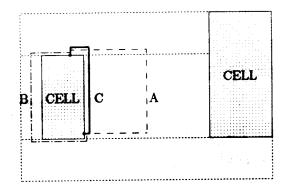

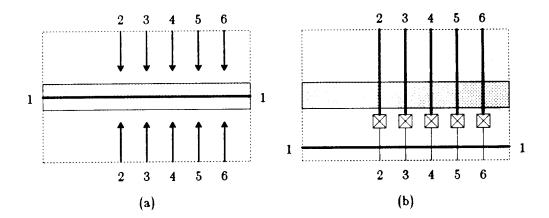

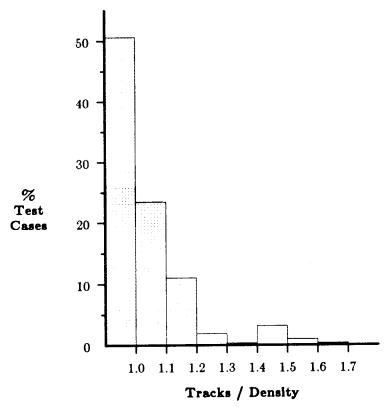

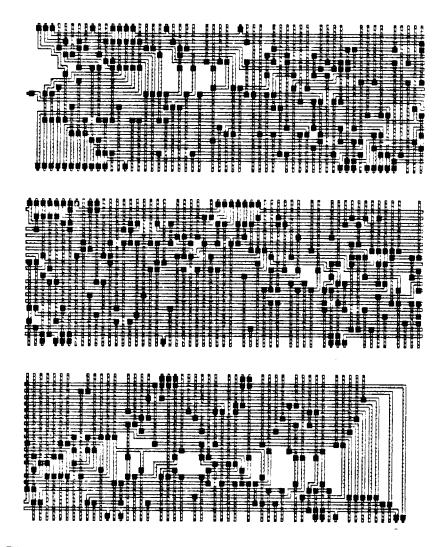

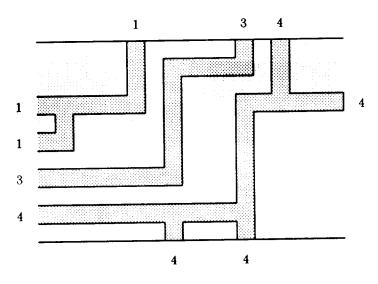

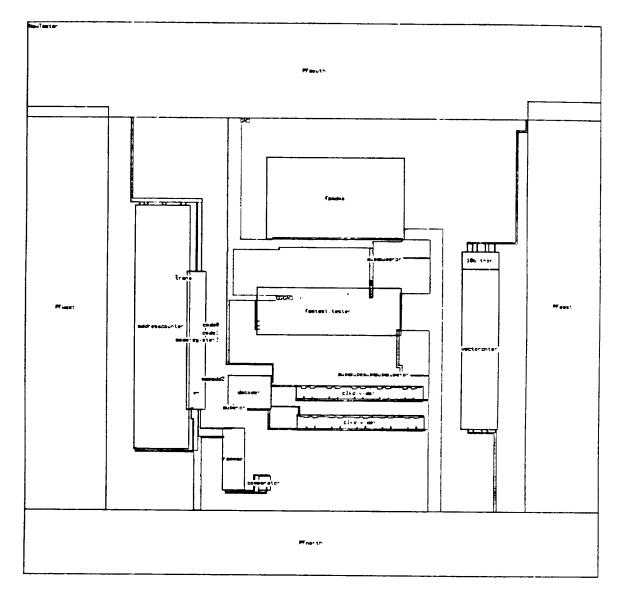

|               | 7.2.3 Effects on Automatic Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108      |  |  |