## SRAM Leakage-Power Optimization Framework: a System Level Approach

Animesh Kumar

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-182 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-182.html

December 19, 2008

Copyright 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Acknowledgement

Financial support from Gigascale Silicon Research Center, and National Science Foundation Infrastructure Grant (No: 0403427)

### SRAM Leakage-Power Optimization Framework: a System Level Approach

by

Animesh Kumar

B.Tech. (Indian Institute of Technology, Kanpur, India) 2001M.S. (University of California, Berkeley, CA) 2003

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

## GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge: Professor Kannan Ramchandran, Chair Professor Jan M. Rabaey Professor Peter J. Bickel

Fall 2008

The dissertation of Animesh Kumar is approved:

$\operatorname{Chair}$

Date

Date

Date

University of California, Berkeley

Fall 2008

## SRAM Leakage-Power Optimization Framework: a System Level

Approach

Copyright 2008

by

Animesh Kumar

#### Abstract

#### SRAM Leakage-Power Optimization Framework: a System Level Approach

by

Animesh Kumar

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Kannan Ramchandran, Chair

SRAM leakage-power is a significant fraction of the total power consumption on a chip. Various system level techniques have been proposed to reduce this leakage-power by reducing (scaling) the supply voltage. SRAM supply voltage scaling reduces the leakagepower, but it increases stored-data failure rate due to commonly known failure mechanisms, for example, soft-errors.

This work studies SRAM leakage-power reduction using system level design techniques, with a data-reliability constraint. A statistical or probabilistic setup is used to model failure mechanisms like soft-errors or process-variations, and error-probability is used as a metric for reliability. Error models which combine various SRAM cell failure mechanisms are developed. In a probabilistic setup, the bit-error probability increases due to supply voltage reduction, but it can be compensated by suitable choices of error-correction code and data-refresh (scrubbing) rate. The trade-offs between leakage-power, supply voltage reduction, data-refresh rate, error-correction code, and decoding error probability are studied. The leakage-power – including redundancy overhead, coding power, and data-refresh power – is set as the cost-function and an error-probability target is set as the constraint. The cost-function is minimized subject to the constraint, over the choices of data-refresh rate, error-correction code, and supply voltage. Using this optimization procedure, simulation results and circuit-level leakage-power reduction estimates are presented.

Experimental results are presented for the special case of low duty-cycle applications like sensor nodes. Retention of stored data at lowest possible leakage-power is the only target in this case. Each SRAM cell has a threshold parameter called the data-retention voltage (DRV), above which the stored bit can be retained reliably. The DRV exhibits systematic and random variation due to process technology. Using the proposed optimization method, the retention supply voltage is selected to minimize the leakage-power per useful bit. The fundamental lower bound on the leakage-power per bit, while taking the DRV distribution into account, is established. For experimentally observed DRV-distributions from custom built SRAM chips, a [31, 26, 3] Hamming code based retention scheme achieves a significant portion of the leakage-power reduction compared to the fundamental limit. These results are verified by twenty-four experimental chips manufactured in an industrial 90nm CMOS process.

> Professor Kannan Ramchandran Dissertation Committee Chair

To my mother and father.

सरस्वतीं विद्यां शरदेन्दुसौम्यवदनां वीणावेदाक्षमालावरहस्तां वाणीं मतिबुद्धिप्राणकर्त्रीं विषयपापतिमिरार्कप्रमां शारदां अर्पयामि ॥

# Contents

| List of Figures in |                                                           |                                                                                                                                                  | iv                                                   |

|--------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1                  | <b>Intr</b><br>1.1<br>1.2<br>1.3                          | oduction         Contributions         Related work         Assumptions and Notation         1.3.1         Simplifying assumptions         1.3.2 | 1<br>7<br>8<br>13<br>13<br>16                        |

| <b>2</b>           | Opt                                                       | imization framework                                                                                                                              | 19                                                   |

|                    | <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul> | Overview                                                                                                                                         | 19<br>24<br>26<br>28<br>30<br>32<br>33               |

| 3                  | Mac                                                       | cro-modeling of failures                                                                                                                         | 34                                                   |

|                    | 3.1<br>3.2<br>3.3<br>3.4                                  | Soft-error rate estimation                                                                                                                       | $36 \\ 41 \\ 43 \\ 47 \\ 53 \\ 58 \\ 61 \\ 63 \\ 64$ |

| 4                  | $\mathbf{Sim}$                                            | ulation results on modeling and optimization                                                                                                     | 65                                                   |

|                    | $4.1 \\ 4.2$                                              | Average SRAM leakage current       Soft-error rates         Soft-error rates       Soft-error rates                                              | $\begin{array}{c} 65 \\ 67 \end{array}$              |

|    | 4.3        | Parametric failures – read upset probability        | 68 |

|----|------------|-----------------------------------------------------|----|

|    | 4.4        | Parametric failures – write failure probability     | 70 |

|    | 4.5        | Parametric failures – hold failure probability      | 71 |

|    | 4.6        | Leakage-power optimization results                  | 72 |

|    | 4.7        |                                                     | 78 |

|    | 4.8        | Review                                              | 81 |

| 5  | Star       | ndby SRAM                                           | 82 |

|    | 5.1        | Modeling assumptions                                | 84 |

|    |            | 5.1.1 Notation                                      | 85 |

|    | 5.2        | Standby SRAM: theoretical results                   | 86 |

|    |            | 5.2.1 SRAM cell Retention model                     | 86 |

|    |            | 5.2.2 Standby SRAM low-power architecture           | 87 |

|    |            | 5.2.3 Power dependence on the supply voltage        | 90 |

|    |            | 5.2.4 Fundamental bounds on the power reduction     | 91 |

|    |            | 5.2.5 Practical low-latency codes and power per bit | 93 |

|    |            | 5.2.6 Chip-implementation overview                  | 95 |

|    | 5.3        | Optimization results from SRAM chips                | 96 |

|    |            | 5.3.1 Spatial correlation of $DRV$                  | 97 |

|    |            |                                                     | 98 |

|    |            | 5.3.3 Row redundancy design                         | 99 |

|    |            | 5.3.4 Parameter dependencies                        | 01 |

| 6  | Con        | nclusions 1                                         | 03 |

|    | 6.1        | Future work                                         | 05 |

| Bi | bliog      | raphy 10                                            | 07 |

| 7  | Арр        | pendix 1                                            | 19 |

|    | $7.1^{-1}$ | Lower bound derivation using channel coding theorem | 19 |

|    | 7.2        | Upper bound derivation using the Gilbert bound 1    | 22 |

# **List of Figures**

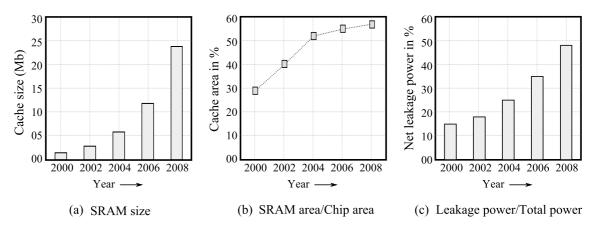

| 1.1 | (a) The increase in cache size with technology node or year is illustrated. This increase is almost exponential. (b) SRAM area in percent of the total chip area as a function of year is illustrated. Observe that cache size has the largest percentage of the total chip area. (c) Increasing leakage power contribution to the total power consumption is shown as a function of time ( <i>source: Intel</i> ).                      | 2        |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2 | The channel model or probabilistic model of an SRAM cell is illustrated. $X$ is a binary input and $Y$ is a binary output. The conditional probabilities                                                                                                                                                                                                                                                                                 | 1 5      |

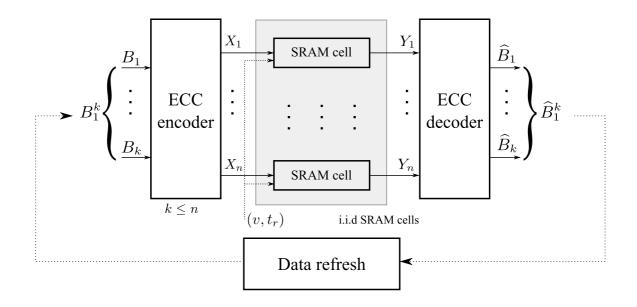

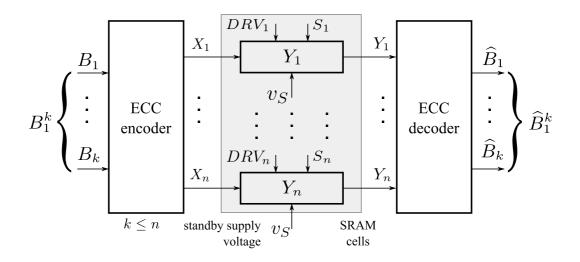

| 1.3 | $(\mathbb{P}[Y = y   X = x])$ depend on the supply voltage $v$ and time $t_r$ The low leakage-power SRAM architecture studied in this work is illustrated.<br>Information bits $B_1^k$ are encoded into $X_1^n = f(B_1^k)$ . Then $X_1^n$ is stored in $n$ i.i.d. SRAM cells. At each refresh cycle, the output bits $Y_1^n$ are read and decoded into $\widehat{B}_1^k$ . This estimate of $B_1^k$ is re-encoded and stored back in the | 17       |

|     | SRAM cells                                                                                                                                                                                                                                                                                                                                                                                                                               | 18       |

| 2.1 | A schematic diagram of the optimization is illustrated. Failure probabili-<br>ties and rates of dominant error-mechanisms, corresponding supply voltages,<br>data lifetime, and SRAM parameters are expected as an input. The op-<br>timizer predicts the best leakage-power achievable within some families of<br>error-correction codes                                                                                                | 21       |

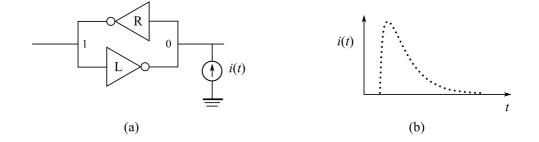

| 3.1 | (a) The simplified circuit (without access-transistors) to evaluate soft-error rate as a function of voltage is illustrated here. The current-source $i(t)$ models the current generated by charged particle. (b) Using experimental measurements and physical models, a simple two-parameter model for $i(t)$ has been proposed in the literature.                                                                                      | 38       |

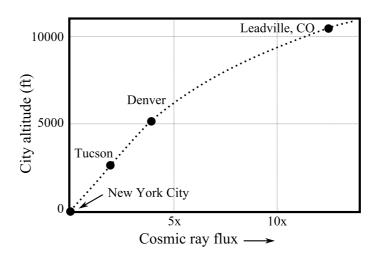

| 3.2 | The increase in cosmic-ray flux with altitude is illustrated. The soft-error rate is proportional to the cosmic-ray flux, and thus it increases with altitude                                                                                                                                                                                                                                                                            |          |

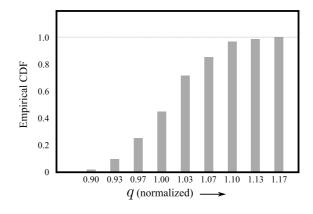

| 3.3 | (source: $IBM$ )                                                                                                                                                                                                                                                                                                                                                                                                                         | 39<br>40 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

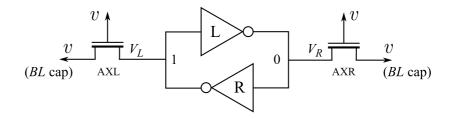

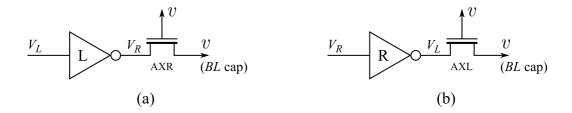

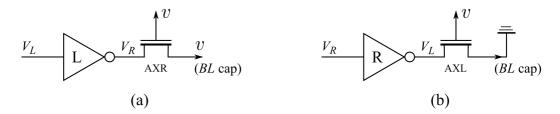

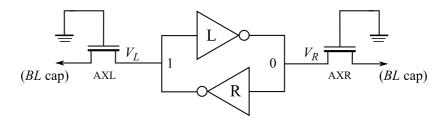

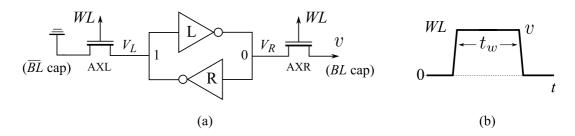

| 3.4  | The DC bias during read operation is illustrated in this figure. The access transistors are turned on, and the bit-line capacitors are charged to the supply voltage $v$ . The nodes with voltages $V_L$ and $V_R$ store the SRAM bit as                                                                                                                      |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

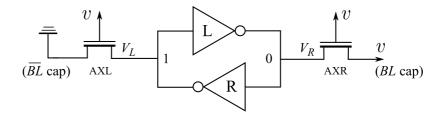

| 3.5  | complementary logical states. $\dots$ The circuit used for obtaining VTCs for $rnm$ calculations are illustrated.<br>The DC bias condition is identical to the read-operation of SRAM, but the inverter L and inverter R circuits are decoupled. (a) The voltage $V_L$ is swept to find the VTC of inverter L. (b) The voltage $V_R$ is swept to find the VTC | 43 |

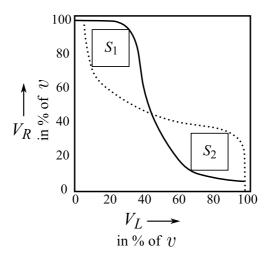

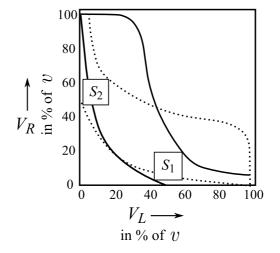

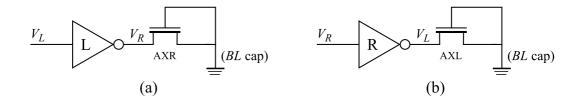

| 3.6  | of inverter R                                                                                                                                                                                                                                                                                                                                                 | 44 |

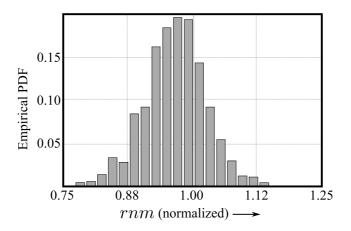

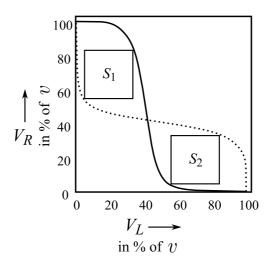

| 3.7  | gram are $S_1$ and $S_2$ with sides $s_1$ and $s_2$ , respectively. Then, $rnm = \min(s_1, s_2)$ .<br>The observed empirical probability density function of $RNM$ at $v = 1.0V$ is                                                                                                                                                                           |    |

| 3.8  | illustrated in this figure. A Gaussian distribution is expected and observed.<br>The DC bias during write operation is illustrated in this figure. The access<br>transistors are turned on and the bit line expecitors are procharged to com-                                                                                                                 | 46 |

| 3.9  | transistors are turned on, and the bit-line capacitors are pre-charged to com-<br>plementary levels for writing the bit. The nodes with voltages $V_L$ and $V_R$<br>store the SRAM bit, and they should flip as a result of write operation<br>These figures illustrate the circuits used for obtaining VTC characteristics for                               | 48 |

| 5.9  | wnm calculations. The bit-line capacitor bias is set as during write operation.<br>(a) The input voltage $V_L$ to the left-inverter is swept to find the VTC of L-                                                                                                                                                                                            |    |

| 2 10 | inverter. (b) The input voltage $V_R$ to the right-inverter is swept to find the VTC of R-inverter. $\ldots$                                                                                                                                                                 | 49 |

| 3.10 | will be obtained by swapping the BL cap bias in Figure 3.9(a) and (b). Let<br>the largest inscribed squares in the butterfly-curves be $S_1$ and $S_2$ with sides                                                                                                                                                                                             |    |

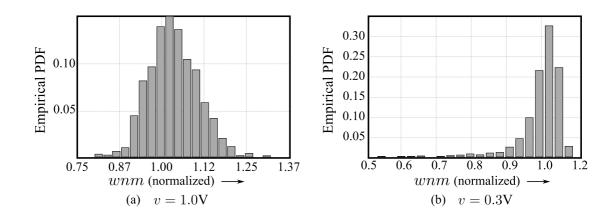

| 3.11 | $s_1$ and $s_2$ respectively. Then $wnm = \min(s_1, s_2)$                                                                                                                                                                                                                                                                                                     | 50 |

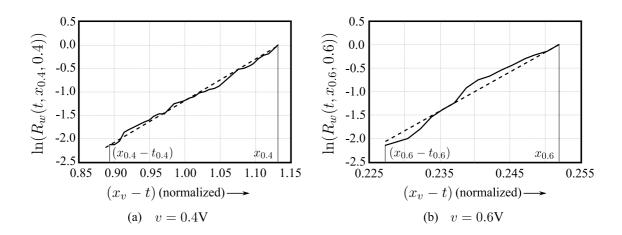

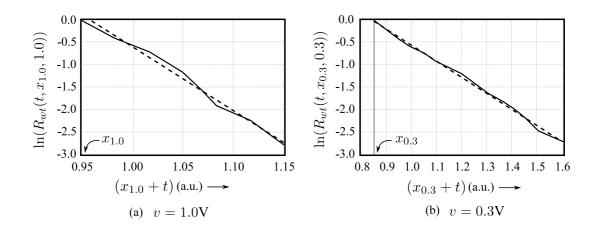

| 3.12 | voltages $(v = 0.3V)$ the distribution is symmetric and at low<br>voltages $(v = 0.3V)$ the distribution exhibits a single-sided tail This figure illustrates the exponential behavior of $R_w(t, x, v)$ at two different                                                                                                                                     | 51 |

| 3.13 | supply voltages. This behavior will be extrapolated to $(x_v - t) = 0$ for write failure estimation                                                                                                                                                                                                                                                           | 53 |

|      | sistors are turned off, and the bit-line capacitors are kept at ground voltage.<br>The nodes with voltages $V_L$ and $V_R$ store the SRAM bit                                                                                                                                                                                                                 | 53 |

| 3.14 | These circuits used for obtaining VTCs for $snm$ calculation are illustrated.<br>The access-transistors and $BL$ cap are turned off. (a) The voltage $V_L$ is<br>swept to find the VTC of inverter L. (b) The voltage $V_R$ is swept to find the                                                                                                              |    |

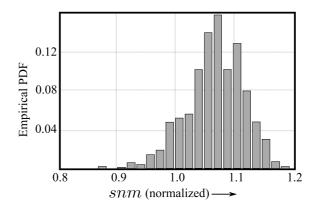

| 3.15 | VTC of inverter R                                                                                                                                                                                                                                                                                                                                             | 54 |

|      | since the squares in the wings of butterny diagram be $S_1$ and $S_2$ with sides $s_1$ and $s_2$ respectively. Then $snm = \min(s_1, s_2) \dots \dots \dots \dots \dots \dots$                                                                                                                                                                                | 56 |

| <ul> <li>3.16 The observed empirical probability density function of illustrated in this figure. A Gaussian distribution is exp</li> <li>3.17 (a) This figure illustrates the write operation circuit. pre-charged to complementary levels, and then the ac are turned on. (b) The WL pulse is enabled for a time t</li> </ul> | pected and observed. 57<br>The $BL$ and $\overline{BL}$ are<br>cess transistors' gate<br>$_w$ to facilitate writing |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| in any SRAM cell                                                                                                                                                                                                                                                                                                               | large enough $x$ is il-<br>x = 0.1. Only plots                                                                      |

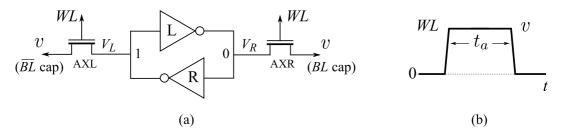

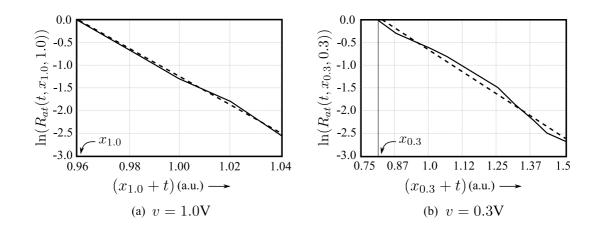

| corresponding to $v = 0.3$ V and $v = 1.0$ V are shown<br>3.19 (a) This figure illustrates the read operation circuit.<br>pre-charged to supply voltage $v$ , and then the access<br>turned on. (b) The $WL$ pulse is enabled for a time $t_a$<br>from any SRAM cell. If the capacitor $BL$ will discharge                     | The $BL$ and $\overline{BL}$ are<br>transistors' gates are<br>to facilitate reading                                 |

| time $t_a$ , then SRAM read is successful                                                                                                                                                                                                                                                                                      | large enough $x$ is il-<br>c] = 0.1. Only plots                                                                     |

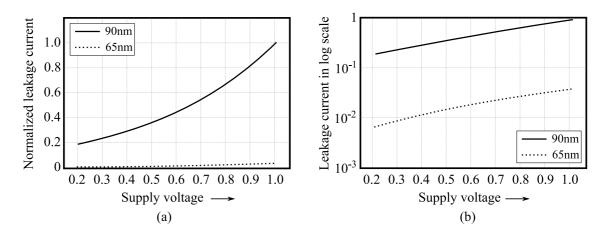

| 4.1 (a) Average (over process-variations) SRAM cell leaka<br>in this figure. Observe that due to high threshold v<br>technology has lower leakage. (b) Leakage current com<br>in log scale. Observe that in 65nm technology, the leak                                                                                          | oltage, 65nm CMOS<br>parison is illustrated<br>kage is smaller by an                                                |

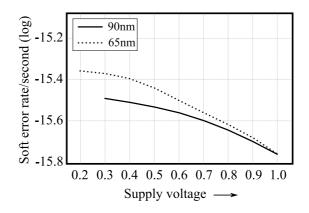

| <ul> <li>order of magnitude.</li> <li>4.2 The soft-error rate (per second) as a function of supply The 65nm technology is expected to have a larger increased.</li> </ul>                                                                                                                                                      | voltage is compared.<br>ease in soft-error rate                                                                     |

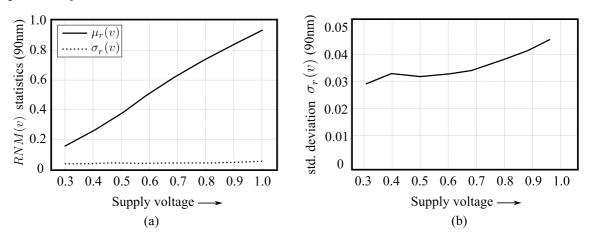

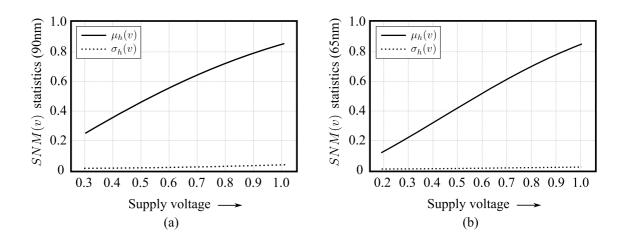

| <ul> <li>with supply voltage reduction than the 90nm technolog</li> <li>4.3 (a) The normalized mean and standard deviation of a for the 90nm technology. (b) The approximately const (especially for lower voltages) is illustrated in this plot.</li> </ul>                                                                   | RNM(v) are plotted<br>ant behavior of $\sigma_r(v)$                                                                 |

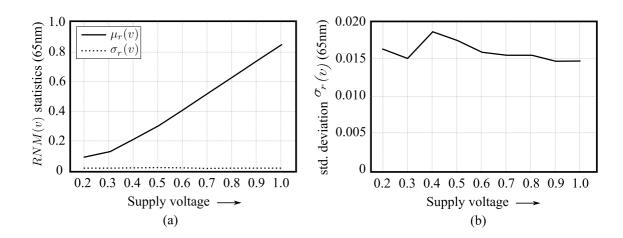

| 4.4 (a) The normalized mean and standard deviation of $RN$ the 65nm technology. (b) The approximately constant                                                                                                                                                                                                                 | VM(v) are plotted for<br>the behavior of $\sigma_r(v)$ is                                                           |

| <ul> <li>illustrated in this plot.</li> <li>4.5 (a) The normalized mean and standard deviation of SN the 90nm technology. (b) The normalized mean and s</li> </ul>                                                                                                                                                             | MM(v) are plotted for<br>standard deviation of                                                                      |

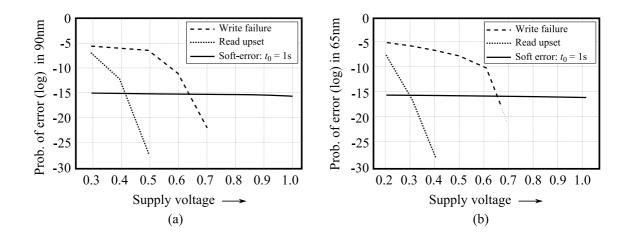

| <ul> <li>SNM(v) are plotted for the 65nm technology</li> <li>4.6 Obtained estimates for soft-errors and parametric failur the 65nm technologies, are compared in this semilog ages, parametric failures are significant. At high-volta</li> </ul>                                                                              | res, for the 90nm and<br>; plot. At low volt-                                                                       |

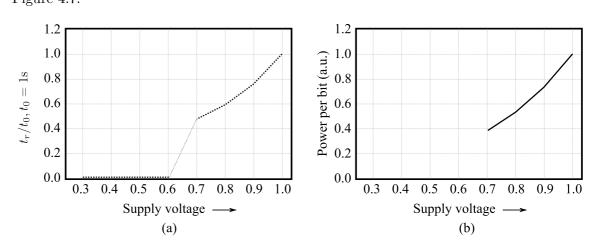

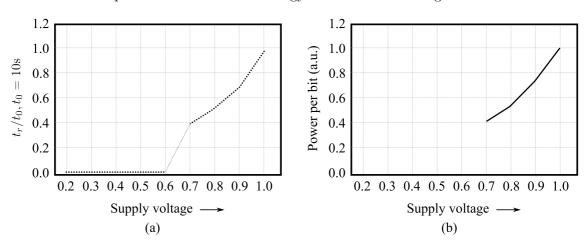

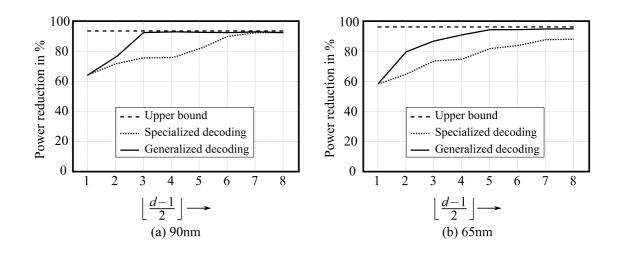

| <ul> <li>probability mechanism is soft-error</li></ul>                                                                                                                                                                                                                                                                         | ion code, The data-<br>he <i>power per bit</i> cost<br>tage reduction is lim-<br><i>wer per bit</i> reduction       |

vi

| 4.8  | (a) For [31, 26, 3] Hamming code as the error-correction code, The data-<br>refresh rate is plotted for the 90nm technology. (b) The <i>power per bit</i> cost<br>function is plotted against the supply voltage v. The voltage reduction is lim-<br>ited by parametric failures which start at 0.6V. The <i>power per bit</i> reduction<br>is nearly 60%. | 74       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.9  | The upper bound is obtained by comparing leakage-power per cell at min-<br>imum supply voltage and leakage-power per cell at $v = 1.0$ V. Power per<br>bit reduction gets close to this upper bound with increase in minimum dis-<br>tance d of error-correction code. Generalized decoding based power reduction                                          |          |

| 4.10 | approaches the upper bound at a faster rate                                                                                                                                                                                                                                                                                                                | 77<br>78 |

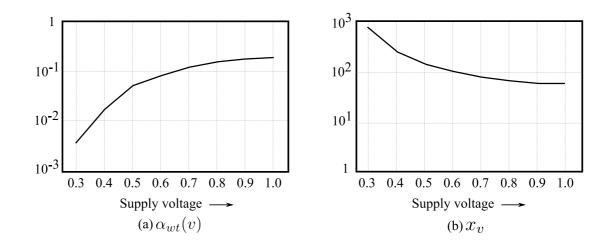

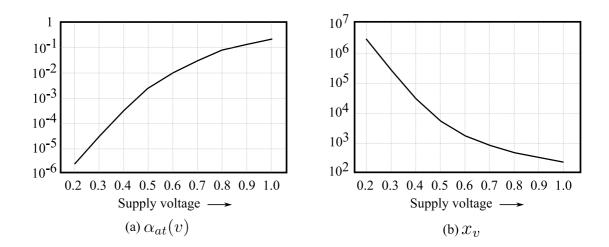

| 4.11 | These estimates were obtained using Monte Carlo simulations in the 65nm technology. (a) The estimated exponent $\alpha_{wt}(v)$ of the write-time model in (4.5) is plotted. (b) The estimate of the reference $x_v : \mathbb{P}[T_w > x_v] = 0.1$ is                                                                                                      |          |

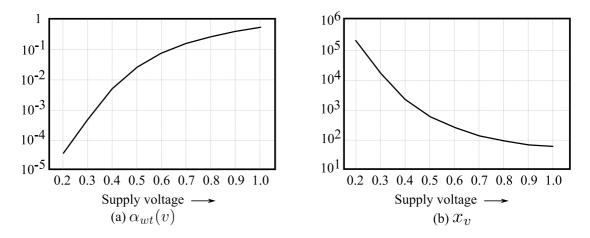

| 4.12 | plotted                                                                                                                                                                                                                                                                                                                                                    | 79       |

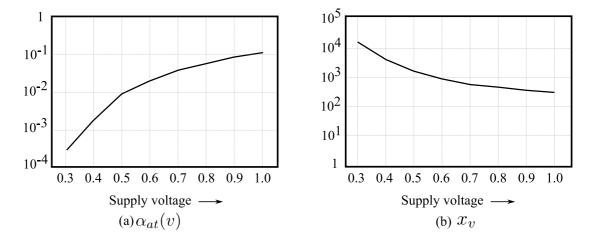

| 4.13 | plotted                                                                                                                                                                                                                                                                                                                                                    | 80<br>81 |

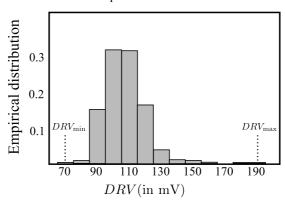

| 5.1  | The experimental intra-chip $DRV$ varies from 70 to $190mV$ in the 90nm CMOS technology. The worst-case solution for data-retention is a supply                                                                                                                                                                                                            | 0.9      |

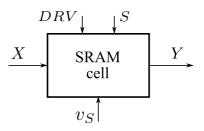

| 5.2  | voltage of 200mV                                                                                                                                                                                                                                                                                                                                           | 83       |

| 5.3  | otherwise                                                                                                                                                                                                                                                                                                                                                  | 87       |

| 5.4  | $v_S$ is selected such that $\mathbb{P}(\text{outage})$ is negligible (see (5.3))                                                                                                                                                                                                                                                                          | 88       |

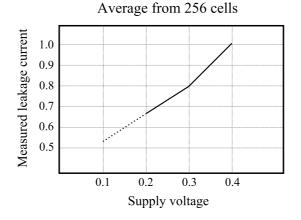

|      | is approximately linear.                                                                                                                                                                                                                                                                                                                                   | 90       |

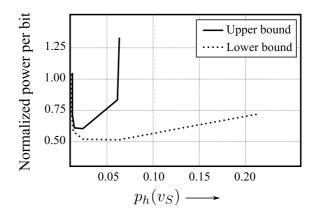

| 5.5  | Power per bit bounds are plotted as functions of the $DRV$ -failure rate $p_h(v_S)$ .    |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | The minima of upper and lower bounds are $40\%$ and $49\%$ lower than the                |     |

|      | worst-case.                                                                              | 93  |

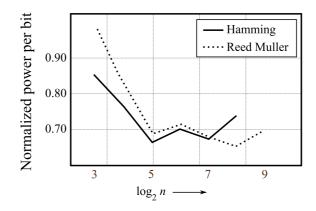

| 5.6  | For an outage $\epsilon = 0.01$ , the optimum power per bit for Hamming and Reed         |     |

|      | Muller codes are plotted. Maximum power reduction is achieved at $n = 31$                |     |

|      | for Hamming codes and at $n = 256$ for Reed Muller codes                                 | 95  |

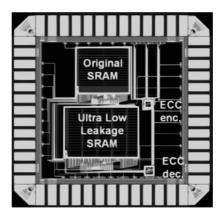

| 5.7  | Fabricated SRAM layout in an industrial 90nm CMOS technology is shown.                   | 96  |

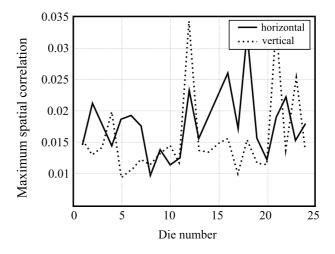

| 5.8  | The maximum absolute empirical horizontal and vertical correlation coeffi-               |     |

|      | cients are plotted as a function of experimental chip index. The maximum                 |     |

|      | observed correlation coefficient is less than 3.5%.                                      | 97  |

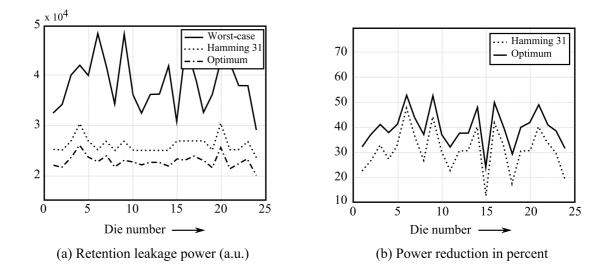

| 5.9  | (a) The leakage-power (in a.u.) for the worst-case method, the [31.26, 3] Ham-           |     |

|      | ming code based implementation, and the theoretical optimum (see $(5.9)$ ) are           |     |

|      | compared. (b) Power reduction for the [31, 26, 3] Hamming code based imple-              |     |

|      | mentation and the theoretical optimum are compared. The implementation                   |     |

|      | tracks the optimum within a close margin of 6-11%.                                       | 100 |

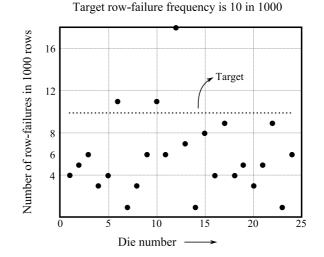

| 5.10 | The number of rows in decoding-failure are plotted as a function of experimental         | _   |

|      | chip number. The average number of failures, 7 in 1000, satisfies the $1\%$              |     |

|      | decoding-failure target (see $(5.15)$ )                                                  | 101 |

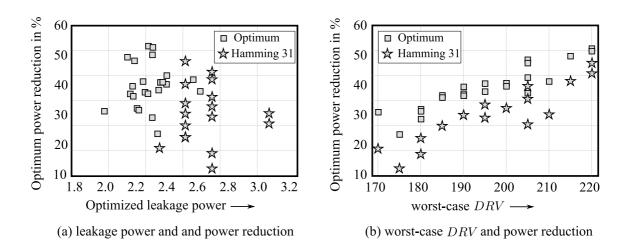

| 5.11 | (a) No relationship between <i>power per bit</i> and optimum <i>power per bit</i> reduc- |     |

|      | tion was observed. (b) On average, power reduction increases linearly with               |     |

|      | the intra-chip worst-case $DRV$ voltage of an SRAM                                       | 102 |

|      |                                                                                          |     |

#### Acknowledgments

Salutations to that Supreme Consciousness, Who inspires thought, wisdom, intelligence, and consciousness in all the living beings. Salutations to my parents, who selflessly endured many difficult financial and emotional troubles to push me towards my desired career objectives. Among countless other qualities, their love, care, nurturing, guidance, and mercy have been irreplaceable.

Thanks to my advisor, Prof. Kannan Ramchandran, who guided me to a successful Ph.D. Over the years, his patience, suggestions, insights, vision, guidance, benevolence, and understanding has been excellent. His patience and help during my qualifying examination is unforgettable. His encouragement and persistence has improved my presentation, understanding, and writing skills by a large extent.

Thanks to Prof. Jan Rabaey, who helped me on numerous occasions with his patience, insights, guidance, vision, and understanding. It has been a pleasure to work with him on probabilistic aspects of memories. I could lay hands on BWRC resources and cutting-edge technology access due to his kindness.

Thanks to Prof. Kannan Ramchandran and Prof. Jan Rabaey for funding and support.

Special thanks to Prof. Martin Vetterli, Prof. Aloke Dutta, and Prof. Rakesh Bansal for successful recommendation letters, because of which I got admitted to University of California, Berkeley.

I continuously adore the 'how to write' training imparted by Dr. Prakash Ishwar.

I deeply appreciate the help, kindness, support, and suggestions of Prof. Peter

Bickel and Prof. Martin Wainwright, who were present in my qualifying exam committee.I again thank Prof. Peter Bickel for being a member in my dissertation committee.

I enjoyed being a teaching assistant under Prof. Ron Fearing, Prof. Venkat Anantharam, and Prof. Kannan Ramchandran.

I would like to thank my Berkeley friends including Dr. Prakash Ishwar, Dr. Vinod Prabhakaran, Dr. Huifang Qin, Dr. Arindam Chakrabarti, Dr. Vinayak Prabhu, Dr. Rupak Majumdar, Dr. Amish Patel, Nidhi Tiwary, Dr. Kaushik Ravindran, David Chen, James Wu, Pulkit Grover, Xuening Sun, Victor Wen, Chintan Thakkar, Dr. Artin Der Minassians, Simone Gambini, Mark Johnson, Biswanath Poudel, Afshan Sheikh, Maryam Vareth, Chuohao Yeo, Dr. Abhijit Davare, Krish Eswaran, Dr. Allie Fletcher, Dr. Rohit Puri, Dr. Abhik Majumdar, Dr. Dan Schonberg, Ping-Chen Huang, Nadathur Satish, Dr. June Wang, Susmit Jha, Dr. Alex Dimakis, Dr. Anand Sarwate, Dr. Hiren Patel, Wei Wang, Hao Zhang, Louis Alarcon, Asako Toda, Dr. Nate Pletcher, Michael Mark, Dr. Krishnendu Chatterjee, Dr. Satrajit Chatterjee, Jike Chong, and Bryan Catanzaro.

This work has benefited a lot from suggestions made by researchers at Intel Corporation, consisting of Dr. Marly Roncken, Dr. T. M. Mak, Dr. M. Spica, Dr. Rajiv Mathur, and Dr. M. Zhang.

I deeply appreciate the financial support from the Gigascale Silicon Research Center (GSRC), and the National Science Foundation (NSF).

I would like to acknowledge the company of my undergraduate friends including Dr. Saurabh Tiwary, Dr. Tandra Ghose, Dr. Smita Agrawal, Ashwani Kumar, Dr. Sourav Chatterji, Dr. Supratim Ray, Pradeep Gatram, Pushkar Sinha, and Gaurav Srivastava. I adore University of California at Berkeley and their educational system, which allow many excellent aspiring individuals from across the globe to do research and exchange ideas on a solid educational platform.

Administrative assistants including Ruth Gjerde, Mary Byrnes, Erin Reiche, Jennifer Stone, Brenda Farrell, Tom Boot, La Shana Porlaris, Loretta Lutcher, Mark Davis, Joe Bullock, Elisa Lewis, Jontae Gray, and Farah Pranawahadi were very helpful.

Blessed I am to have three siblings – Snigdha Bhasin, Piyush Singh, and Akash Kartikey. They have been very supportive and encouraging during my Ph.D endeavors.

## Chapter 1

# Introduction

Static random access memory or SRAM has been the main data storage block for many generations of microprocessors. As the name suggests, the SRAM cell stores a bit without dissipating any active power, unlike its counterpart dynamic random access memory or DRAM [1]. Even though a DRAM cell is smaller than an SRAM cell, the latter has two important advantages: (i) once a bit has been written in an SRAM cell, active power is not spent during retention of the stored bit, and (ii) it is faster to read and write from an SRAM cell. However, SRAM cells are volatile, i.e., they require a positive supply-voltage to retain data. A positive supply-voltage results in leakage-power dissipation to retain SRAM cell data. In earlier technologies, data bits could be stored in SRAM at negligible leakage-power consumption. However, with technology scaling, it has been observed that a significant fraction of total power is wasted as leakage-power in cache or SRAM [2]. In the future, this trend is expected to worsen, unless the threshold voltage of transistors is increased. The trends of SRAM size and leakage-power as a function of year (technology) are illustrated in Figure 1.1 (source: Intel) [2].

Observe that, with Moore's law SRAM size on the microprocessor has increased with time. With Moore's law and technology scaling, the SRAM leakage gets higher, as illustrated in Figure 1.1(c). The SRAM leakage-power is even more significant for low dutycycle applications, like sensors [3]. This is because low duty-cycle applications store the state in SRAM and turn off the other hardware blocks in the chip to save power. If the storage time is large, then the time-averaged active power is negligible compared to the SRAM leakage-power.

Figure 1.1: (a) The increase in cache size with technology node or year is illustrated. This increase is almost exponential. (b) SRAM area in percent of the total chip area as a function of year is illustrated. Observe that cache size has the largest percentage of the total chip area. (c) Increasing leakage power contribution to the total power consumption is shown as a function of time (*source: Intel*).

At a broad level, two techniques can control or reduce the leakage-power problem in SRAM: (i) circuit-level design techniques, and (ii) system level design techniques such as supply voltage reduction. Of these, the circuit level techniques usually change one or more parameters of the SRAM circuit. For example, these techniques include modification of SRAM cell's transistor-parameters like threshold voltage or sizing [4], addition of a sleep transistor or control gate to reduce standby leakage [5–7], usage of asymmetry in the SRAM cell design [8], proposed usage of a different transistor than traditional MOSFET [9], and a change in the SRAM cell structure to enable ultra-low voltage operation [10]. Note that this list is not complete, and other ideas can be found in the literature. In contrast, at the system level, the SRAM cell is not altered but architecture-level changes are introduced. The most common architecture level technique is supply voltage reduction (scaling) of inactive SRAM, without affecting the stored bits [11–15]. This technique works since leakage-power has strong dependence on the supply voltage.

This work focuses on *system level* techniques to reduce SRAM leakage-power, therefore, these techniques are examined in detail. The trendy supply voltage scaling technique reduces the leakage-power. However, supply voltage scaling increases failure-rate of the stored data. Stored SRAM-cell data is subjected to the following failure mechanisms:

- 1. Soft-errors due to cosmic particles or alpha particles from die-packaging [16].

- 2. Parametric failures which include read-upset, write-failure, write-time failure, access-failure, and hold-failure due to process-variations [17].

- 3. Supply voltage noise induced failures [18, 19].

- 4. Gate-leakage fluctuations due to trapped charge in gate oxide [20].

These failure mechanisms increase with supply voltage reduction. Soft error increase with voltage reduction has been extensively reported in the literature [16, 21–24]. Read, write, or hold (store) operation failures increase with supply voltage reduction. This has been reported in many references [10, 17, 25–27]. Supply noise induced failures are usually tackled

by a 100mV voltage margin [18, 19]. Finally, gate-leakage fluctuations, similar to random telegraph signal, change the minimum voltage at which an SRAM cell can work. This phenomenon, termed as erratic fluctuations, was reported by Agostinelli et al. [20]. Thus, any straightforward supply voltage scaling based leakage-power reduction is achieved at the cost of lower data-reliability. An alternate interpretation is that the lower leakage-power is achieved by an increase in data-failure rate.

On the other hand, if the supply voltage is kept at a high-level to mitigate the above failure mechanisms, then leakage-power will be high. Leakage-power increase is aggravated by two more reasons: (i) Cache-size typically increases with technology generation to provide faster computing, (ii) to compensate for process variations, the SRAM area is not (geometrically) scaled fully with technology [17, 25, 27]. A high supply voltage, with large cache-size and large SRAM cell area, leads to significant leakage-power.

At the system level, coding and error-correction have been used for communication since decades [28–31]. In fact, it was noted that this error-correction can be used for storage since a bit-level memory can be thought of as a binary input binary output channel. Not surprisingly, these codes have also been used in SRAM as an indicator of soft-error events [32–34]. However, till date the usage of error-correction in SRAMs is only to correct (or detect) a single-bit in error [33]. In error-correction coding (or channel coding), usually redundancy (parity check) is introduced to combat against bit-errors. In a probabilistic setup, the amount of redundancy determines the *decoding error probability* and the *storage efficiency* (in bits/cell) – thereby introducing a trade-off between the two quantities.

A technique called "scrubbing" has also been studied in the literature [34–38].

Among the error mechanisms mentioned before, soft-errors, supply noise induced errors, and fluctuating gate-leakage induced errors randomly happen as a temporal phenomena. Thus, the number of induced bit-errors increases on average with the storage time. If an error-correction code is used, any errors in the stored data can be periodically checked and corrected to combat bit-error accumulation. This procedure is commonly called as *scrubbing*. In this work, it will be called as *data-refresh*. This refresh is triggered by any errors present in the stored bits and it reduces the probability of decoding error at the expense of extra power consumption.

In a probabilistic setup, while supply voltage reduction causes the bit-error probability to increase, it can be compensated by suitable choices of error-correction code and data-refresh rate. To the best of our knowledge, the trade-offs between leakage-power, supply voltage reduction, data-refresh rate, decoding error probability, and error-correction code has not been studied in the literature. Accordingly, these trade-offs will be studied in this work. The trade-off study procedure is as follows. The *leakage-power* – including redundancy overhead, coding power, and data-refresh power – is the cost-function to be minimized. The failures will be modeled in a probabilistic setup and the constraint is set by an error-probability target. In particular, the error-probability target is set by soft-errors at the supply voltage  $V_{dd} = 1.0$ V and a single-error correction code. <sup>1</sup> The supply voltage, the data-refresh rate, and the error-correction code will be treated as variables chosen to optimize the leakage-power cost function. Using this optimization principle, the important contributions of this work are described in the next section.

<sup>&</sup>lt;sup>1</sup>A single-error correction code is chosen for target error probability since this is a common error-correction mechanism used in contemporary SRAM [33].

To understand the limits of leakage-power reduction, "standby-mode" of an SRAM is described next. This concept was introduced by papers using supply voltage scaling to reduce the leakage-power. An SRAM module which is in "no-operation" ON mode is classified as a *standby SRAM*. In this mode, the SRAM retains the data, but it is not accessed for read or write operations. The only task in this mode is to retain the stored data. The system level leakage reduction techniques, like drowsy-cache [11], exploit the fact that read and write activity are absent in the standby-mode, and thus a lower (than active-mode) supply voltage level can be used to reduce the leakage-power till storage (hold) failures begin [11,12,15]. Because two supply voltages are assumed in such solutions – one for standby-mode and one for normal operation – these solutions are labeled as *dynamic voltage scaling* (DVS) techniques. If a dynamic supply voltage is not available, then this solution *cannot* be used.

Within the topic of SRAM leakage-power reduction, the contributions of this work are classified into two cases: (i) When a dynamic supply voltage is not available or not desired, and (ii) when a dynamic supply voltage can be used. Previously, while accounting for various error mechanisms, parametric failures were mentioned. Various parametric failures correspond to the read, write, and hold operations. In case (i) of voltage scaling, all parametric failures should be counted for various supply voltages. In contrast, in case (ii) of voltage scaling, only the *hold-failure* among parametric failures should be counted for various supply voltages. This is because read and write operations are assumed to happen at a high supply voltage. The main results are presented next.

## 1.1 Contributions

The contributions of this work are listed below. The supply voltage assumptions are specified when necessary.

- Error models which combine various failure mechanisms are developed, while accounting for data-lifetime, and spatially fixed or random nature of these errors. Spatially fixed errors, where the erratic location can be known, are easier to correct than spatially random errors. An error-probability constrained optimization framework is developed, which accepts SRAM cell parameters (like leakage-power and error probabilities) for various supply voltages as input and optimizes leakage-power over supply voltage, error-correction code, and refresh-time (see Chapter 2).

- For exemplifying results, the supply voltage dependencies of failure mechanisms, a key ingredient in optimization, are estimated by circuit-level Monte Carlo simulations and low-complexity macro-models. These macro-models use simple statistical techniques to extrapolate error probabilities (see Chapter 3).

- Using error probabilities estimated by circuit level simulations, it is shown that datarefresh and stronger error-correction codes can reduce the supply voltage significantly, without any increase in the decoding error probability. For an approximate idea, in 90nm CMOS technology simulations, the supply voltage can be reduced to 0.3V. The leakage-power per cell at 0.3V is approximately 94% lower than that at 1.0V. Simulation results from the 90nm CMOS technology and 65nm CMOS technology are presented (see Chapter 4).

For case (ii) of voltage scaling, when a different supply voltage can be used for standby operation, the error mechanisms are dominated by hold-failures (among parametric failures) and soft-errors. In this special case, the following results are shown and verified using experiments and simulations with *twenty-four fabricated* chips in Chapter 5:

- Fundamental lower bound on the leakage-power reduction in terms of the hold-failure distribution using techniques from *information and coding theory* are established. The distribution of hold-failure is learned from custom-built fabricated chips. This leakage-power lower bound as a function of the experimental-chip's index will be presented.

- Due to latency-constraints on decoding, power reduction as a function of the blocklength is studied. A low complexity Hamming code was chosen for implementation. Its leakage-power reduction performance in comparison with the fundamental bounds will be presented. The [31, 26, 3] Hamming code based implementation's power reduction closely tracks the optimum power reduction, and this desirable property justifies our low-complexity implementation.

Other interesting measurement results are also presented. They include bounds on the empirical correlation of neighborhood SRAM cells, and scatter plots to examine dependencies between parameters of interest.

#### 1.2 Related work

**Voltage scaling:** Voltage scaling for data-storage in standby-SRAM was first proposed by Kim et al. [11]. Later, it was shown by Qin et al. [12,13] that there is a minimum supply

voltage for an SRAM cell above which it can retain (store) a bit reliably (in the absence of other failures). This minimum retention voltage is termed as *data retention voltage* or DRV in the literature. Due to process variations, the DRV exhibits a distribution [13]. The largest DRV on a chip is the supply voltage needed for ensuring reliable retention across all SRAM cells. The temperature variation of this largest DRV parameter was studied by Wang et al. [39]. Multiple standby voltages have also been proposed in the literature [15], but our results in Chapter 5 show that a single standby supply voltage is optimum in a statistical setup.

**Soft-errors:** Soft-errors were first observed in DRAMs [40]. Later companies like IBM and Intel did a series of experiments to characterize soft-errors for SRAM arrays. A summary of experiments at IBM is presented by Ziegler et al. [16] and it is a recommended reading for understanding various soft-error issues faced while designing circuits. Freeman proposed a canonical circuit for soft-error rate estimation using the critical charge model [41]. The critical charge model uses a current source, which was later validated by Hazucha and Svennsson [23, 24]. The shape of this current source has been modeled as a double exponential in some other works (for example [42]). A different approach to estimate soft-errors using node capacitance was introduced by Merelle et al. [43] which uses complicated threedimensional CAD analysis. Comparisons of various soft-error models has been studied by Naseer et al. [44]. In this work, the Freeman model will be used because it successfully models SRAM failure rates as demonstrated by Hazucha and Svennsson [23,24].

**Parametric failures:** Parametric failures affect the read, write, or hold (store) ability of SRAM cell. There are five types of parametric failures that need to be accounted. They

are: (i) read-upset failure in which the stored bit flips on read operation, (ii) write-failure in which a bit cannot be written into the cell, (iii) hold-failure in which stored bit is not retained in the cell, (iv) access-time failure in which stored bit cannot be read within a specified duration, and (v) write-time failure in which a bit cannot be written within a specified duration [25,26,45]. Typically these failures start to happen as voltage is reduced or as process-variations increase [10,17,26,45,46]. Because of process-variations, some cells fail earlier than the others, and thus failures can be modeled in a probabilistic or statistical setup [25,45].

Some comments about failure probability estimation are in order. Within parametric failures, the access-time and write-time failures can be made negligible by choosing read-time and write-time to be large enough. The distribution of critical write-time and read-time across cells has been modeled by Roy et al. [25], and Agarwal and Nassif [45]. The other three failures are estimated using noise-margin techniques (see Chapter 3 for detailed discussions). These noise-margin techniques have been proposed and discussed in detail in the literature (for example, see [17, 26, 45]).

Erratic fluctuations: Trapping and de-trapping of charges in Si-SiO<sub>2</sub> interface causes significant  $V_{cc|\min}$  fluctuation in SRAMs. By definition,  $V_{cc|\min}$  is the minimum voltage at which read, write, and hold operations are successful in an SRAM cell. If the  $V_{cc|\min}$ becomes larger than the supply voltage, and if the bit is accessed, then the bit will be in error. This phenomenon, called erratic fluctuation, varies temporally and spatially. Further, this erratic fluctuation is "soft" in the sense that cell becomes normal (not erratic) after some random time. An essential reference for understanding erratic fluctuations is by Agostinelli et al. [20]. From a modeling perspective, little is known about erratic fluctuation time constants and magnitudes. It is modeled by introducing a gate-leakage current varying as a random telegraph noise signal.

Supply noise: Presence of noise in supply voltage implies temporally (and spatially) varying voltage levels. For using noise statistics in a probability-aware optimization framework, suitable (statistical) characterization of the supply v(t) and dynamic stability metrics are needed. The statistical (correlation properties) of supply voltage noise have been successfully explored by Alon and Horowitz [19]. Dynamic stability of SRAM has been studied in a limited setting of soft-particle strikes by Zhang et al. [47]. However, their treatment is far from complete. The classical approach to ensure supply noise margin is by adding an overhead of 100mV to the supply voltage. This framework assumes the same 100mV margin to prevent supply noise induced errors.

**Cell hardening:** A common approach to tackle soft-errors is by making SRAM cells more tolerant to particle strikes. The common approach involves making larger or more complicated SRAM cells or adding a capacitor to ensure tolerance against energetic particles. A detailed summary of these techniques can be found in the paper by Roche and Gasiot [48]. To this end, it must be noted that even the hardened SRAM cell will have an increase in soft-error rate as the supply voltage is lowered for reducing leakage. Thus, techniques like data-refresh or error-correction will be *needed* to enable supply voltage reduction.

Scrubbing or data-refresh: Data-refresh, popularly called by the ruffian name *scrubbing*, was proposed by Saleh et al. [35] for memories. Its necessity in cache/SRAM was examined by [36]. Some error-probability expressions on error-probability within a refresh-period with

the use of single or double error-correcting codes were explored by Bajura et al. [38].

**Coding theory:** Channel or memory coding for arbitrary reliability was introduced by Shannon in his classic paper on communication theory [28]. Some practical algebraic methods to encode for decreasing decoding error probability were first proposed by Hamming [29]. Reliable storage capacity and coding for storage have been studied by Heegard and El Gamal in the presence of erasures and errors [49]. A succinct reference for channel coding in Information Theory is the book by Cover and Thomas [50]. An exhaustive reference for algebraic error-correction codes is the book by Lin and Costello [51]. In this work, coding theory will be used as a technique to reduce power in storing data in SRAM cells has not been studied by any of these work. Further, coding complexity needs accounting, since the whole error-protected SRAM consists of coding and storage. In channel coding results, usually the complexity (or power) of encoder and decoder is not an issue while deriving capacity. The fresh idea of Green Codes by Grover and Sahai [52] can be included in the optimization setup presented in Chapter 2. This is left as a future work for latency-tolerant large memories where LDPC codes can possibly be a reality.

**Standby SRAM:** Chapter 5 naturally extends the standby SRAM work proposed by Qin et al. [12, 13]. This solution is motivated from the perspective of standby storage in SRAM, where leakage-power minimization leads to total power minimization. Using the voltage scaling approach, it has been shown that any SRAM cell has a critical voltage (called the data retention voltage or DRV) at which a stored bit (0 or 1) is retained reliably [12]. The intra-chip DRV exhibits a distribution due to process-variations. In order to minimize leakage-power without observing hold-failures, a standby supply voltage equal to the highest

DRV among all cells in an SRAM can be used. This is a "worst-case" selection of the standby supply voltage. The leakage-power reduction from  $V_{dd} = 1000$ mV to the largest DRV voltage in many test-chips has been studied in detail by Qin et al. [13, 53]. This work naturally extends these results by power reduction below the worst-case strategy. A supply voltage lower than the largest DRV voltage is chosen, with appropriate error-control coding to overcome ensuing errors. Under this approach, the supply voltage is flexible and the leakage-power per useful bit can be (fundamentally) reduced over the choice of supply voltage. For a detailed understanding of DRV-distribution based leakage-power reduction, previous work is recommended for reading [12, 13, 53].

#### 1.3 Assumptions and Notation

#### 1.3.1 Simplifying assumptions

Multiple-bit failures have been reported in sub-90nm SRAMs (e.g., [21, 54, 55]). Correlation in failures can usually be exploited by coding. However, the dependencies between these failures are not well known. Address permutation schemes can interleave SRAM cells with negligible energy overhead and make the failures (approximately) statistically independent [34, 56]. For simplicity, address interleaving is assumed. The energy and delay cost of address interleaving can be made negligible by permuting the address lines of SRAM. This is highlighted in Example 1.3.1. Please note that even though interleaving can be simply performed by permuting the address lines, it will have power (energy) impact while accessing SRAM cells, especially when word-level access is used.

**Example 1.3.1.** Let  $x_1^l := (x_1, x_2, ..., x_l)$  and  $y_1^n := (y_1, y_2, ..., y_l)$  be the row and column

address bits for any SRAM block, respectively. This array will be  $(2^l \times 2^l)$  in size. Consider the address permutation where these addresses are mapped to  $(y_l, x_{l-1}, y_{l-2}, x_{l-3}, ...)$ and  $(x_l, y_{l-1}, x_{l-2}, y_{l-3}, ...)$ . Simply speaking, the least significant bits are made into most significant bits and the resultant address bits are "mixed." For example,  $(x_1, x_2, x_3, x_4)$  and  $(y_1, y_2, y_3, y_4)$  are mapped into  $(y_4, x_3, y_2, x_1)$  and  $(x_4, y_3, x_2, y_1)$ . These mappings are bijective, or one to one and onto. As a result, each mapped address corresponds to a unique unmapped address.

On a physical layout level, SRAM cells which are close will have addresses that differ in least significant bits. By flipping, these bits are mapped into most significant bits, causing the mapped addresses to be far apart. Mixing is done to ensure two dimensional interleaving.

For implementation purposes, only bounded-distance decoding based block codes are considered. Thus, LDPC, Turbo, or Convolutional codes are not considered. This is motivated by block-length and latency considerations. SRAM blocks are typically organized into blocks of size ranging from  $32 \times 32$  to  $512 \times 512$  [57]. This arrangement naturally puts a restriction on the block-length of any error correction code. For binary channels, graph based LDPC codes typically outperform the conventional bounded distance decoding codes for large block lengths, where bit-error probability is large. <sup>2</sup> As will be seen in Chapter 4, the error mechanisms in SRAM have low bit-error probabilities. Owing to this reason, only bounded-distance decoding based codes are considered. Asymptotic trade-offs between a

<sup>&</sup>lt;sup>2</sup>For example, for a binary symmetric channel with crossover probability p, the asymptotic storage capacity achieved by bounded distance decoding is  $1 - H_2(2p)$ , where  $H_2(.)$  is the binary entropy function in bits. The storage capacity (irrespective of coding strategy) is  $1 - H_2(p)$ . If p is close to zero, their relative difference  $\frac{H_2(p) - H_2(2p)}{1 - H_2(p)}$  is negligible.

graphical code's rate and asymptotic coding-energy scaling models have been studied by Grover and Sahai [52]. Using these models, supply voltage reduction and LDPC coding trade-offs can be studied in an asymptotic setting to establish upper bounds on power reduction. This has been left as a future work.

Supply noise issue is usually addressed by a 100mV extra margin on the supplyvoltage, to ensure proper functionality of SRAM [18, 19]. In this work, the same approach will be adopted. Thus, if  $v^*$  is found to be the leakage-power optimal supply voltage for SRAM, then  $(v^* + 100 \text{mV})$  will be the actual supply voltage. To simplify the exposition, leakage-power comparisons will be made *without* adding the noise margin. The extra 100mV margin will not change the nature of leakage-power optimization results. It must be noted that this is not the power optimal strategy. For example, in the case of standby SRAM, the supply noise will be much smaller due to zero circuit activity. Usually supply noise is observed at the clock edge, when the active logic blocks draw a large (but indefinite) amount of current [19]. Difficulties in moving away from this worst-case strategy and exploiting the statistics of supply noise will be discussed in Chapter 3.

Unlike traditional circuit optimization works, the focus here is on system level optimization without changing the SRAM cell parameters like transistor threshold voltage  $V_T$ , transistor channel length L, or transistor width W etc. This simplification leaves the cell-design and cell-area unaffected for the SRAM cell. The redundancy overhead of errorcorrection code will be accommodated in the optimization cost function in the next chapter. The exploration of joint circuit and system optimization has been left as a future work.

#### 1.3.2 Notation

The supply voltage will be denoted by v and any current will be denoted by i(t). In the special case of standby SRAM in Chapter 5, the standby supply voltage will be denoted by  $v_S$ . Average leakage-power (over random realizations of SRAM cells) at supply voltage v is denoted by  $P_l(v)$ . Data-lifetime and refresh time are denoted by  $t_0$  and  $t_r$ , respectively. The letter E is reserved for energy (of various types). The acronym ECC will stand for a generic error-correction code. Leakage-power per useful bit including the coding overheads will be referred to as *power per bit* and denoted by  $\mathcal{P}_b(v, t_r, ECC)$ . High supply voltage stands for  $V_{dd} = 1.0$ V. Error probabilities (of various types) will be denoted by the letter pand the letter r will be used for bit-error rate. The binary entropy function is denoted by  $H_2(p)$ . The letter  $\mathcal{E}$  will be used to denote error events. The symbols  $\mathbb{E}$  and  $\mathbb{P}$  will be used for statistical expectation and probability, respectively. Any vector  $(x_1, x_2, \ldots, x_j)$  will be denoted by  $x_1^j$ .

The standard threshold voltage 90nm CMOS technology will be called as 90nm CMOS technology or just 90nm technology. Similarly, the standard threshold voltage 65nm CMOS technology will be called as 65nm CMOS technology or just 65nm technology. The SRAM cell sizing cannot be disclosed due to non-disclosure agreement. Most of the presented simulation results are normalized due to the same reason.

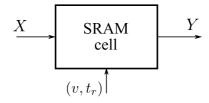

A bounded distance decoding based error-correction code will be represented by the [n, k, d] parameters [30,51]. Block length (total number of bits) is denoted by n, number of information bits is denoted by k, and d denotes the minimum Hamming distance of the code. A bounded distance decoding based code will detect up to (d-1) errors and correct up to  $u := \lfloor \frac{d-1}{2} \rfloor$  random bit-flips. The general probabilistic model of SRAM cell is illustrated in Figure 1.2. The SRAM cell has a binary bit  $X \in \{0, 1\}$  as input. The output is another

Figure 1.2: The channel model or probabilistic model of an SRAM cell is illustrated. X is a binary input and Y is a binary output. The conditional probabilities  $(\mathbb{P}[Y = y | X = x])$ depend on the supply voltage v and time  $t_r$ .

bit  $Y \in \{0,1\}$ . The error probability  $Y \neq X$  is controlled by the supply voltage v and the data-refresh time. Even though  $Y \in \{0,1\}$ , it will be shown later that a fraction of errors in SRAM cells can be converted into erasures. Thus,

$$Y = \times$$

, with probability  $p_x(v)$ ,

=  $\bar{X}$ , with probability  $p_e(v)$ ,

=  $X$ , otherwise. (1.1)

The  $\times$  symbol stands for 'don't care' or an erasure. The error probability  $p_e(v)$  depends on  $t_r$  as will be shown later.

The error-correction code and data-refresh based SRAM block diagram is illustrated in Figure 1.3. The bit-vector  $B_1^k$  for storage is encoded into  $X_1^n = f(B_1^k)$ . The vector  $X_1^n$  is stored in n independent and identically distributed (i.i.d.) SRAM cells with probabilistic model as described in (1.1). At each refresh cycle, the output bits  $Y_1^n$  are decoded into an estimate  $\hat{B}_1^k$  of the vector  $B_1^k$ . This estimate is re-encoded and stored back in the SRAM cells. With the notation in place, the overview of optimization framework is

Figure 1.3: The low leakage-power SRAM architecture studied in this work is illustrated. Information bits  $B_1^k$  are encoded into  $X_1^n = f(B_1^k)$ . Then  $X_1^n$  is stored in n i.i.d. SRAM cells. At each refresh cycle, the output bits  $Y_1^n$  are read and decoded into  $\widehat{B}_1^k$ . This estimate of  $B_1^k$  is re-encoded and stored back in the SRAM cells.

discussed in the next chapter.

# Chapter 2

# **Optimization framework**

# 2.1 Overview

As envisioned, the optimization problem has a leakage-power per stored bit (power per bit) cost-function which will be optimized over the choices of refresh time  $t_r$ , errorcorrection code, and supply voltage v. The constraint is set by a decoding error probability target. The cost function includes the refresh power overhead. The basic principle used to save leakage-power is supply voltage reduction. As supply voltage v is reduced, average leakage-power of SRAM cells decreases. The disadvantage of supply voltage reduction is an increase in the SRAM cell failure probability. <sup>1</sup> Recall that the prominent error mechanisms consist of parametric failures, supply noise induced failures, soft-errors, and oxide trapcharge induced SRAM  $V_{cc|\min}$  fluctuations. Among these errors, parametric failures do not accumulate with time, while other "noise" phenomenon based errors accrue with time. For these errors, system level techniques like error-correction codes and periodic data-refresh

$<sup>^{1}</sup>$ As discussed before in Chapter 1, the error mechanisms will be modeled in a statistical setup.

will decrease the decoding error probability of stored SRAM data. Both these techniques add power and storage (redundancy) overhead to the overall system. The tradeoff between these overheads and leakage-power reduction has to be explored.

The optimization constraint is that the decoding error probability of an SRAM block should be equal to the decoding error probability associated with [31, 26, 3] Hamming code based SRAM block at a supply voltage of v = 1.0V after the data-lifetime  $t_0$ . All Hamming codes fall into the category of single-error correcting double-error detecting (SEC-DED) codes. A SEC-DED code is chosen for target error probability since this is a common error-correction mechanism used in contemporary SRAM [33]. In this work, a data-lifetime of  $t_0 \geq 1$  sec is considered for the 90nm technology simulations, and a data-lifetime of  $t_0 \ge 10$  sec is considered for the 65nm technology simulations. The necessity of data-lifetime is explained next. Phenomena like soft-errors accumulate temporally and their timestamps are well modeled by discrete independent increment process. Thus, the decoding error probability will increase as the data-lifetime increases, since the probability of a bit in error increases with storage time. This bit-error probability coupled with error-correction code, will determine the decoding error probability. Therefore, the decoding error probability depends on the data-lifetime of interest. In this work, the data-lifetime is treated as a input parameter to the optimizer. Observe that the target error probability will increase as a function of this input parameter.

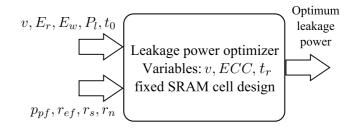

The optimization framework has the following ingredients: (i) a range of supply voltage v, (ii) average SRAM cell leakage  $(P_l(v))$ , (iii) average SRAM cell soft-error rate  $(r_s(v))$ , (iv) the spatial parametric failure probability  $(p_{pf}(v))$ , (v) the supply noise induced error rate  $(r_n(v))$ , (vi) the oxide trap-charge assisted error rate  $(r_{ef}(v))$ , (vii) the datalifetime parameter  $t_0$ , (viii) SRAM cell parameters such as read and write energy  $(E_r$ and  $E_w$ , respectively), and (ix) ECC parameters such as block length, information bits, minimum distance, and encoding and decoding energy. These parameters, except (ix), are expected as an input by the optimization program. Hamming and BCH error correction code families will be used as a variable in optimization [30]. A schematic diagram of the framework is shown in Figure 2.1. The encoding and decoding energy for error-correction codes were estimated using parity check complexity by standard cell library implementation in the 90nm CMOS technology. The coding energy parameter is not critical, since the coding power is amortized by the data-lifetime parameter.

Figure 2.1: A schematic diagram of the optimization is illustrated. Failure probabilities and rates of dominant error-mechanisms, corresponding supply voltages, data lifetime, and SRAM parameters are expected as an input. The optimizer predicts the best leakage-power achievable within some families of error-correction codes.

To evaluate the performance of this optimization framework, the optimization inputs will be estimated or simulated for the 90nm and 65nm CMOS technologies (*courtesy: ST Microelectronics*). For the 90nm technology, the supply voltage is discretized to the set  $\{0.3V, 0.4V, \ldots 1.0V\}$  and the optimizer computes *power per bit* on this set of input supply voltage. For the SRAM cell in 90nm technology, at 0.2V, the SRAM cell was not writeable.

The supply voltage set is  $\{0.2V, 0.3V, \ldots, 1.0V\}$  for the 65nm technology. The SRAM cell in 65nm was not writeable at 0.1V. This supply-voltage quantization step is flexible in the optimization program. Only for results presented in Chapter 4, this particular discrete set is chosen. Failure rates for various error-mechanisms at these discrete supply voltages will be estimated later (see Chapter 3). The read-write energy for SRAM cell, and the ECC encoding and decoding energy will be estimated by their values at a supply voltage of 1.0V for simplicity. These estimates will be pessimistic since these energies are expected to reduce with supply voltage. However, this approach saves simulation effort, and it does not changes the nature of *power per bit* optimization results.

For the 90nm technology, a short data-lifetime  $t_0 : t_0 < 1$ s is uninteresting from a leakage-power perspective. Leakage-power per cell for this technology is of the order of 1nA. Active energy needed to read or write a bit from SRAM is of the order of 10pJ. Therefore, for  $t_0$  below 10ms range, the leakage-power will be negligible compared to the active power. While this active power problem can also be addressed within a similar optimization framework, the optimization cost-function will change and hence it is beyond the scope of this work. In problems with large  $t_0$ , where leakage-power contribution to the total power is significant, the coding energy overhead becomes negligible after amortization by  $t_0$ . This observation is particularly useful for low duty-cycle and low power applications (like sensors using energy scavenging [58]). Similar arguments can be made for  $t_0 < 10$ s in the 65nm technology.

An intuitive explanation of leakage-power reduction is given next. Qualitatively speaking, depending on the supply voltage, the dominant failure mechanism is of a certain type. For the SRAM cell design under simulation, soft-errors dominate the bit-error probability and set the target decoding error probability at high supply voltage. At voltages less than 0.6V, the parametric failures dominate the bit-error probability. The soft-error rate increase with voltage reduction is not catastrophic, and it can be tackled by data-refresh, at a negligible power overhead for large  $t_0$ , till parametric failures begin to dominate. This is the prime reason why leakage-power reduction can be expected at an intuitive level. Further, as supply voltage reduces and parametric failures become dominant, extra a larger error-correction capability is needed to maintain a constant decoding error probability. This extra error-correction capability requires more parity checks or redundant bits, but parametric failure probability in the voltage-range of interest is close to zero. Therefore, only a small fraction of bits are used as parity checks<sup>2</sup> and it leads to efficient leakage-power reduction at a constant decoding error probability.

In summary, this approach differs from the traditional in the following way: Read, write, access, or hold may not be fulfilled for all voltages by all the SRAM cells. But as long as a large fraction of cells are functional, this negligible loss in functional SRAM cells can be made up by suitable error-correction codes. This work's main contribution is establishing trade-offs between error-correction, supply voltage, and leakage-power reduction – at a constant decoding error-probability.

<sup>&</sup>lt;sup>2</sup>Informally, if  $p_x \approx 0$ , then the binary entropy  $H_2(p_x)$  is close to zero, meaning that the Shannon capacity of the SRAM cell is equal to  $1 - H_2(p_x) \approx 1$ .

## 2.2 Probability models for SRAM cells

The probabilistic aspects of the optimization framework are discussed next. The classification of SRAM error mechanisms as errors and erasures is discussed first.

#### **Errors and erasures**

In coding theory, two types of errors are distinguished – errors and erasures. An error is a flipped bit where the SRAM cell affected by bit-flip is unknown. Strictly speaking, an erasure is a missing bit (or symbol). An SRAM cell that is *known to be* faulty can be reduced into an erasure by 'ignoring' the content of the known and faulty SRAM cell. In other words, a faulty SRAM cell will always output some value upon reading. If the value is known to be coming from a faulty SRAM cell, it can be ignored and labeled as an erasure. An erasure is similar to a don't care ( $\times$ ). The differentiation is important since an erasure is *easier* to decode compared to an error. In simple terms, no information from a bit in error (erasure) is better than incorrect information from a bit in error (flipped bit). This can illustrated using the following example:

**Example 2.2.1.** Consider the simplest repetition code (triple modular redundancy or TMR) for a single information bit with a block length of n = 3. The information bit to be stored is repeated 3 times in this coding scheme. Thus, codewords corresponding to bits 0 and 1 are (000) and (111), respectively. This code can correct one error or one erasure by using majority voting on the read-out bit. In general, this coding technique can correct two erasures or one error.

Let 0 be the information bit, and consider the two separate cases with two erasures

and two errors. The stored block will be (000). Since the code is symmetric, without loss of generality, assume that the first two bits are affected. Therefore,  $(\times \times 0)$  and (110) will be the error-affected codewords for the two cases. By ignoring the erasures or  $\times$ , the bit 0 can be successfully decoded. However, (110) decodes to the incorrect bit 1 when using the (optimal) majority decision rule.

Decoding errors and erasures together was studied by Forney under the concept of generalized decoding [59]. Some binary error-correction code families (e.g., BCH codes) jointly decode errors and erasures (generalized decoding). In generalized decoding, if an error-correction code has minimum Hamming distance d, then  $m_e$ -errors and  $m_x$ -erasures can be corrected if,

$$2m_e + m_x < d. \tag{2.1}$$

Loosely speaking, two erasures are equal to one error.

In contrast, let *specialized decoding* be the setup where defective SRAM cell bits are treated as errors. With  $m_e$ -errors and  $m_x$ -erasures, the total number of bit-flips in specialized decoding will be  $(m_e + m_x)$ . And, the condition for correct decoding is,

$$2(m_e + m_x) < d. \tag{2.2}$$

Observe that only the total number of bit-flips are important in specialized decoding. Comparing (2.1) with (2.2), a larger set of  $(m_e, m_x)$  positive integer pairs satisfy the condition for correct decoding in *generalized decoding*. Thus, it is expected that *generalized decoding* will have a smaller decoding error probability. Quantitative comparisons on this difference will be presented later in Chapter 4.

#### 2.2.1 SRAM cell failure mechanism classification