## A Platform-Based Approach to Low-Power Receiver Design

Yanmei Li

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-181 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-181.html

December 19, 2008

Copyright 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### A Platform-Based Approach to Low-Power Receiver Design

by

#### Yanmei Li

B.Eng. (Tsinghua University, China) 1998M.Eng. (Tsinghua University, China) 2001

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Alberto Sangiovanni-Vincentelli, Chair Professor Jan M. Rabaey Professor Peter J. Bickel

Fall 2008

#### The dissertation of Yanmei Li is approved.

| Chair Date  Date |       |      |

|------------------|-------|------|

| Date             | Chair | Date |

|                  |       |      |

|                  |       |      |

|                  |       |      |

|                  |       |      |

|                  |       |      |

|                  |       |      |

|                  |       | Date |

| Data             |       |      |

|                  |       | Date |

University of California, Berkeley Fall 2008

A Platform-Based Approach to Low-Power Receiver Design

Copyright © 2008

by

Yanmei Li

#### **Abstract**

A Platform-Based Approach to Low-Power Receiver Design

by

#### Yanmei Li

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Alberto Sangiovanni-Vincentelli, Chair

Driven by the desire of people to communicate more efficiently, more flexibly and more reliably, tremendous changes are occurring in the wireless world. As one of the dominant drivers for the semiconductor industry, the wireless evolution towards higher data rate and higher capacities presents numerous opportunities. However, it also introduces many challenges to the current design technology, particularly, the demanding requirement for low power or even ultra-low power consumption. The rapid growth of various wireless services increased the need for highly integrated and low-cost solutions with very demanding performances. The fast growing market and heated competition require very short system development cycle. To cope with this constantly increasing system complexity, higher performance demands and tight time-to-market constraints, it is imperative to develop new design techniques for wireless systems to cope with these challenges.

This dissertation presents a design approach for wireless systems where the design requirements are demanding in terms of contradicting objectives. The approach is based on the paradigm of *platform based design*, featuring in the adoption of higher

levels of abstraction, better reusability and early consideration of system performance. Wireless receivers are used to demonstrate the approach proposed here. A receiver is a complicated system consisting of RF, analog and mixed-signal components. Traditionally, when developing a wireless system, system design and circuit design are conducted separately. Our research shows that effective interactions between different levels are critical to obtain an optimal system. In this research, systematic design space exploration is necessary to facilitate the trade-off evaluations and system partitioning. To demonstrate this concept, the platform-based receiver system design is presented from system level down to circuit design, focusing on the minimization of the overall power dissipation while maintaining system performance. Two application scenarios are explored. One is a receiver front-end for an MB-OFDM UWB system. The other one is an ultra-low power mostly-analog baseband design for wireless sensor networks.

In the context of the proposed design approach, several representative challenges in the wireless receiver design are investigated, which include how to improve the system robustness against various interferences, how to quickly estimate the wireless system performance in an analytical approach, how to validate a system algorithm in a heterogenous simulation environment, how to build the abstracted behavioral models and use them to perform the design space exploration, etc. The circuit level design concerns and subthreshold design techniques are also demonstrated. Finally, system-level optimization is performed using behavioral models and, to preserve fidelity, the models are constrained by the achievable performance of actual circuit implementations. The resulting two designs show that significant power savings can

| be accomplishe | d through | systematic | design | space | ${\it exploration}$ | in | the | platform | -based |

|----------------|-----------|------------|--------|-------|---------------------|----|-----|----------|--------|

| design framewo | rk.       |            |        |       |                     |    |     |          |        |

Professor Alberto Sangiovanni-Vincentelli Dissertation Committee Chair

To my parents and my husband

## Contents

| C            | onter       | $\operatorname{nts}$ |                                                 | i    |

|--------------|-------------|----------------------|-------------------------------------------------|------|

| Li           | ${f st}$ of | Figur                | es                                              | v    |

| Li           | st of       | Table                | ${f s}$                                         | viii |

| $\mathbf{A}$ | ckno        | wledge               | ements                                          | ix   |

| 1            | Intr        | oduct                | ion                                             | 1    |

|              | 1.1         | Trend                | ls and Challenges in Wireless System Design     | 1    |

|              |             | 1.1.1                | Low Power Consumption                           | 2    |

|              |             | 1.1.2                | Increasing System Complexity                    | 4    |

|              |             | 1.1.3                | Technology into Nanometer Era                   | 5    |

|              |             | 1.1.4                | Systematic Design Methodology                   | 6    |

|              | 1.2         | Work                 | of this Thesis                                  | 7    |

| <b>2</b>     | Met         | thodol               | $\mathbf{ogy}$                                  | 10   |

|              | 2.1         | Tradit               | tional Design Approach to Transceiver Systems   | 10   |

|              |             | 2.1.1                | Design Flow                                     | 10   |

|              |             | 2.1.2                | Difficulties and Challenges                     | 12   |

|              | 2.2         | Recen                | at Progress                                     | 15   |

|              | 2.3         | Platfo               | orm-Based Approach to Low Power Receiver Design | 16   |

|              |             | 2.3.1                | Platform-Based Design (PBD)                     | 16   |

|              |             | 2.3.2                | Platform-Based Receiver Design Flow             | 18   |

|              |             | 2.3.3                | Application Scenarios                           | 21   |

| 3 | $\mathbf{Sys}$ | ${ m tem} \ { m Le}$ | evel Design                                    | 25  |

|---|----------------|----------------------|------------------------------------------------|-----|

|   | 3.1            | Syster               | m Exploration                                  | 25  |

|   |                | 3.1.1                | Functionality Partitioning: Digital vs. Analog | 25  |

|   |                | 3.1.2                | System Budget: Robustness vs. Low Power        | 30  |

|   | 3.2            | Model                | l and Validation                               | 32  |

|   |                | 3.2.1                | Analytical Approach                            | 32  |

|   |                | 3.2.2                | Modeling in Matlab: UWB System Validation      | 45  |

|   |                | 3.2.3                | Modeling in Metropolis                         | 47  |

|   | 3.3            | Syster               | m-Level Conclusions                            | 57  |

| 4 | Pla            | tform                | Exploration                                    | 61  |

|   | 4.1            | Archit               | tecture Level Exploration                      | 61  |

|   |                | 4.1.1                | Analog/RF Behavioral Model                     | 61  |

|   |                |                      | Behavioral Model for System Verification       | 62  |

|   |                |                      | Behavioral Model for PBD                       | 63  |

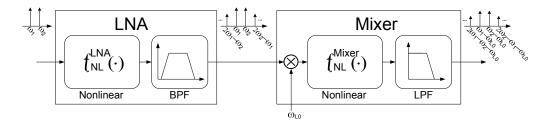

|   |                |                      | RF Front-End Modeling                          | 66  |

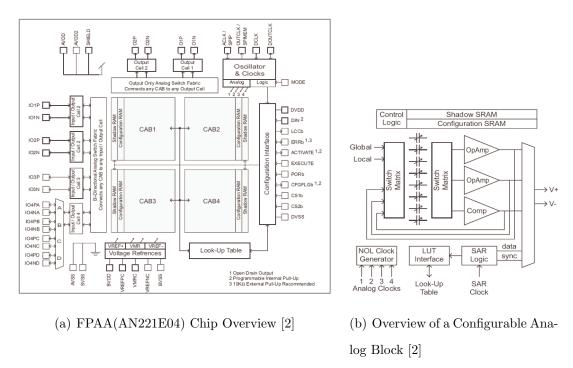

|   |                | 4.1.2                | Reconfigurable Platform                        | 69  |

|   | 4.2            | Circui               | it Level Exploration                           | 72  |

|   |                | 4.2.1                | Ultra-Low Power Analog Circuit Design          | 74  |

|   |                |                      | Subthreshold Circuit Design                    | 74  |

|   |                |                      | Device Model                                   | 76  |

|   |                |                      | IC-based Circuit Design Approach               | 79  |

|   |                |                      | Ultra-Low Power Baseband Circuit Design        | 82  |

|   |                |                      | Design Space Exploration                       | 85  |

|   |                | 4.2.2                | Low Power RF Front-End Design                  | 89  |

|   |                |                      | RF Circuit Characterization                    | 92  |

| 5 | Opt            | imizat               | tion and Implementation                        | 96  |

|   | 5.1            | Meet-                | in-the-middle Optimization                     | 97  |

|   | 5.2            | Silicon              | n Implementation                               | 100 |

| 6 | Cor            | clusio               | $\mathbf{n}\mathbf{s}$                         | 103 |

|   | 6.1            | Concl                | usions                                         | 103 |

|              | 6.2   | Future Research Directions | 105 |

|--------------|-------|----------------------------|-----|

| $\mathbf{A}$ | Inte  | er-modulation Products     | 106 |

|              | A.1   | WBI and NBI                | 106 |

|              | A.2   | WBI and WBI                | 116 |

| Bi           | bliog | graphy                     | 121 |

## List of Figures

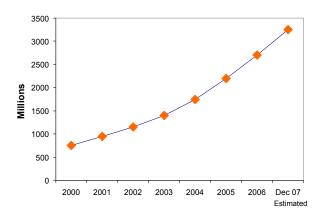

| 1.1  | Growth of worldwide wireless subscriptions (source: ITU World Telecommunication/ICT Indicators Database)                                                                                                                                                                                    | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

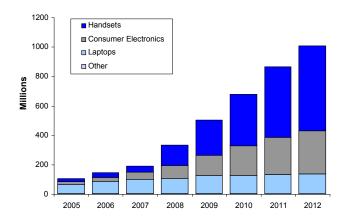

| 1.2  | Wi-Fi market projections (source: Skyhook Wireless)                                                                                                                                                                                                                                         | 3  |

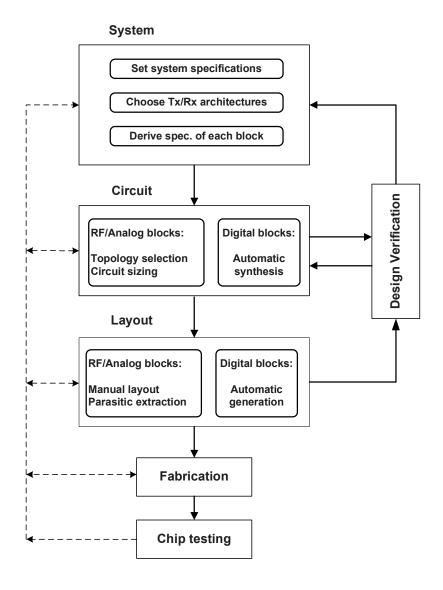

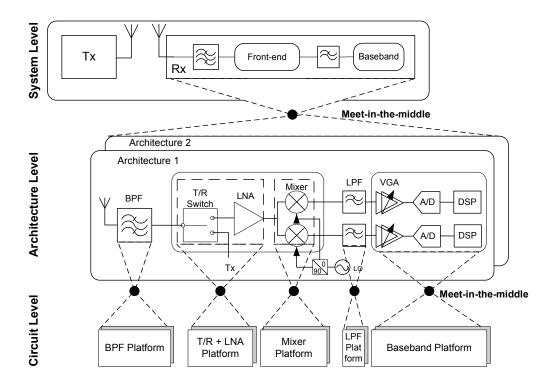

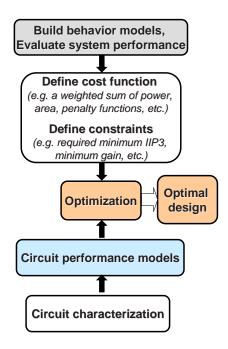

| 2.1  | Typical design flow of a transceiver system                                                                                                                                                                                                                                                 | 11 |

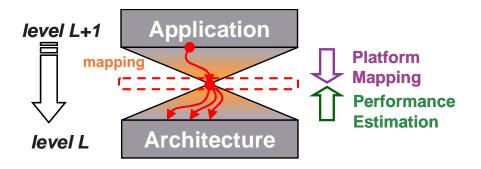

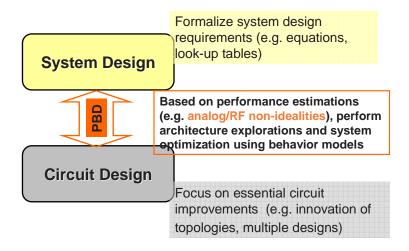

| 2.2  | Platform-based design (PBD)                                                                                                                                                                                                                                                                 | 17 |

| 2.3  | Platform-based approach to transceiver design                                                                                                                                                                                                                                               | 19 |

| 2.4  | Bridge the gap between two design layers                                                                                                                                                                                                                                                    | 20 |

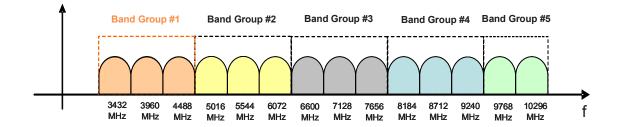

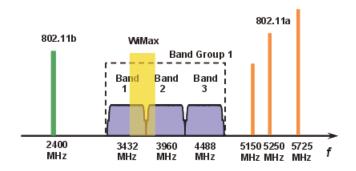

| 2.5  | MB-OFDM UWB frequency allocation                                                                                                                                                                                                                                                            | 22 |

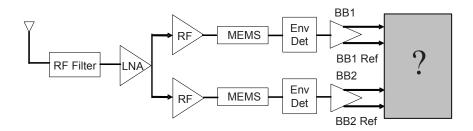

| 3.1  | Ultra-low power receiver for wireless sensor networks (WSNs)                                                                                                                                                                                                                                | 27 |

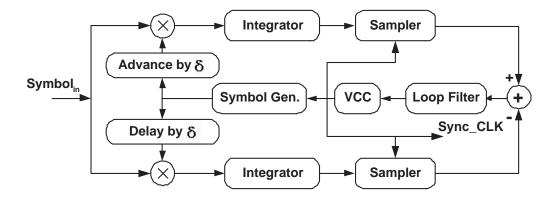

| 3.2  | Block diagram of Early-Late Gate synchronizer                                                                                                                                                                                                                                               | 29 |

| 3.3  | Interference scenario around UWB band group 1                                                                                                                                                                                                                                               | 31 |

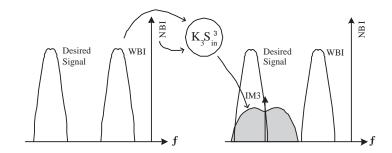

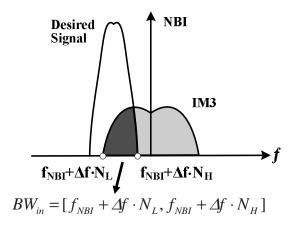

| 3.4  | XMD products of NBI (adjacent to the desired band) and WBI                                                                                                                                                                                                                                  | 38 |

| 3.5  | Third order IMD products of NBI and WBI                                                                                                                                                                                                                                                     | 38 |

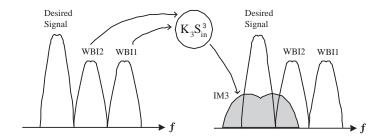

| 3.6  | Third order IMD products of WBI and WBI                                                                                                                                                                                                                                                     | 40 |

| 3.7  | For approximation of IMD products                                                                                                                                                                                                                                                           | 43 |

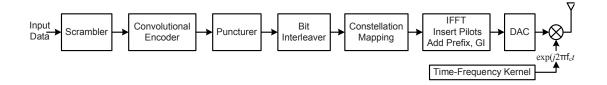

| 3.8  | Transmitter architecture of MB-OFDM UWB system                                                                                                                                                                                                                                              | 45 |

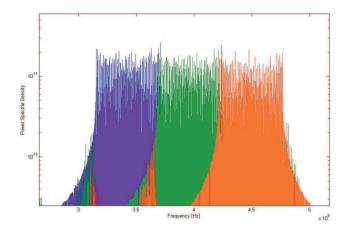

| 3.9  | Spectrum of an MB-OFDM UWB signal (band group I)                                                                                                                                                                                                                                            | 46 |

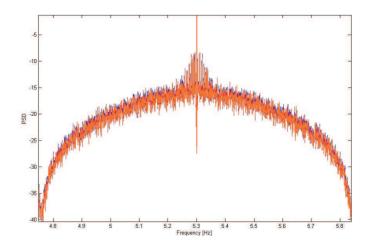

| 3.10 | Simulated PSD of an inter-modulation product                                                                                                                                                                                                                                                | 47 |

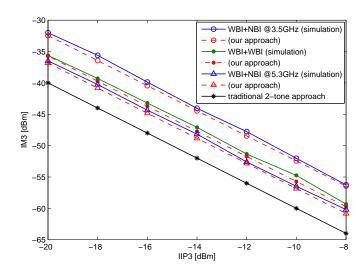

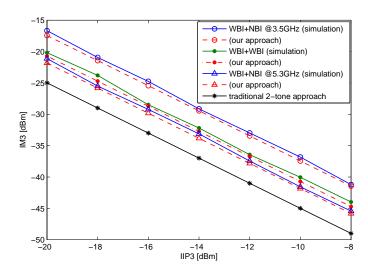

| 3.11 | In-band IM3 power from system simulation, our analytical approach, and the traditional two-tone approach. Three interference cases: NBI(5.3GHz) and WBI (band 3); NBI(3.5GHz) and WBI(band 3); WBI (band 2) and WBI (band 3). Desired UWB signal is in band 1. Interference power is -35dBm | 48 |

| 3.12 | In-band IM3 power. The interference cases are same as in Fig. 3.11. Interference power is -30dBm.                                                                                        | 49 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

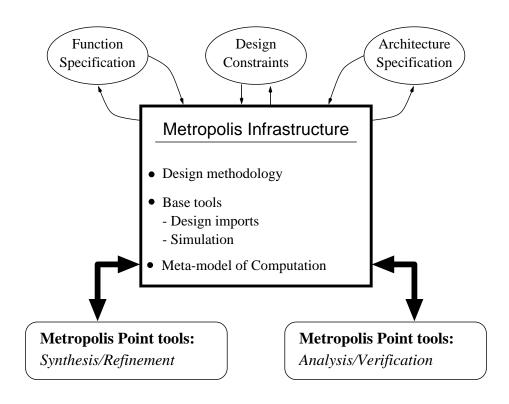

| 3.13 | Metropolis Infrastructure                                                                                                                                                                | 50 |

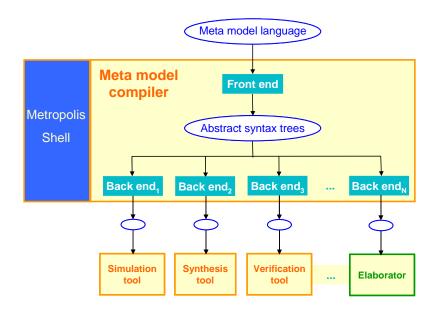

| 3.14 | Metropolis Tools Framework                                                                                                                                                               | 52 |

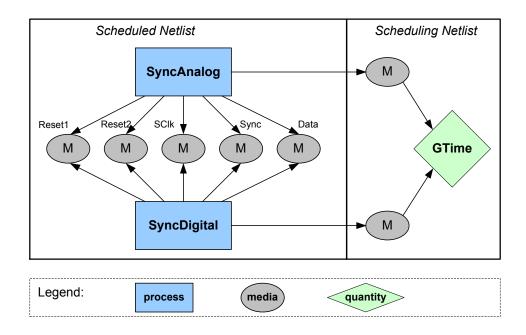

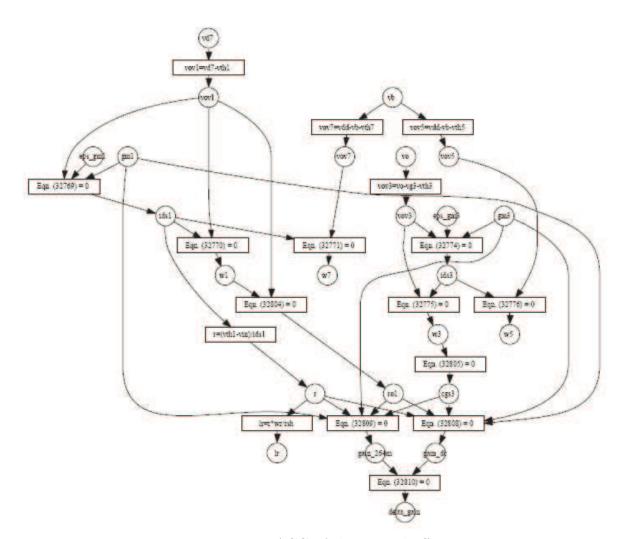

| 3.15 | Symbol Synchronizer Model in Metropolis                                                                                                                                                  | 53 |

| 3.16 | Symbol Synchronizer Model Simulation Result                                                                                                                                              | 57 |

| 4.1  | A behavioral model of the UWB receiver front-end                                                                                                                                         | 66 |

| 4.2  | FPAA overview                                                                                                                                                                            | 70 |

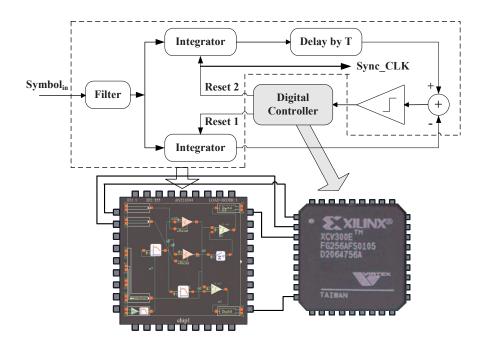

| 4.3  | Adapted Early-Late Gate synchronizer mapping on the FPAA-FPGA platform                                                                                                                   | 73 |

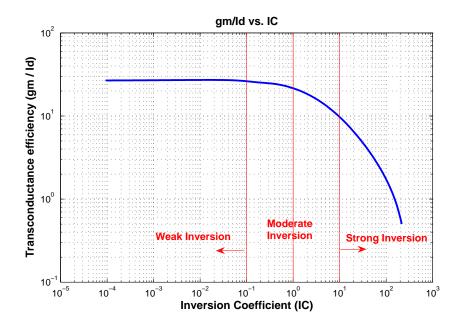

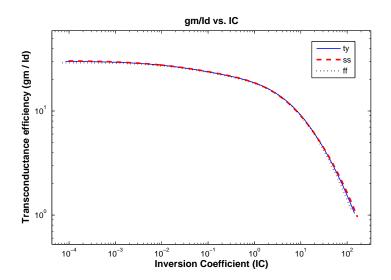

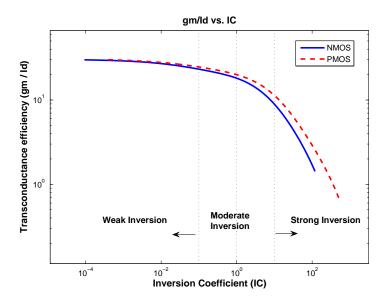

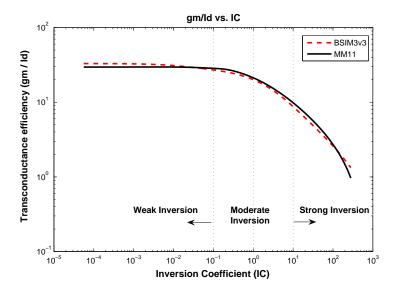

| 4.4  | Transconductance efficiency $(\frac{g_m}{I_D})$ vs. inversion coefficient $(IC)$                                                                                                         | 74 |

| 4.5  | $\frac{g_m}{I_D} \sim IC$ plots of different process corners (typical, slow, fast)                                                                                                       | 76 |

| 4.6  | $\frac{g_m}{I_D} \sim IC$ plots of different device types (NMOS and PMOS)                                                                                                                | 77 |

| 4.7  | $\frac{g_m}{I_D} \sim IC$ plots of BSIM3v3 model and MM11 model                                                                                                                          | 80 |

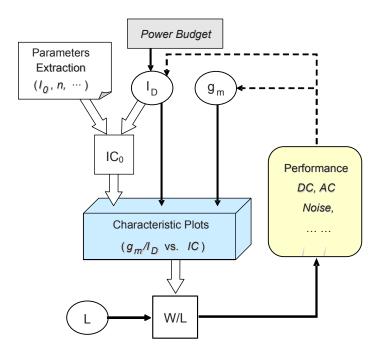

| 4.8  | IC-based low power design approach                                                                                                                                                       | 81 |

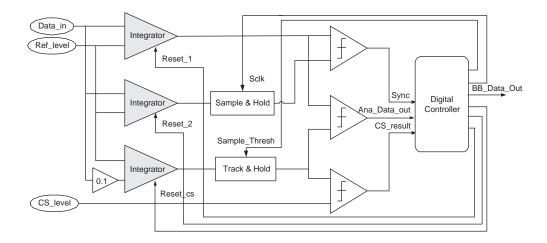

| 4.9  | Block diagram of the baseband silicon implementation                                                                                                                                     | 83 |

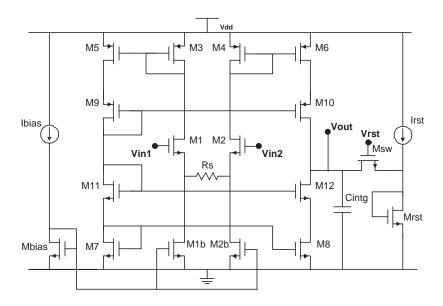

| 4.10 | Schematic of $G_m-C$ integrator with a symmetrical OTA                                                                                                                                   | 84 |

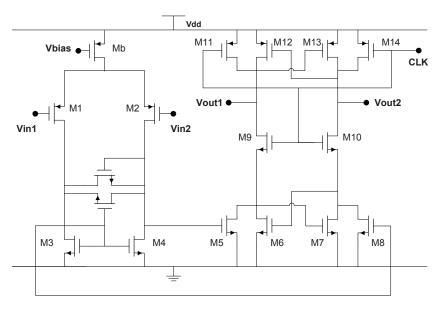

| 4.11 | Schematic of comparator                                                                                                                                                                  | 86 |

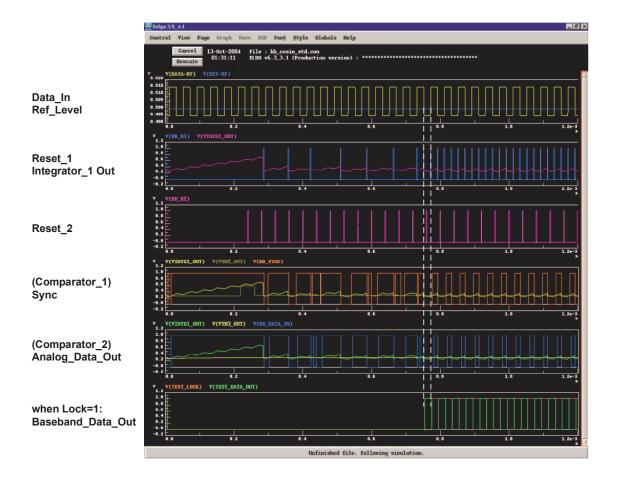

| 4.12 | Simulation results of the baseband circuits                                                                                                                                              | 87 |

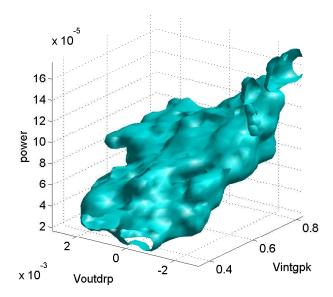

| 4.13 | Integrator performance space projection. The volume shows a feasible range of the integrator performance in terms of output voltage droop, integration peak level, and power consumption | 89 |

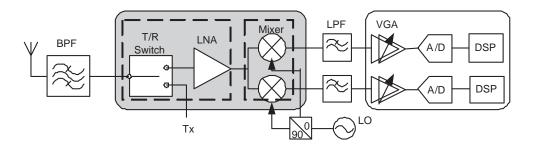

| 4.14 | Direct conversion UWB receiver architecture                                                                                                                                              | 90 |

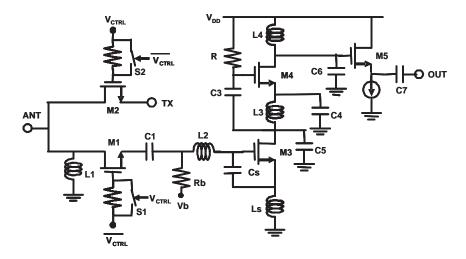

| 4.15 | Schematic of the $T/R$ switch and the stagger tuning LNA                                                                                                                                 | 91 |

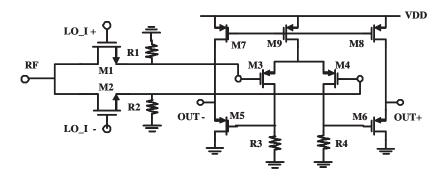

| 4.16 | Schematic of the Mixer and buffer                                                                                                                                                        | 91 |

| 4.17 | ACG of the mixer buffer                                                                                                                                                                  | 93 |

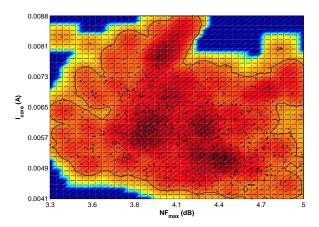

| 4.18 | A projection of LNA performance space. The area restricted by the boundary shows the achievable ${\rm NF}_{max}$ and current dissipation                                                 | 94 |

| 5.1  | Platform mapping                                                                                                                                                                         | 97 |

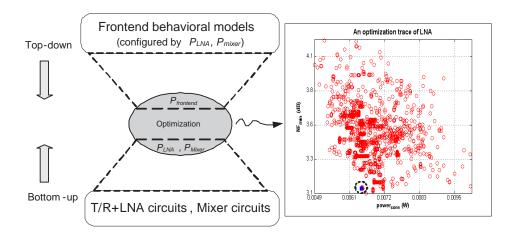

| 5.2 | meet-in-the-middle optimization process for the UWB front-end. The          |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | performance space $P_{LNA}$ and $P_{mixer}$ are generated from the circuit  |     |

|     | characterization. The front-end performance $P_{front-end}$ is evaluated by |     |

|     | means of its behavioral model. On the optimization trace, the square        |     |

|     | marker (within the dashed circle) indicates the optimal $NF_{min}$ and      |     |

|     | power consumption of LNA                                                    | 98  |

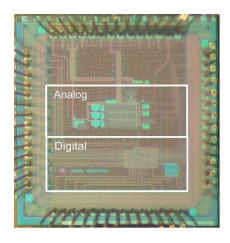

| 5.3 | Die photograph                                                              | 100 |

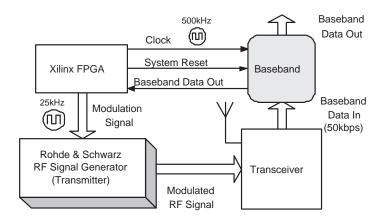

| 5.4 | Measurement setup                                                           | 101 |

| 5.5 | Baseband operation with the radio                                           | 102 |

## List of Tables

| 4.1 | Output harmonic and inter-modulation products | 68  |

|-----|-----------------------------------------------|-----|

| 5.1 | Performance Comparison                        | 99  |

| 5.2 | Baseband Design Summary                       | 102 |

#### Acknowledgements

When looking back over my study journey at this wonderful place, Berkeley, I want to say that it was indeed a challenging but rewarding experience. There are many people who have impacted my work and my life in these years. Without them, it was impossible for me to complete my Ph.D..

First and foremost, I would like to thank my advisor, Professor Alberto Sangiovanni-Vincentelli, for the great opportunity he offered me to work with him and for guiding me through the research. His sharp vision on cutting-edge research and broad experience led me to the interesting research topics. His continuous support, valuable advice and encouragement during times of frustration have been critical for me through all these years. His enthusiasm for his career would always inspire me in the rest of my life.

I am also fortunate to have Professor Jan Rabaey as my co-advisor. I would like to thank him for taking me on to the Picoradio project and getting me involved in his research group at Berkeley Wireless Research Center (BWRC). His grand vision and broad knowledge on EDA and circuit design (especially in low power) have inspired and guided my work crossing these two areas. He is one of the most energetic people I have ever met. What I have learned from him is not only on research, but also on life.

I would also like to thank Professor Peter Bickel for serving on my qualifying exam and my dissertation committee, for his valuable comments on this research. I am also very grateful to Professor Seth Sanders, who was a committee member of my qualifying exam and the instructor of my first analog circuit class at Berkeley. My appreciation also goes to Professor Kurt Keutzer, who was my temporary advisor during my first semester at Berkeley. He gave me valuable suggestions on my study plan. I also had the privilege to be hooded by him.

I thank my colleagues at the D.O.P. center, for the interesting discussions and the great time we spent together: Fernando D. Bernardinis, Alvise Bonivento, Adam Cataldo, Rong Chen, Abhijit Davare, Doug Densmore, Cong Liu, Trevor Meyerowitz, Alessandra Nardi, Roberto Passerone, Claudio Pinello, Alessandro Pinto, Xuening Sun, James Wu and Qi Zhu. In particular, I want to thank James Wu for helping me on the front-end circuit design. He also helped maintaining a great collaboration with UMC. I also want to thank Fernando D. Bernardinis, who was my mentor when I started my research in Alberto's group. The discussions with Fernando have been detailed and very helpful. We collaborated on part of the research that is presented in this dissertation and coauthored papers and technical reports.

I also want to thank Jan's group and other colleagues at BWRC for the inspiring discussions. I will never forget the interesting Friday meetings and seminars. In particular, a deep appreciation goes to Josie Ammer, Brian Otis, Nate Pletcher, Huifang Qin, Johan Vanderhaegen and Stanley Wang, for their help and/or collaboration on the Picoradio baseband project.

Another group of people that I would like to thank is the excellent office-mates I had in 545F Cory Hall: Satrajit Chatterjee, Shauki Elassaad and Trevor Meyerowitz, who shared their interesting research and industry experiences, funny stories, cookies and chips with me.

A special thank goes to Ruth Gjerde in the Graduate Student Affairs office for her great help and patient guidance since my first day at Berkeley.

This work was supported in part by SRC and the MARCO-sponsored Gigascale Systems Research Center (GSRC). I thank all the sponsors and industrial collaborators who supported this research. In particular, thank ST Microelectronics for fabricating the baseband chip. Thank UMC for providing a challenging application and very supportive resources.

During my stay at Berkeley, I have been so lucky to have these great Chinese friends: Li Yin, who has always been available to offer her advice and help whenever I needed; Jinhui Pan, Xu Zou, Yunjian Jiang and Weidong Cui, who have been my good friends since the years in Tsinghua University, and have given me lots of help since the first day I arrived at the United States; Rui Xu and Jianhui Zhang, with whom I have shared very important moments and wonderful vacation trips; Huifang Qin, who has given me very helpful advice and encouragement; Jing Yang, who was my great partner fighting together on the circuit class projects and became my good friend; Yang Yang and Qi Zhu, who helped me a lot when I was finishing up my dissertation. I want to thank all of them for their generous help and support. I am also very grateful to Yu Cao, Yuen-Hui Chee, Minghua Chen, Zhanfeng Jia, Jieli Li, Yaping Li, Qingguo Liu, Wei Mao, Cheongyuen Tsang, Hongwei Wang, Wei Wei, Fang Yu, Min Yue, Haibo Zeng, Yang Zhao, Wei Zheng, Janie Zhou, and Ye Zhou. I want to thank them for all the fun time we shared in these years. A special thank goes to the little angel, Shubo, whose smile always brightens my day.

Last but not least, I would like to thank my families. I can not find the words to describe to what extent I am grateful to them. I want to thank my parents for teaching me to be brave and optimistic. I thank my brother for taking care of the family. The unconditional love and support from my family has been a source of strength for me throughout my entire student life. Finally, I want to thank my husband, Guang, for being so supportive and patient. It was his sacrifice that made my life at Berkeley a happy journey since the first day. His love and encouragement carried me through the tough times.

### Chapter 1

### Introduction

In the past several decades, wireless communication technology has brought dramatic changes to this world. It has become an integral part of everyone's life. With the rapid evolution of wireless technologies, a mobile phone is not merely a simple voice centric device, but also an Internet browser, a camera and a compact entertainment center. You can use your cellular phone to get a driving direction or find a nearby restaurant quickly when you are on the road, or enjoy a real-time TV program when you are waiting for a flight. Driven by the desire of people to communicate more efficiently, more flexibly and more reliably, tremendous changes are occurring in the wireless world.

# 1.1 Trends and Challenges in Wireless System Design

According to the statistics from ITU World Telecommunication, the market of wireless mobile devices has experienced an explosive growth in the last decade to fulfill people's increasing need. As shown in Fig. 1.1, the worldwide mobile subscribers have

Figure 1.1. Growth of worldwide wireless subscriptions (source: ITU World Telecommunication/ICT Indicators Database)

increased from around 800 millions in 2000 to over 3 billion in 2007. Another set of data, as shown in Fig. 1.2, demonstrates the rapid growth of Wi-Fi services. The number of Wi-Fi users is expected to grow to nearly a billion in the next 5 years.

The tide of wireless evolution towards higher data rate and higher capacities has motivated numerous new research topics in related areas. The growth of various wireless services increased the need for low-cost highly integrated solutions with very demanding performance. Wireless applications have been and will remain being one of the dominant drivers for the semiconductor industry. On the other hand, the dramatic progress in IC technology has enabled small-area and low-power implementation of sophisticated systems. From the perspective of wireless system implementations, we can see several main trends as following.

#### 1.1.1 Low Power Consumption

In portable wireless applications, low power consumption is one of the critical requirements that designers make a great deal of efforts to achieve. As advanced multimedia and entertainment applications are becoming must-have features, apparently

Figure 1.2. Wi-Fi market projections (source: Skyhook Wireless)

higher power demand will be inevitable to realize the multi-functions. Therefore, it is more critical to develop new low-power techniques.

Other recent emerging applications, such as wireless sensor networks [41], have gained many interesting applications, such as improved human health monitoring, fire detection in forests, environmental control in smart buildings, etc. Shrinking semiconductor cost makes these areas more attractive. In a wireless sensor network consisting of a large number of distributed nodes, replacing batteries at regular instants in battery-powered nodes is impractical. It will be advantageous for the sensor nodes to be able to scavenge the energy from the environment. For this purpose, it is critical to pursue design solutions that reduce the power consumption as much as possible. This kind of systems pose extremely aggressive power dissipation challenges.

A new generation of wireless communications, 4G system, has attracted many attentions, targeting an "all-in-one" handset that enables seamless integration and fast communication between wireless devices across diverse wireless standards in different environments (from indoor networks such as WLANs and Bluetooth, to cellular signals, radio and TV broadcasting, and satellite communications) as well as broad-

band networks. This new generation of mobile devices offering faster speed and more functions is expected to appear in the market by the end of this decade [25, 51]. Maintaining a power efficient design in the multi-function multi-standard 4G devices is one of the main tasks to tackle.

As the system performance requirements and the bandwidth demand increase, power conscious design becomes more difficult than before. Using a low voltage process technology is helpful to some extent in reducing the power consumption, but not sufficient enough if it is the only strategy. The stringent power dissipation constraints require dedicated efforts at every stage of design - system planning, architecture, software, algorithm, logic design, circuit design, and so on.

#### 1.1.2 Increasing System Complexity

In the extremely competitive market, wireless systems are driven to higher levels of integration to achieve smaller physical size and lower cost. The integrated transceivers are quite complicated systems, including RF (Radio Frequency) blocks, analog blocks, and mixed-signal blocks together with digital circuitry on the same chip. Managing an efficient transceiver budget is one of the most compelling tasks the designers are facing. For instance, many tradeoffs have to be balanced due to the interdependency among the noise, non-linearities, gain, sensitivity, and selectivity.

The situation is even more challenging when the wireless system is designed to provide cost effective multi-function service. Besides high speed wireless communication capabilities, demanding functionalities also include positioning, aggressive multimedia and business applications, financial service, etc. When more and more functions are squeezed into a single system, the level of complexity is increased with the need to keep the system performance high (e.g. sensitivity, interference performance, etc.) and the power consumption low. The design tradeoffs and implementation options

inherent in meeting these demands highlight the extremely challenging requirements for a transceiver system.

Usually, even with the increasing complexity of the digital part, the RF and analog parts remain to be the bottleneck of the whole system design process, posing a main barrier of shrinking the entire design cycle. Especially, for a RF design, challenges lie not only in achieving successful operation at a relatively high frequency of 1-2 GHz, but also in doing so for widely varying application environments, under tight constraints such as cost and power consumption. From the system-level point of view, it is critical to understand and manage the effects from the multi-dimensional performance space of RF and analog components. To achieve that, Electronic Design Automation (EDA) methodologies and tools are desired to undertake the task managing the increasing design complexities in tight time-to-market requirements.

#### 1.1.3 Technology into Nanometer Era

The rapid evolution of semiconductor technology is one of the main contributors to the explosive growth of wireless applications. As in Moore's law, the number of transistors on a chip has increased exponentially, doubling approximately every two years. The CMOS technology is evolving deeper and deeper into the nanometer era, 90 nm, 65nm and even 45nm. This has brought faster, denser logic for less power, at lower cost per function, and also allowed more complex systems to be integrated on a single chip.

While the advanced technology is always preferred for cost reduction and system performance improvement, the designers, especially RF designers, have to handle the significant challenge of moving the design from one technology node to the next. For digital designers, the process of technology migration is known. However, the transition to new technologies brings along significant challenges to RF and analog

designers, for instance, to maintain a reasonable dynamic range and signal to noise ratio, which are proportional to the supply voltage. With the tight time-to-market constraint, it is crucial to migrate the design generation effectively, particularly when the supply voltage is lowered with the technology scaling. Proper design methodologies and tools that can facilitate this technology migration for RF and analog design and increase designers' efficiency are still missing.

When the technology moves to the nanometer era, considering the prohibitive cost of a mask set, it is more urgent than ever to be able to complete a new product in least number of silicon re-spins, preferably a first-pass silicon. Thus it becomes imperative to improve the modeling, simulation and verification techniques to achieve a higher rate of first-pass silicon success.

#### 1.1.4 Systematic Design Methodology

Nowadays, the system level design of transceivers is usually performed using spreadsheets. This method is limited in the number of different design possibilities it can explore within a given time. More effective design space exploration is desired since more significant improvement in cost and performance can be made in the system planning and architecture selection phases.

In comparison with their digital counterparts, the analog and RF components have a much longer design cycle. Besides developing the circuit topologies, it also takes the designers numerous efforts to adjust the device parameters and various circuit configurations. Moreover, the RF and analog circuits are also noticeably sensitive to a wide range of parameters including parasitic effects, substrate effects, packaging effects, etc. Due to the limitations of the available EDA tools for RF and analog circuits, most of the analysis and design work still highly depends on the circuit designer's judgement, making the solution less than optimal in terms of efficiency

and quality. Furthermore, whenever the block specification is changed, it takes a long time again to translate this change to the circuit parameters. The entire design process highly relies on the designer's experience.

The increasingly competitive market of wireless applications forces higher pressures on time to market. For example, the design cycle of a handset has been pushed from the typical 2 years to the target of 6 months, or even more compressed. To deal with constantly increasing complexity and time-to-market pressure, there is clearly a need for a new design methodology to support the trends and handle the challenges mentioned above. Recently, several EDA tools have been developed in this perspective [3, 17, 23]. But they provide very little help to the designers on the entire design flow and the system level optimization.

A fundamental problem of the current design methodologies is that an effective interaction is missing between system level design and circuit level design. To achieve an optimal solution on the system level, one of the biggest challenges for the designers is to understand somewhat unrelated disciplines such as RF and analog circuit design, circuit modeling and characterization, and digital communications. Having a complete design flow from system to silicon, such as the one described in this thesis, we believe we can increase the design productivity significantly.

#### 1.2 Work of this Thesis

In this thesis, I present a systematic design approach for wireless systems where the design requirements are demanding in terms of contradicting objectives, such as high performance requirements and low power consumption. The proposed methodology helps the designers balance various tradeoffs and make the optimal choices at system level. Using this approach, the chance of first-pass success will be greatly increased.

The approach is based on the paradigm of platform based design, featuring in the adoption of higher levels of abstraction, better re-usability and early consideration of system performance. Besides the platform-based design flow, this dissertation also makes a claim that low power design efforts should be taken into consideration at all design layers. The rest of this dissertation is organized as follows:

In chapter 2, the main difficulties of the traditional design approach are analyzed. The idea of platform-based design is introduced and a design flow leveraging the new abstraction levels is detailed. Following that, two challenging application scenarios requiring the minimization of power consumption are explored to demonstrate the effectiveness of this approach. These two applications are in radio frequency and in low frequency respectively, representing different design challenges. I use them to demonstrate different aspects of the new approach.

The systematic design effort starts with the system level exploration in chapter 3, where the representative design challenges of receiver systems are investigated, such as functionality partitioning between analog domain and digital domain, system robustness against the various interferences, etc. For modeling and validation purpose, an analytical approach and a simulation-based approach are discussed. To perform accurate estimation of the interference effects, a new analytical approach is proposed and validated. Furthermore, the critical concerns of validating a mixed-signal system in a heterogenous simulation environment are addressed in Metropolis.

Chapter 4 demonstrates the platform exploration approaches at the architectural level and the circuit level. Behavioral models are introduced to describe the functionality of the RF/analog blocks on a higher abstraction level. The specific requirements on behavioral models are addressed, and a concrete model for an RF front-end is generated. After that, reconfigurable devices are also discussed as a candidate platform to perform architectural exploration. The second part of this chapter focuses on the

circuit level exploration. A subthreshold circuit design technique and the associated device models are presented. This part also discusses the analysis and design of the specific circuitries for the two low-power applications. As a critical step of the platform-based design flow, circuit characterization is carried out to explore the circuit level design space. As a result, the circuit performance models are generated.

In chapter 5, based on all above design explorations, optimization is done in the context of platform mapping. The resulting low power implementations are reported, testifying the effectiveness of the platform-based receiver design approach. This chapter also shows the testing results of a silicon implementation.

Finally, chapter 6 concludes the dissertation with a summary and a discussion of future research directions.

### Chapter 2

## Methodology

## 2.1 Traditional Design Approach to Transceiver Systems

#### 2.1.1 Design Flow

The top-down design process of a wireless communication system can be summarized in the diagram (Fig. 2.1). At system level, the design specifications are usually set by the addressed wireless standard. The standard sets a profile of the surrounding wireless environments, including the adjacent channel selectivity, blocker profile, and so on. Based on these, the system designer will derive a set of transceiver specifications, such as intermodulation requirements, noise figure, linearity requirements, etc. The next task of system design is to make the functional decomposition, select the transceiver architecture and derive the specifications of each building block. Traditionally, hand calculations or spreadsheets are used during this system level architectural design. For simulation purpose, Matlab/Simulink are often used, where some block models with non-idealities are available in the library.

Figure 2.1. Typical design flow of a transceiver system

Having the block specifications, the design process proceeds to the block architecture exploration and circuit design. In this stage, digital circuits can be dealt with by automatic synthesis. While RF and analog circuit design heavily rely on the designers, including topology selection and circuit sizing. Simulations are exploited to get accurate performance estimates at circuit level. Low frequency analog circuits are usually simulated with SPICE (or SPICE-like tools), which provides DC, AC, noise and transient analysis. Since RF signals usually consist of a high frequency carrier

modulated with a low frequency signal, and the difference of their frequencies can be as large as several order of magnitude, the normal transient simulations are very time consuming. Some dedicated RF simulators, such as SpectreRF[15, 16], have been developed to solve this problem, providing periodic and quasi-periodic, and transient envelope analysis.

After the circuits have met the specifications, the next stage is the layout generation. Again, automatic layout generation tools are available to the digital circuits. For RF and analog circuits, the circuit performances are very sensitive to the parasitic factors. The device layout, and the placement and routing have to be performed manually. Beyond that, before the chip is sent out to fabrication, parasitic extraction and post-layout simulation of the RF/analog circuits are also needed.

#### 2.1.2 Difficulties and Challenges

#### 1. System Optimization

To win in the competitive market, an optimal system should not only provide the desired functions with maximal performance, but also demonstrate the advantage of smaller physical size and efficient power consumption. As these objectives are conflicting to each other, a big challenge to achieve them is to balance the tradeoffs at the system level. On the other hand, it is more important in practice to achieve an implementable solution, even having to sacrifice the optimum to some extent. Changing system-level specifications in the later design stages should be avoided since that will cause big changes at the lower design levels, even a complete start from scratch. Keeping that in mind, the system architect usually sets some margins when evaluating the tradeoffs and derive the block specifications. A system designed in this way is seldom an optimal design, just an implementable one.

Another reality is that design space exploration at system level is rarely performed due to the intrinsic complexity and the time-to-market pressure. However, better solutions in terms of performance and cost can be found by exploring various architectures, attempting different performance partitions or playing with the design margins. Though it has been acknowledged that the significant impact comes from the highest design level, the design space exploration at system level is still very limited and is hard to integrate into the design flow unless a systematic approach is developed.

Due to the absence of an inter-level interaction, the optimization objectives are only addressed at a specific level if there is any. For instance, at the circuit level, lots of manpower is dedicated to analog circuit sizing to minimize the power consumption and area while meeting the performance requirements. Since this type of optimization efforts are conducted only at the "local" level, the results make limited impact on the same objectives at the "global" level. Consequently, the entire system is still less than optimum though considerable time and resources have been spent for the optimization purpose.

#### 2. Design Iteration

If we consider the entire design process, iterations (shown by dash lines in Fig. 2.1) among the different design stages also take a considerable portion of the design cycle. For instance, the block specifications can not be satisfied on the circuit level after trying different topologies and a few attempts of circuit sizing. The design will have to go back to the system level, where the architect needs to make a new performance decomposition or even change the architecture, and derive a new set of block requirements to propagate to the circuit level. Similar iterations could also occur if the post-layout simulation demonstrates a failure to meet the minimum performance requirements, that unfortunately needs to go

back to the higher levels (circuit level or even the system level) and apparently requires more efforts to fix the failure.

One of the main reasons that possibly causes the iterations is the gap between the different design levels. Usually, two different groups of people work on the system level and the circuit level. Their expertise are in different areas, e.g. system architect in communication and algorithms, and circuit designers in circuit analysis and design. The design and simulation tools are also applied on the particular level, not crossing the different levels. Consequently, there is no effective interactions to cover the gap between different levels, that possibly leads to time-consuming design iterations. The system architect does not have enough knowledge of the lower levels, and commonly, the performance and cost evaluations are still unknown at that design stage. All of these can bring about some block specifications that are infeasible at the circuit level. So, reducing the possibility of cross-level design iterations is key in meeting the increasingly tight time-to-market constraints.

#### 3. Circuit Sizing

At the circuit level, in contrast to the digital parts, the RF and analog parts are the bottleneck of the entire system design, in terms of performance, design time, and cost. The RF/Analog design consists of two phases, topology selection and circuit sizing. Topology selection is more like a heuristic process, requiring the designer's knowledge and expertise. Therefore, traditionally it is a manual process. Though there are many existing topologies for those commonly used blocks, novel topologies are continuously developed to enhance performance to meet the aggressive requirements.

During circuit sizing, to meet the performance requirements and reduce various cost (power consumption, chip area, etc.), designers calculate and adjust

the circuit parameters, including component values and dimensions (width and length of transistors, values of resistor, capacitor and inductor, etc.) and circuit configurations (bias current, reference voltage, etc.). In RF/analog circuits, the performance is inevitably degraded by intricate sources, such as various noise sources, non-ideal effects, parasitics, etc. This makes the circuit sizing a complicated and time-consuming task. Whenever the block specifications are changed, it takes a long time for the designers to propagate the changes to the circuit parameters, even if the topology remains same.

#### 2.2 Recent Progress

Advanced design approaches and supporting EDA tools are critical in successfully going from system planning to chip fabrication while meeting the increasingly tight time-to-market constraints. Enormous research effort has been made to provide RF/analog designers with EDA tools to ease their job at different design levels.

These tools and methodologies focus on different aspects of RF/analog design [24, 46, 52, 17, 23]. Behavioral models of RF/analog blocks are important to accelerate the system simulation and verification. Some work focused on the macromodeling techniques for RF/analog blocks [54, 21, 34, 45, 38, 50]. For communication circuits, it is critical to understand and model the nonlinear distortions. Some work analyzed and modeled various nonlinear effects [22, 55]. For RF circuits, fast and accurate simulation is highly desired by designers. Some simulation techniques have been developed [31]. In communication system, especially in RF circuits, parasitic effects can have significant impacts on the circuit performance. There are some efforts trying to analyze and model the parasitic effects [26]. From the optimization point of view, some tools were developed to help designer optimize a circuit design based upon a topology starting point [28]. There are also a number of tools and methodologies

that help design some specific blocks, for instance, [27] discussed ADC design and optimization, [29] developed a modeling approach for PLL. On the commercial side, there are also some tools, such as Agilent ADS [1], Ansoft [3], providing models and simulation environment for the analog/RF blocks.

# 2.3 Platform-Based Approach to Low Power Receiver Design

As mentioned above, there are a number of design and simulation tools that focus on the various design steps from system planning to silicon implementation. They improve the design process here and there, however, there is limited work that addresses the complete design flow and system-level design. Especially, there is a clear need for an efficient approach that can perform design space exploration at the system level and facilitate an effective system design. A new design approach has been developed in this thesis to address these challenges.

#### 2.3.1 Platform-Based Design (PBD)

The methodology should be applicable seamlessly at all levels of abstractions and can capture design constraints and components at each level. In addition, the methodology must favor a system view of the design so that it can deliver an increased productivity and the capability of dealing with multiple design goals, thus always keeping in mind performance, power, reliability and cost as essential characteristics of the final solution.

The platform based design methodology has been proposed and applied in several application scenario [47, 49, 48]. In platform based design, the design problem is to

Figure 2.2. Platform-based design (PBD)

identify a stack of platforms that successively map the system from design specification to the lower levels platforms all the way to an actual implementation (e.g. silicon chips). At each layer of the platform stack, the platform needs to be configured to reflect the merits and limitations of the lower level resources. This process not only requires the matching between the functionality and the platform resources, but also keeps the performance sets from the platform resources in the design and analysis loop.

More specifically, we define a *platform* as a library of components, each decorated with a set of methods to estimate performances and behavior and to provide correct ways of composing them. Platforms can be at different level of abstractions, such as custom designed circuits or reconfigurable components (e.g. FPGAs). The design process is a *meet-in-the-middle* approach, as shown in Fig. (2.2). First, a library of components (platform) are characterized by extracting accurate models that include methods to compute physical quantities such as timing and power dissipation. This description of the components is used to offer the designer a way of exploring trade-offs when mapping the application to a legal composition of the platform components, called a *platform instance*. Because platform performances can be readily evaluated, efficient optimization can be carried out to perform design space exploration. The

accurate performance models available with platforms guarantee implementability of selected performances so that design can proceed to the next level down the hierarchy.

## 2.3.2 Platform-Based Receiver Design Flow

It is common that the system architects and the circuit designers focus on the problems coming from their "local" layers. Without digging into the problems in other layers, they can hardly optimize the design at the whole system level, but just limited at the local layers. A company rarely has the bandwidth to explore the systematic cross-layer interactions. An immediate consequence of that is the longer time-to-market, because it is quite usual that lots of manpower is spent on fixing problems caused by the ad-hoc cross-layer interference, iterating the design process, or even re-spinning. A new design approach that can cover the gaps across layers, such as between the communication layer and the circuit layer, will fulfill this need. Furthermore, a more formal design procedure is more preferable in contrast to the intuition-based system partition and constraint propagation.

From another perspective, system verification is very essential to increase the first-pass silicon success. Low level simulation of a large system is quite computationally intensive and should be avoided if possible. This problem becomes more challenging when the system consists of RF, low-frequency analog, and digital blocks. Building behavioral models at a higher abstraction level is considered as an effective solution to tackle the verification challenges.

As we all realized, the highly competitive market pushes for fast development of more powerful wireless communication systems. The design challenges and tight time-to-market can not be successfully conquered only at the circuit level through new topology development and exhaustive simulations. This indeed calls for a new design science, different from traditional design methodologies.

Figure 2.3. Platform-based approach to transceiver design

We propose a platform-based approach to receiver system design, as illustrated in the diagram (Fig. 2.3). The first thing is to define appropriate levels of abstractions that have to be traversed in the design process. These levels are not necessarily common to all receiver designs as they can be customized to the particular application at hand. As an example, we identify three levels of abstraction: a system level, an architecture level and a circuit level. This decomposition is useful to simplify design space exploration by limiting the range of alternatives that must be analyzed. Another consideration to define the proper abstraction levels is for reusing purpose. Reusing an existing platform or an already tested Intellectual Property (IP) block in a new design will greatly increase the chances of first pass success and therefore shrink the design cycle. The circuit platforms compose of different topology choices and also the same topology with different set of design parameters.

In this approach, a top-down process of mapping the receiver system specifica-

Figure 2.4. Bridge the gap between two design layers.

tions to an architecture and finally to circuit implementations is met by a bottom-up process where the building blocks are characterized in terms of their performance, size and cost. Behavioral models will be introduced as an intermediate level of abstraction to enable efficient performance evaluations (Fig. 2.4). They are parameterized executable models. The model parameters are configured by the lower-level performance obtained from the platform characterization. For example, the performance can be the non-idealities of analog/RF circuits. Lower level implementation details are abstracted away. In this way, the behavioral models are constrained by available implementation architectures. Through the behavioral models, we can make an accurate estimation of the non-idealities and implementation costs (e.g. power consumption, area) on a higher design level. During the top-down phase, design optimization is efficiently performed using behavioral models at system level, allowing effective exploration of the design space.

This proposed receiver design approach automates the design-space exploration procedure at a high abstraction level, which allows to explore a large design space at the beginning of the design cycle. As a result, system engineers can get "the big picture" of what performance levels can be expected when making different choices along the design process.

In the next chapters, I will explore two application scenarios to demonstrate this proposed design approach. One is a low power front-end design for Ultra Wideband (UWB) receiver; the other is an ultra low power mixed-signal baseband design for wireless sensor networks.

## 2.3.3 Application Scenarios

#### 1. Low Power Front-end Design for an Ultra Wideband Receiver

As one of the most exciting evolutions of wireless communications, multimedia can be transmitted over a wireless LAN. The wireless connectivity offers more flexibility and new potentials in consumer applications. Growing demands for wireless multimedia transmission are boosting the data rate requirements of wireless communications. Ultra-WideBand (UWB) wireless technology is considered to be a compelling solution to short-range communications (1-10m), which is characterized by high data rates (e.g. hundreds of megabits per second), low power consumption, high robustness to multi-path fading, and low transmission power that allows it to coexist with other wireless technologies.

There are two competing UWB radios under consideration: the direct-sequence impulse radio and the Multi-Band Orthogonal Frequency Division Multiplexing (MB-OFDM) radio. The UWB spectrum released by the FCC spans the range from 3.1GHz to 10.6GHz, with very low power spectral density. For the MB-OFDM UWB radio, as specified by the Multi-Band OFDM Alliance (MBOA) standard [12], the spectrum is divided into five band groups, each composed of 528MHz spaced frequency-hopping bands carrying OFDM signals (Fig. 2.5). Within each band, each carrier is modulated

Figure 2.5. MB-OFDM UWB frequency allocation.

by QPSK. In our design, we focus on the MB-OFDM UWB systems operating in the first band group (Mode I), which spans the frequency range from 3.1GHz to 4.8GHz.

Our goal is to design a low-power UWB receiver that should be sufficiently robust against nearby interference. Typically, UWB receivers operating in band group 1 will suffer from potential interference from standards such as 802.11a/b WLAN, WiMax, Bluetooth, and so on. The interference could have significant impacts given the anticipated weak power levels of the UWB signal (maximum power spectral density is -41.3dBm/MHz). A strong narrow band interferer could be as much as 60dB above the UWB signal at the receiver antenna. This situation imposes challenging design requirements on the desensitization, linearity and dynamic range of a UWB receiver.

Design challenges also come from the need for input impedance matching and gain flatness over the broad band (3.1-4.8GHz), the design of a broadband transmit/receive (T/R) switch, and so on. Traditionally, a complex analog/RF design such as above is carried out by a trial-and-error approach and is rarely optimized. We believe that a systematic design space exploration is essential to obtain an optimal system and to improve the state of the art of wireless design technology.

As a short summary, the design of an MB-OFDM ultra-wideband receiver is challenging when we target power consumption minimization while providing enough robustness against the nearby wireless interference. In the remaining part of this thesis, I will present an optimized receiver front-end design starting from system level analysis down to circuit implementation, using the PBD design methodology. In chapter 3, we investigate the impacts of interference at system level and propose an approach to estimate the inter-modulation products. In chapter 4, we introduce the behavioral models developed at architectural level, which will be used to perform design space exploration based on the PBD methodology. On the circuit level, low power front-end circuits are designed and their performance profiles are generated. In chapter 5, a top-down process of mapping the system-level specifications to circuit-level platforms is conducted by optimization. The optimal design will be reported.

#### 2. Ultra-Low Power Baseband for Wireless Sensor Networks

Wireless sensor network (WSN) has attracted more and more attentions and is very promising to become a growing market in the near future. It opens up many opportunities for ubiquitous sensing and ambient intelligence, such as improved human health monitoring, fire detection in forests, traffic control, environmental observation, etc. Typically, the WSN communication features low data rates with low duty cycles.

An important design requirement of the sensor nodes is the ultra-low power consumption. In almost all applications, replacing batteries at regular instants in battery-powered nodes is inconvenient if not impossible. Some sensor nodes need to scavenge the energy from the environment. For these nodes, it is critical to pursue design solutions that reduce the power consumption as much as possible (e.g. sub-mW level). Designing these wireless nodes in nanometer CMOS technologies with decreasing supply voltages and worsening signal integrity conditions are key challenges that designers face.

Recent progress in ultra-low power transceivers for sensor networks has reduced the receiver's power consumption to the level below a milliwatt and the overall transceiver implementation volume to below 1mm<sup>3</sup> [35, 36]. This new radio utilizes a combination of micro-electromechanical (MEMS) devices and standard CMOS processes. The radio baseband (demodulation and synchronization) circuitry must be extremely small and exhibit very low power dissipation. This leads to fundamentally different baseband design approaches than the ones used in standard radios. To eliminate the need for replacing or recharging system batteries, all of the energy dissipated by the electronics must be scavenged from the environment [41][44]. This limits the average power dissipation of the sensor node to around  $100\mu$ W. One of the most challenging aspects of this vision is integrating a low power RF communication link capable of connecting the autonomous nodes into a large, ad-hoc network. The baseband design in this thesis focuses on the demodulation synchronization hardware of such a system.

We believe that the constraints introduced above can only be met within a reasonable design time if a system level design methodology is used. In the following chapters of this thesis, I will explain how we leverage the platform based approach to design the baseband section for the low power Picoradio transceivers. Starting from the RF interface, our design process begins with a system level phase focusing on the functional design. The PBD approach is used to explore two alternative solutions: a predominantly digital one and a predominantly analog one. To validate the functional aspect of the design and explore the different analog vs. digital partitions, prototype implementations based on configurable platforms including an FPGA and a Field Programmable Analog Array (FPAA) are derived using the PBD approach. Finally, after evaluating performances and extrapolating results to a custom design, we map the system level description to an ultra-low power silicon implementation in a 0.13µm CMOS process.

# Chapter 3

# System Level Design

## 3.1 System Exploration

An effective system exploration is not only important to reduce the time-to-market. It can also realize more significant overall power savings than the power reduction that circuit design techniques can achieve in each individual block. There are numerous exploration concerns, whose weights vary in different wireless systems. During the system level exploration, we first need to identify the critical concerns that will generate important impacts on system performance and overall power consumption in a specific system context. In this section, I mainly discuss two typical concerns in wireless receiver systems.

## 3.1.1 Functionality Partitioning: Digital vs. Analog

Wireless receiver systems compose of RF front-end and low frequency back-end. For the low frequency part, the function partitioning can vary substantially, that consequently requires quite different type of corresponding architectures. The entire system design will benefit from a proper system-level partitioning, that includes parti-

tioning of the function implementation between the hardware and software domains, also includes partitioning of the signal processing between the digital and analog domains. This is one of the main concerns in the WSN baseband design.

The mostly-digital approach is very typical in most digital wireless receivers, where minimal functionalities are performed in the analog domain. After the RF front-end down-conversion, the incoming signal is digitalized by ADC and all further signal processing is conducted in digital domain. This brings about a main benefit, i.e. the digital signal processing algorithms usually offer higher flexibility and better integrity than the analog processing. A typical design challenge of a mostly-digital solution is to design an ADC with stringent performance requirements. Without pre-processing the received signal in analog domain, the ADC is required to provide a high resolution to accommodate for the fact that the down-converted signal at the ADC input has a very high dynamic range. The increased ADC resolution requirements will be translated to a considerable increase of overall power dissipation of the receiver. That is the main reason motivating the designers to consider the hybrid or mostly-analog solutions.

A different signal partitioning is that more signal processing jobs are performed in the analog domain, that is called hybrid approach (comparable amounts of digital and analog) or mostly-analog approach (analog is dominant). Though the mostly-analog approach is not widely employed, there are some successful design examples. A typical usage is to insert some analog blocks between the RF front-end and the ADC so that the down-converted signal is pre-processed before the digitalization conversion. Even further, part of the baseband tasks can be moved to the analog domain. The big advantage is the reduced performance requirements on ADC design, that consequently leads to a significant power savings. One of the disadvantages that restricts its wide adoption is that the baseband functionalities (e.g. AGC, channel equalization, etc.) and the algorithms (e.g. maximum likelihood algorithm) require complicated circuitry if implement in analog domain. The operations of most digital

Figure 3.1. Ultra-low power receiver for wireless sensor networks (WSNs)

modulation schemes can be performed elegantly in digital domain, while same tasks become very difficult if map to analog domain. Moreover, due to the existance of various noise and non-idealities in analog circuits, the precision or even the correctness of the advanced signal processing algorithms can be corrupted. Therefore, a hybrid or mostly-analog approach requires a careful evaluation of the system, including the modulation scheme, the RF front-end, the baseband signal processing requirements, etc. In order to take advantage of the power savings in hybrid or mostly-analog solutions, the algorithms in mostly-digital solution need to be modified or a different algorithm need to be developed in order to be well mapped to the analog architectures.

The Picoradio design targets for an extremely low power system for use in wire-less sensor network applications. This system operates at a maximum data rate of 50kbit/s, and a non-coherent modulation scheme is used. Simplification is considered as an effective strategy to achieve the extremely low power consumption. Generally, in order to correctly demodulate and detect the incoming signal, a digital communications receiver needs to perform a set of signal processing tasks, such as symbol synchronization, carrier phase/frequency recovery, automatic gain control (AGC), channel equalization, etc. Among the tasks, symbol synchronization is to deal with the timing offset that is caused by the mismatches between the transmitter and receiver oscillators and by the unknown time of flight between the transmitter and receiver.

As a part of the simplification strategy, an MEMS-based RF transceiver is designed to operate at 2GHz [36]. The high-Q MEMS channel-select filter greatly suppresses the out-of-band interference. The radio employs a self-mixing signal down conversion using an envelope detector. Due to the self-mixing process, frequency and phase information is removed from the incoming signal. Considering this MEMS-based architecture, a simple ON/OFF keying (OOK) modulation scheme is chosen. It allows simple detection on the receive side and efficient modulation on the transmit side, and has been proved to be very energy efficient for wireless sensor network systems. Since the startup time of the transmitter is fast, the entire transmitter is cycled on/off between transmitted symbols. Thus, the entire transmitter is powered down while transmitting a zero, effectively reducing the energy consumption of the transmitter by a factor of two.

An alternating 1010 training sequence header is used for synchronization. For simplification purpose, the main task of the baseband is just to perform the symbol synchronization. The synchronization requirements and the baseband complexity have been simplified by the radio RF front-end and the modulation scheme. For the OOK modulation, only timing and amplitude are required to be detected during synchronization. No AGC is involved, and equalization is also avoided. Such a baseband system is a suitable case to explore different signal partitioning, because the simplified synchronization requirements are able to be implemented in digital domain and in analog domain as well.

In order to achieve a synchronization system with short header length and extremely low power consumption, two different signal partitions are investigated. In the digital scheme, the signal from the envelope detector goes directly into an the analog-to-digital convertor(ADC). All the synchronization tasks are performed in the digital domain. The digital scheme with an 8-bit ADC is elaborated in [8]. Considering that ADC is a dominant power consumer, another scheme is designed to avoid

Figure 3.2. Block diagram of Early-Late Gate synchronizer

the ADC employment. In this scheme, the synchronization functionality is mainly implemented in analog circuits, with digital control. This thesis will be focused on the mostly-analog scheme.

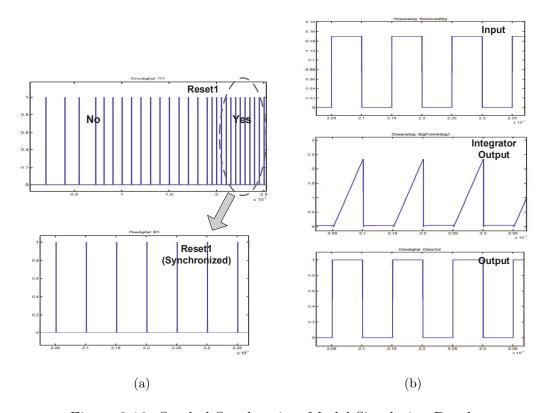

An Early-Late Gate synchronization scheme is employed to demodulate the OOK modulation. The block diagram is shown in Fig. 3.2. The demodulator works by correlating the incoming signal with two copies of an internally generated symbol, one delayed by  $\delta$  and one anticipated by  $\delta$ . If the internal symbol clock is correctly synchronized, each integrator will integrate half of the symbol, so that no error signal is generated. If the symbol clock is leading (lagging), negative feedback is applied through combining the integration paths until synchronization is achieved [40].

This synchronization algorithm allows different implementations, ranging from a completely analog one (e.g. a principle implementation of the block diagram in Fig. 3.2) to a completely digital one (after the incoming signal has been sampled and converted). We explored the different possibilities of partitioning the design between analog and digital, evaluating performances as accurately as possible before final implementation on silicon. To achieve this, we modeled the algorithm at a high level of abstraction in Matlab/Simulink, and also in Metropolis (will be discussed in section 3.2.3). We excluded the all-analog solution from exploration because we needed

some flexibility in the control algorithm to adjust for variable bit rates. A mostly digital solution with digitization occurring immediately after down conversion, and a hybrid solution (predominantly analog processing) were investigated where signal processing is performed in the analog domain using a 1 bit converter (comparator) at the end of the sampler blocks to feed a digital control algorithm. The detailed investigation will be introduced in section 4.1.2.

### 3.1.2 System Budget: Robustness vs. Low Power

To design a low power receiver, a critical task is trading off the system requirements, including nonlinearities, Noise Figure (NF), implementation loss, gain, etc. If we target to achieve low power consumption and simultaneously provide enough robustness against the interference, we need to perform a careful system budget. In order for the architect to make the appropriate trade-offs, the various estimations in the system budget must be accurate enough. Therefore, minimizing power consumption of a robust design implies the need of thorough investigation and accurate estimation of the interference influences on the receiver's performance. This is the design scenario for our UWB receiver.

To achieve co-existence with other wireless technologies, UWB receivers should exhibit robust behavior against nearby interference. Typically, UWB receivers operating in band group 1 will suffer from the potential interference from standards such as 802.11a/b WLAN, WiMax, Bluetooth, and GSM1900 as shown in Fig. 3.3. The interference could have significant impacts given the anticipated weak power levels of the UWB signal (maximum power spectral density is -41.3dBm/MHz). A strong narrow band interferer could be as much as 60dB above the UWB signal at the receiver antenna. This situation imposes challenging design requirements on the linearity performance and the dynamic range of a UWB receiver.

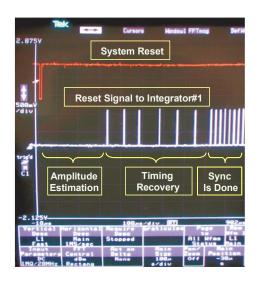

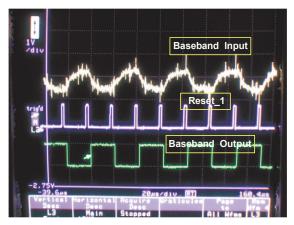

Figure 3.3. Interference scenario around UWB band group 1.