### Novel Processes and Structures for Low Temperature Fabrication of Integrated Circuit Devices

Joanna Lai

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2008-173 http://www.eecs.berkeley.edu/Pubs/TechRpts/2008/EECS-2008-173.html

December 19, 2008

Copyright 2008, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Novel Processes and Structures for Low Temperature Fabrication of Integrated Circuit Devices

by

Joanna T Lai

B.S. (Cornell University) 2002

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

### GRADUATE DIVISION

of the

### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Nathan Cheung Professor Costas Grigoropoulos

Fall 2008

The dissertation of Joanna T Lai is approved.

Chair

Date

Date

Date

University of California, Berkeley Fall 2008 Novel Processes and Structures for Low Temperature Fabrication of Integrated Circuit Devices

Copyright  $\bigodot$  2008

by

Joanna T Lai

### Abstract

### Novel Processes and Structures for Low Temperature Fabrication of Integrated Circuit Devices

by

Joanna T Lai

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Low temperature fabrication of integrated circuit (IC) devices is important for large-area electronics and 3-D integration with CMOS electronics. This work addresses novel processes and transistor structures for these applications.

Polycrystalline silicon thin film transistors (poly-Si TFTs) are the highest performing devices for flat panel displays such as active matrix liquid crystal displays. Though the poly-Si TFT market share in the flat panel display industry is growing, realizing systemon-panel (SOP) products with all electronic circuitry directly fabricated on the display substrate requires improved device uniformity and reliability.

Two new processes are investigated to improve the performance, uniformity and reliability of poly-Si TFTs. The first is an ultra-low-temperature ultraviolet (UV) oxidation process with a maximum substrate temperature of 150°C developed for fabrication of poly-Si TFTs on flexible substrates. The UV oxide interfacial layer with a gate oxide deposited by PECVD shows excellent gate oxide characteristics for poly-Si TFT technology. Next, a defect passivation technique by selenium ion implantation into the TFT channel is shown to successfully passivate defects and improve TFT reliability under hot carrier bias conditions. An alternative TFT design is examined, the accumulation-mode TFT. The accumulation-mode TFT employs a moderately-doped channel ( $\sim 10^{18} \text{cm}^{-3}$ ) of the same dopant type as the source and drain regions. Using a 2-dimensional device simulator, it is shown that this device can achieve good electrical characteristics, with thin gate oxide and silicon channel film thickness. Simulations for a single grain boundary in the TFT channel show that the accumulation-mode design is less sensitive to the grain boundary location as compared to a conventional enhancement-mode design.

A novel device, the poly-Si tunneling field effect transistor (TFET), is fabricated with a maximum process temperature of 600°C. The short channel TFETs exhibit enhanced on-state current mostly due to carrier multiplication by impact ionization, at a trade-off of high leakage currents. An optimal TFET device design is proposed to decrease the off-state current levels.

Several low-thermal-budget materials are investigated as candidate structural MEMS materials for 3-D integration with CMOS circuitry. The mechanical properties of four metals (Al, Ti, TiN and Ni) are extracted. Of the four, only Al exhibited a low average tensile stress suitable for MEMS applications, but it had large strain gradient. Poly-Si formed by aluminum-induced-crystallization (AIC) at a maximum temperature of  $350^{\circ}$ C showed improved mechanical properties (low compressive stress and moderate strain gradient). An additional excimer laser anneal (ELA) at low laser fluence of  $100 \frac{\text{mJ}}{\text{cm}^2}$  yields superior mechanical properties so that AIC poly-Si is suitable for integrated MEMS applications such as inertial sensors and hybrid relay/CMOS circuits.

Professor Tsu-Jae King Liu Dissertation Committee Chair Dedicated to my Mommy and Daddy.

Your encouragement, faith and love have helped me through this journey.

## Contents

| $\mathbf{C}$ | onter | nts    |                                                                                                  | ii           |

|--------------|-------|--------|--------------------------------------------------------------------------------------------------|--------------|

| Li           | st of | Figur  | es                                                                                               | $\mathbf{v}$ |

| Li           | st of | Table  | s                                                                                                | x            |

| A            | ckno  | wledge | ements                                                                                           | xi           |

| 1            | Intr  | oduct  | ion                                                                                              | 1            |

|              | 1.1   |        | Chermal-Budget Device Fabrication for Large-Area Electronics and 3-D ation with CMOS Electronics | 1            |

|              | 1.2   | Active | e Matrix Liquid Crystal Display Technology                                                       | 2            |

|              |       | 1.2.1  | Thin Film Transistor Technologies                                                                | 4            |

|              |       | 1.2.2  | Challenges for Poly-Si Thin Film Transistor Technology $\ . \ . \ . \ .$                         | 6            |

|              | 1.3   | Three  | -Dimensional Integrated Circuit Technology                                                       | 8            |

|              |       | 1.3.1  | Low-Thermal-Budget Structural Materials for MEMS $\ . \ . \ . \ .$ .                             | 9            |

|              | 1.4   | Thesis | Organization                                                                                     | 10           |

|              | 1.5   | Refere | ences                                                                                            | 11           |

| <b>2</b>     | Ult   | ra-Low | 7-Temperature Gate Oxide Interface Formation                                                     | 16           |

|              | 2.1   | Introd | $\operatorname{luction}$                                                                         | 16           |

|              | 2.2   | Oxide  | Growth by UV-Enhanced Oxidation                                                                  | 18           |

|              | 2.3   | UV O   | xidation Process Optimization                                                                    | 19           |

|              |       | 2.3.1  | Interface Characterization by Surface Charge Analysis                                            | 19           |

|              |       | 2.3.2  | Pressure and Temperature Dependence of Interface Properties $\ . \ .$                            | 20           |

|              | 2.4   | Metal  | -Oxide-Semiconductor Capacitor Study                                                             | 21           |

|          |     | 2.4.1 Ultra-Low-Temperature Gate Oxide by PECVD and PVD Processes 2            | 2        |

|----------|-----|--------------------------------------------------------------------------------|----------|

|          |     | 2.4.2 MOS Capacitor Fabrication                                                | 4        |

|          |     | 2.4.3 Experimental Results                                                     | 5        |

|          | 2.5 | Summary                                                                        | 8        |

|          | 2.6 | References                                                                     | 8        |

| 3        |     | ect Passivation by Selenium Ion Implantation for Poly-Si Thin Film<br>nsistors | 3        |

|          | 3.1 | Introduction                                                                   | 3        |

|          | 3.2 | Process Flow                                                                   | 5        |

|          | 3.3 | Effects of Selenium on TFT Performance                                         | 8        |

|          |     | 3.3.1 Optimal ELA Process Condition                                            | 8        |

|          |     | 3.3.2 Impact of Selenium Dose                                                  | 0        |

|          | 3.4 | Comparison of Hydrogen and Selenium Passivation Techniques                     | 2        |

|          |     | 3.4.1 Effects of Hydrogenation on Control and Se-passivated TFTs 4             | 2        |

|          |     | 3.4.2 Effect of Passivation Technique on Short Channel Effects 4               | 4        |

|          | 3.5 | TFT Hot Carrier Reliability for Different Passivation Techniques 4             | 6        |

|          | 3.6 | Summary 4                                                                      | 7        |

|          | 3.7 | References                                                                     | 9        |

| 4        | Acc | umulation-Mode Poly-Si Thin Film Transistors 5                                 | <b>2</b> |

|          | 4.1 | Introduction                                                                   | 2        |

|          | 4.2 | Accumulation-Mode TFT Operation                                                | 4        |

|          | 4.3 | Simulation-based Design Study                                                  | 5        |

|          |     | 4.3.1 Optimization of TFT Dimensions                                           | 6        |

|          |     | 4.3.2 Optimization of Body Dopant Concentration                                | 8        |

|          |     | 4.3.3 Effect of Grain Boundaries on Accumulation-Mode TFTs 6                   | 1        |

|          | 4.4 | Proposed Vertical Accumulation-Mode TFT Fabrication Flow 6                     | 5        |

|          | 4.5 | Summary                                                                        | 8        |

|          | 4.6 | References                                                                     | 9        |

| <b>5</b> |     | verystalline Silicon Tunneling Field Effect Transistors for Enhanced           |          |

|          | On- | State Performance 7                                                            | 1        |

|          | 5.1 | Introduction                                                                   | 1        |

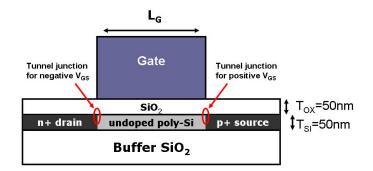

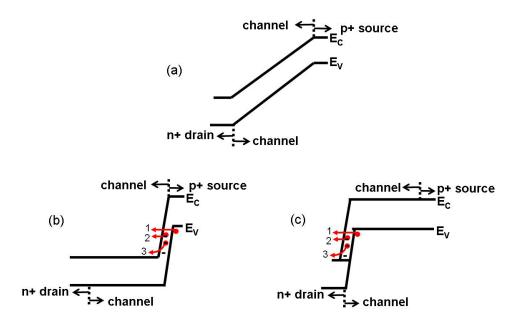

|   | 5.2 | TFET    | Operation                                                           | 72  |

|---|-----|---------|---------------------------------------------------------------------|-----|

|   | 5.3 | Poly-S  | Si TFET Study                                                       | 73  |

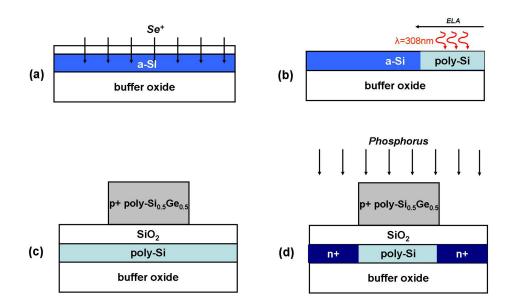

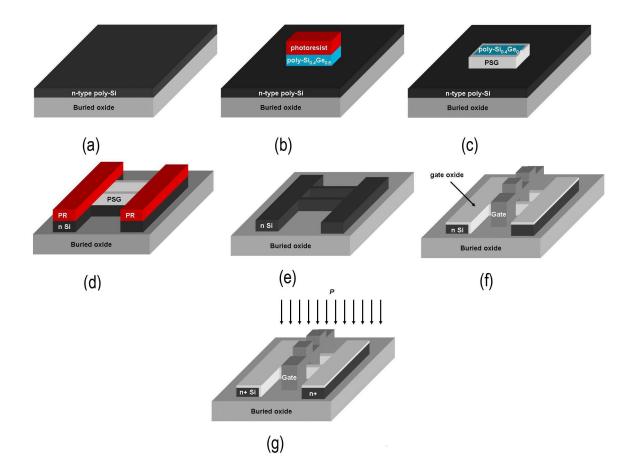

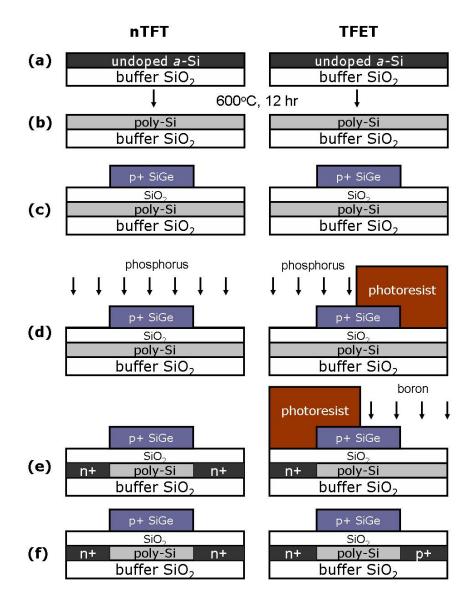

|   |     | 5.3.1   | Process Flow                                                        | 73  |

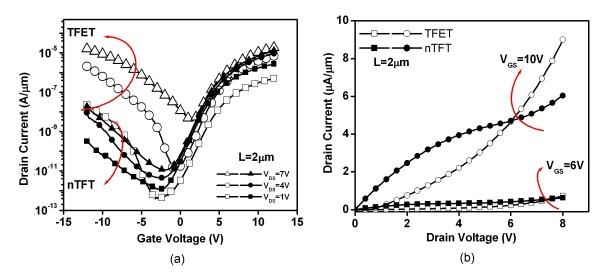

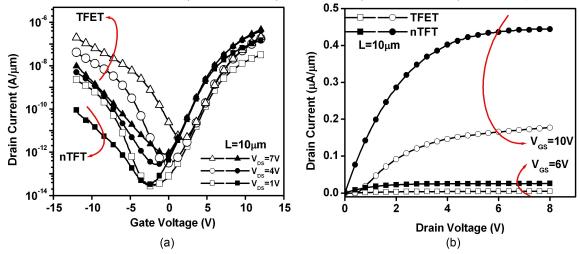

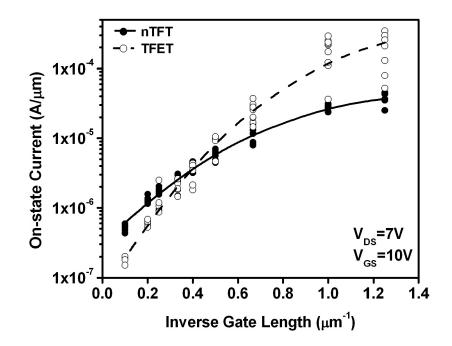

|   |     | 5.3.2   | Experimental Results                                                | 75  |

|   | 5.4 | Summ    | nary                                                                | 78  |

|   | 5.5 | Refere  | ences                                                               | 80  |

| 6 |     |         | mal-Budget Materials for Integrated Microelectromechanica           |     |

|   | v   | tems    |                                                                     | 83  |

|   | 6.1 |         |                                                                     | 83  |

|   | 6.2 |         | ction of Mechanical Properties                                      | 84  |

|   |     | 6.2.1   | Residual Stress Measurement by Wafer Curvature                      | 84  |

|   |     | 6.2.2   | Mechanical Properties Extraction using Analytical Model             | 85  |

|   | 6.3 |         | date Structural and Sacrificial Materials                           | 87  |

|   | 6.4 | -       | ered Metals for MEMS Structural Layer                               | 89  |

|   |     | 6.4.1   | Deposition Parameters for Sputtered Metal Films                     | 90  |

|   |     | 6.4.2   | Residual Stress of Sputtered Metal Films                            | 91  |

|   |     | 6.4.3   | Mechanical Properties of Aluminum Thin Films                        | 97  |

|   | 6.5 | Alumi   | inum-Induced Crystallization of Poly-Si for MEMS Structural Layer . | 99  |

|   |     | 6.5.1   | Formation of Polycrystalline Silicon Films                          | 99  |

|   |     | 6.5.2   | X-ray Diffraction Analysis of AIC Poly-Si Films                     | 100 |

|   |     | 6.5.3   | Mechanical Properties of AIC Poly-Si Films                          | 103 |

|   | 6.6 | Summ    | nary                                                                | 106 |

|   | 6.7 | Refere  | ences                                                               | 106 |

| 7 | Cor | nclusio | ns                                                                  | 111 |

|   | 7.1 | Summ    | hary of Contributions                                               | 111 |

|   |     | 7.1.1   | Contributions to Poly-Si Thin Film Transistor Technology            | 112 |

|   |     | 7.1.2   | Low-Thermal-Budget Materials for 3-D MEMS Integration $\ . \ . \ .$ | 113 |

|   | 7.2 | Sugge   | stions for Future Work                                              | 114 |

|   |     | 7.2.1   | Accumulation Mode Thin Film Transistors                             | 114 |

|   |     | 7.2.2   | Optimized Silicon Tunneling Field Effect Transistor Structure       | 114 |

|   | 7.3 | Refere  | ences                                                               | 116 |

# List of Figures

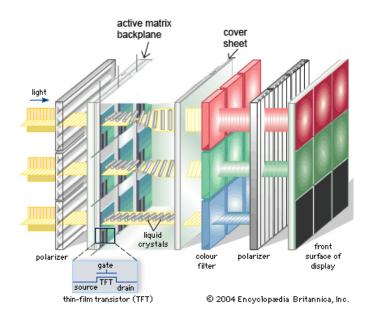

| 1.1 | Schematic cross section of a liquid crystal display [5]                                                                                                                                                   | 3        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

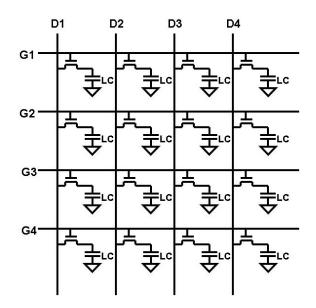

| 1.2 | Circuit schematic of an active matrix backplane for a liquid crystal display.                                                                                                                             | 4        |

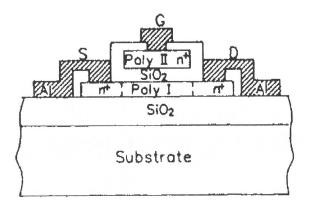

| 1.3 | Typical top gate, coplanar poly-Si TFT structure [12]                                                                                                                                                     | 5        |

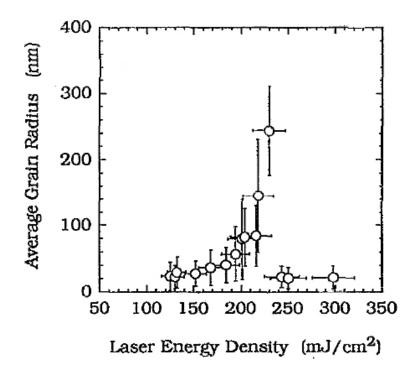

| 1.4 | Dependence of the average Si grain size as a function of pulsed excimer laser fluence, from [16]                                                                                                          | 7        |

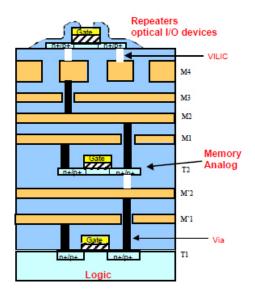

| 1.5 | Schematic cross-section of a 3-D integrated circuit with low-temperature transistors fabricated over CMOS electronics for memory applications, from                                                       |          |

|     | $[22]. \ldots \ldots$                                                              | 9        |

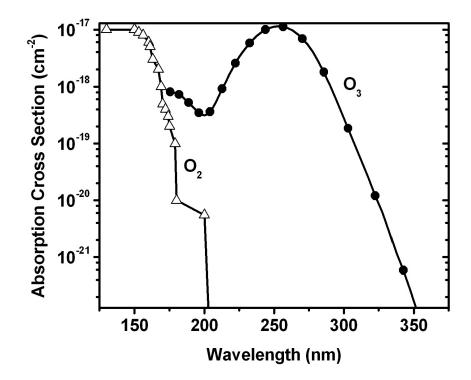

| 2.1 | Absorption of oxygen $(O_2)$ and ozone $(O_3)$ in silicon for various wavelengths of light, from [20] and [21]                                                                                            | 18       |

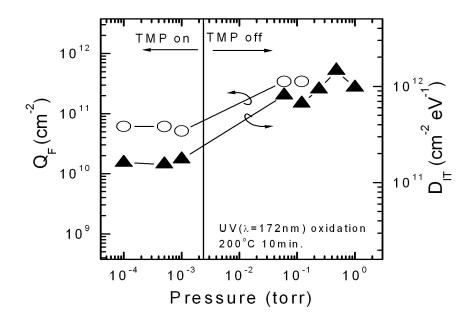

| 2.2 | Interface trap density and fixed oxide charge of UV-enhanced oxide films for various oxidation process pressures [24].                                                                                    | 20       |

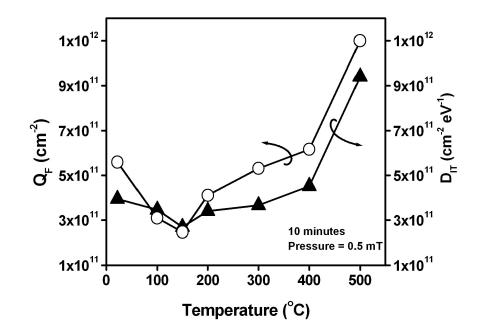

| 2.3 | Interface trap density and fixed oxide charge in UV-enhanced oxide films for various oxidation process temperatures.                                                                                      | 21       |

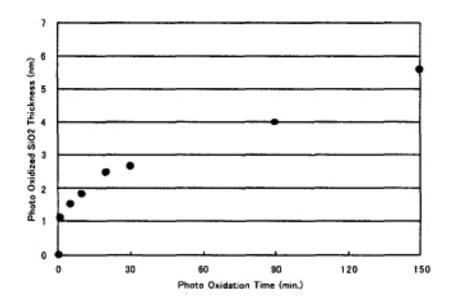

| 2.4 | UV-enhanced oxide growth follows the Deal-Grove model for oxidation at constant temperature and pressure, from [25]                                                                                       | 22       |

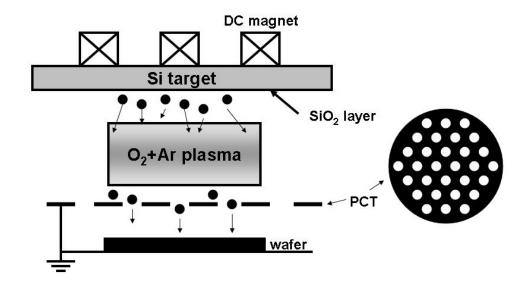

| 2.5 | Diagram of sputtering chamber with a PCT inserted between the Si target<br>and wafer. The PCT collects high-energy ions, preventing damage to the<br>wafer surface. This diagram is adapted from [26, 27] | 23       |

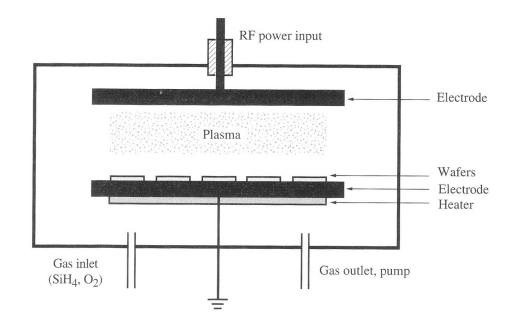

| 2.6 | Configuration of a typical parallel plate PECVD chamber [28].                                                                                                                                             | 20<br>24 |

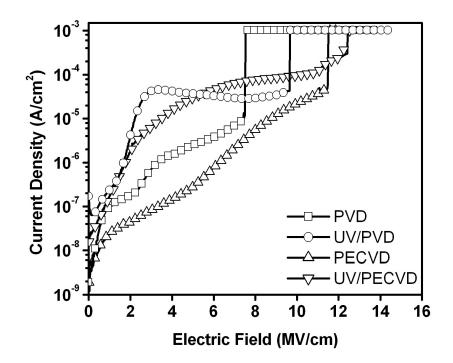

| 2.7 | Electric field breakdown versus current density for four gate dielectrics                                                                                                                                 | 26       |

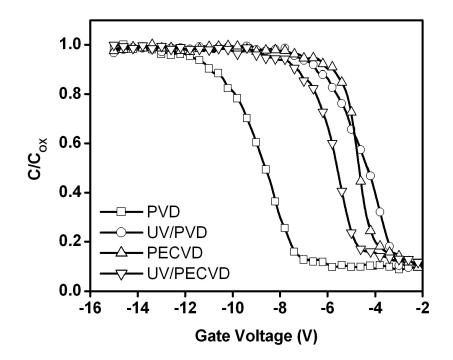

| 2.8 | Normalized gate capacitance versus gate voltage for four ultra-low-<br>temperature gate dielectric samples.                                                                                               | 27       |

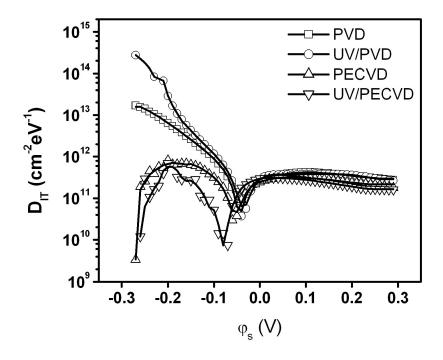

| 2.9 | Interface trap density versus Si surface potential for four oxide samples. The surface potential is measured relative to the flat band potential ( $\varphi_s=0$ at flat                                  |          |

|     | band)                                                                                                                                                                                                     | 27       |

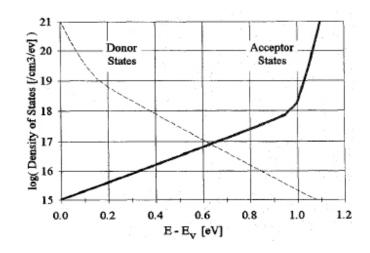

| 3.1  | Density of states in the Si bandgap due to presence of grain boundaries in a poly-Si film [1].                                                                                                                                                                                                                                                                                                                                                                          | 34 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Fabrication process flow for Se-implanted poly-Si TFTs                                                                                                                                                                                                                                                                                                                                                                                                                  | 36 |

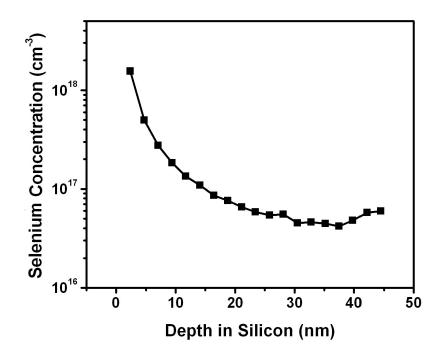

| 3.3  | Selenium concentration profile in a poly-Si film formed with a Selenium implant dose of $10^{13}$ cm <sup>-3</sup> and ELA laser fluence of $300 \frac{\text{mJ}}{\text{cm}^2}$                                                                                                                                                                                                                                                                                         | 37 |

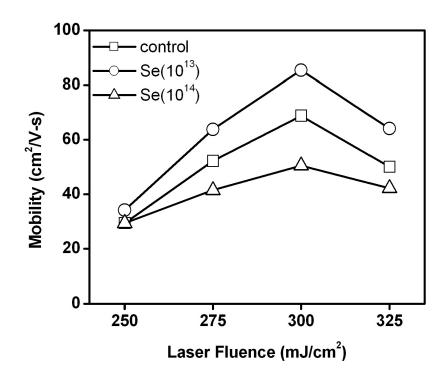

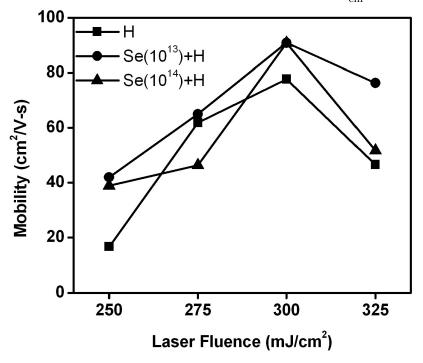

| 3.4  | Dependence of effective mobility ( $\mu_{\text{eff}}$ ) on excimer laser fluence for control and Selenium-passivated TFTs. Optimal laser fluence is evident at $300 \frac{\text{mJ}}{\text{cm}^2}$ .                                                                                                                                                                                                                                                                    | 39 |

| 3.5  | Dependence of effective mobility $(\mu_{\text{eff}})$ on excimer laser fluence for hydrogenated samples with and without Selenium passivation. Optimal laser fluence is evident at $300 \frac{\text{mJ}}{\text{cm}^2}$                                                                                                                                                                                                                                                  | 39 |

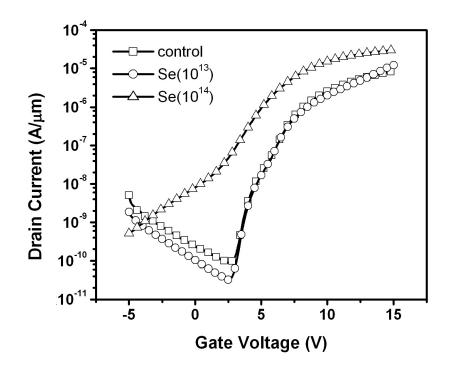

| 3.6  | Transfer characteristics of control and Se-passivated TFTs of W/L= $10\mu$ m/ $5\mu$ m, crystallized at laser fluence of 300 $\frac{mJ}{cm^2}$ . The drain current is normalized to the transistor width.                                                                                                                                                                                                                                                               | 41 |

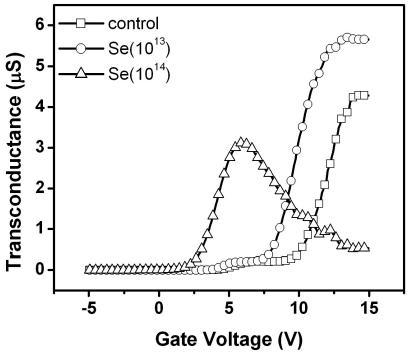

| 3.7  | Transconductance of the corresponding control and Se-passivated TFTs                                                                                                                                                                                                                                                                                                                                                                                                    | 41 |

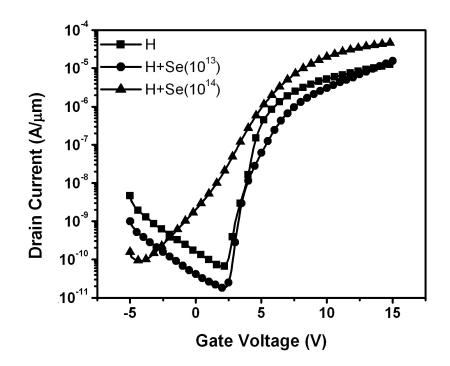

| 3.8  | Transfer characteristics of hydrogenated control and Se-passivated TFTs of $W/L=10\mu m/5\mu m$ , crystallized at laser fluence of 300 $\frac{mJ}{cm^2}$ . The drain current is normalized to the transistor width.                                                                                                                                                                                                                                                     | 43 |

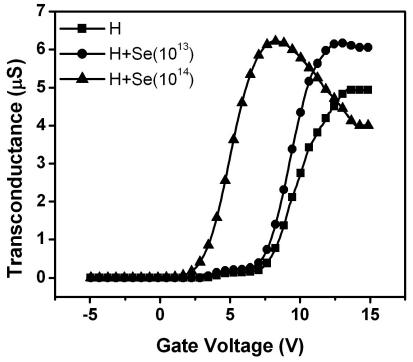

| 3.9  | Transconductance of the corresponding hydrogenated control and Sepassivated TFTs                                                                                                                                                                                                                                                                                                                                                                                        | 43 |

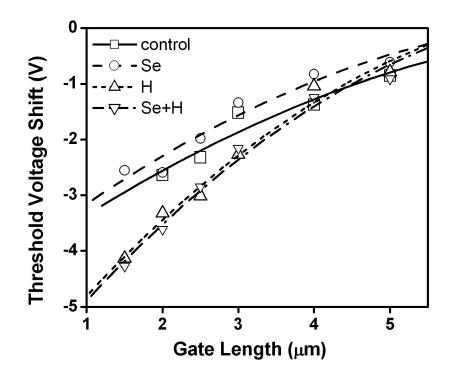

| 3.10 | Comparison of threshold voltage reduction vs. transistor gate length for various defect passivation techniques                                                                                                                                                                                                                                                                                                                                                          | 45 |

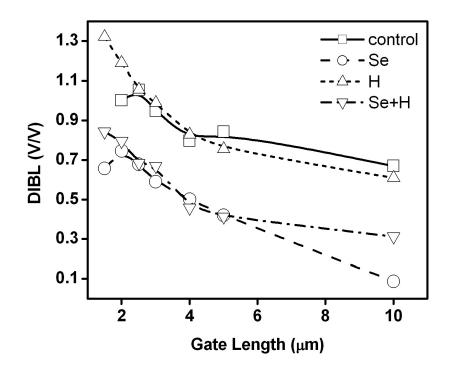

| 3.11 | Comparison of DIBL for different transistor gate lengths for each defect passivation technique.                                                                                                                                                                                                                                                                                                                                                                         | 46 |

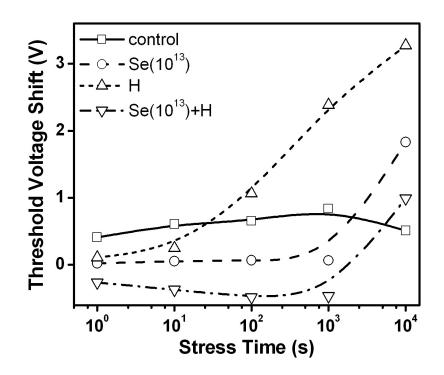

| 3.12 | $V_{\rm T}$ shift with DC bias stress duration in the forward mode                                                                                                                                                                                                                                                                                                                                                                                                      | 48 |

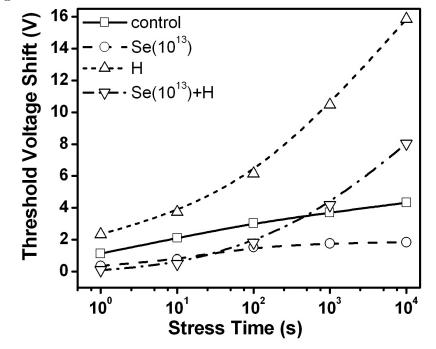

| 3.13 | $V_{\rm T}$ shift with DC bias stress duration in the reverse mode                                                                                                                                                                                                                                                                                                                                                                                                      | 48 |

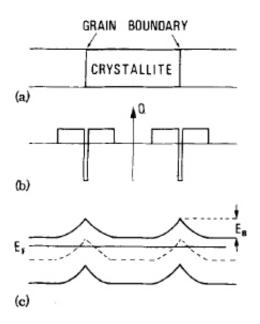

| 4.1  | A film with two grain boundaries is shown in (a). Large density of trapping sites $(N_T)$ at the grain boundaries are able to capture carriers, shown in the charge-density diagram in (b). Large energy barriers appear at the grain boundaries, shown in the energy band diagram in (c). The curvature of the energy bands are a result of the depletion regions. For undoped or lightly doped films, large and wide potential barriers are seen by the carriers [3]. | 53 |

| 4.2  | Potential barriers in a poly-Si film with doping greater than the critical concentration. All trap sites are filled leading to a reduction in barrier height and width [4]                                                                                                                                                                                                                                                                                              | 54 |

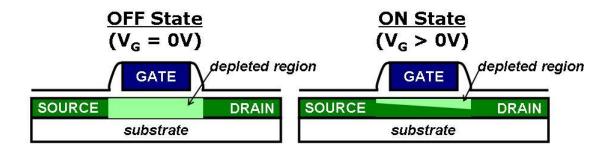

| 4.3  | Schematic cross-section of an n-channel accumulation-mode TFT operation<br>in the on- and off-states                                                                                                                                                                                                                                                                                                                                                                    | 55 |

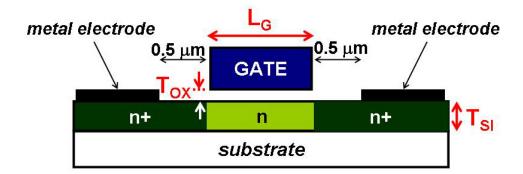

| 4.4  | Schematic cross-section of simulated accumulation-mode TFT                                                                                                                                                                                                                                                                                                                                                                                                              | 56 |

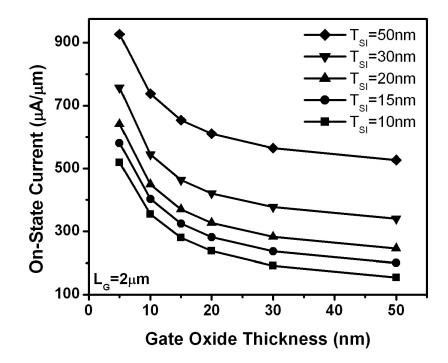

| 4.5  | Dependence of on-state current on gate oxide and silicon film thicknesses                                                                                                                                                                                                                                                                                                                                                                                               | 57 |

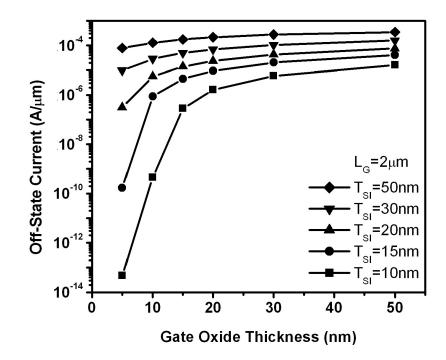

| 4.6  | Dependence of off-state current on gate oxide and silicon film thicknesses                                                                                                                                                                                                                                                                                                                                                         | 58 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

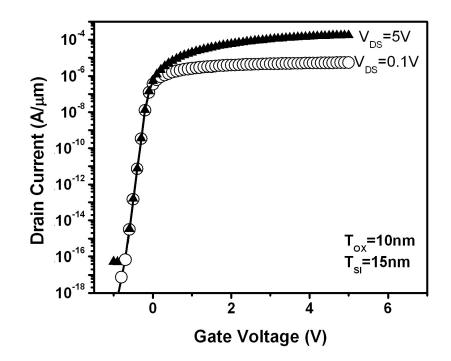

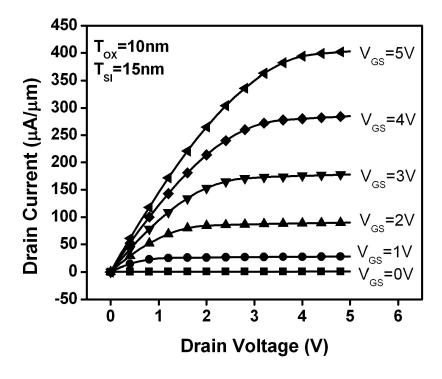

| 4.7  | Transfer characteristics for an optimized accumulation-mode MOSFET for drain bias of $V_D=0.1$ V and 5 V                                                                                                                                                                                                                                                                                                                           | 59 |

| 4.8  | Output characteristics for an optimized accumulation-mode MOSFET for gate bias of $V_G=0, 1, 2, 3, 4, 5 V. \ldots$                                                                                                                                                                                                                                                                                                                 | 59 |

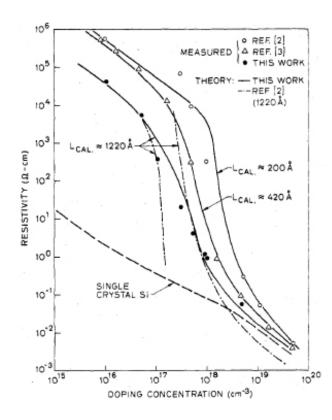

| 4.9  | Dependence of polycrystalline and single crystal Si resistivity on dopant concentration for various grain sizes [7].                                                                                                                                                                                                                                                                                                               | 60 |

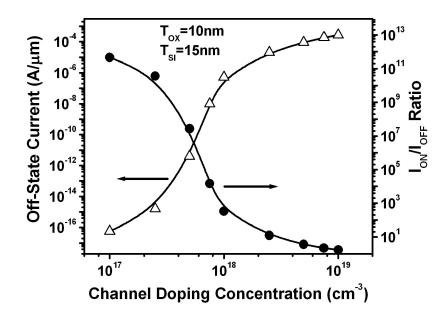

| 4.10 | Off-state current and $I_{ON}/I_{OFF}$ ratio of accumulation-mode MOSFETs of 2- $\mu$ m gate length with variable body doping.                                                                                                                                                                                                                                                                                                     | 61 |

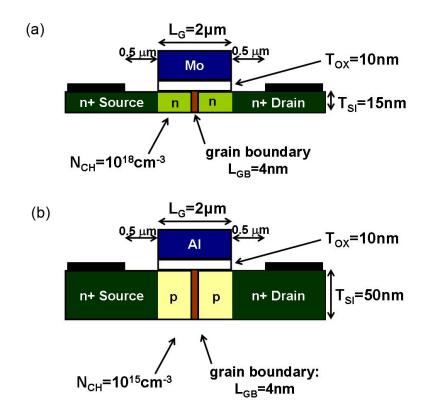

| 4.11 | Schematic cross-section of simulated (a) accumulation-mode TFT and (b) enhancement-mode TFT with a 4-nm long single grain boundary                                                                                                                                                                                                                                                                                                 | 62 |

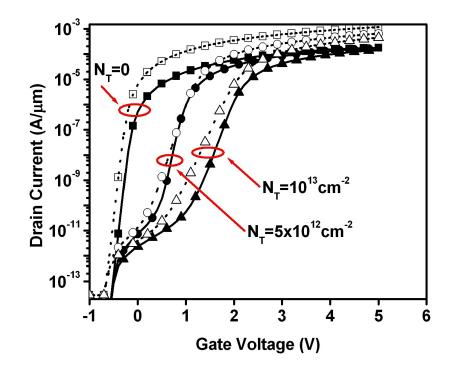

| 4.12 | Transfer characteristics of an accumulation-mode TFT and an enhancement-<br>mode TFT with a grain boundary midway between the source and drain<br>with drain bias of $V_D=5$ V for different areal trap densities. The transfer<br>characteristics for enhancement-mode TFTs are shown by dashed lines and<br>open symbols; the transfer characteristics for accumulation-mode TFTs are<br>shown by solid lines and closed symbols | 64 |

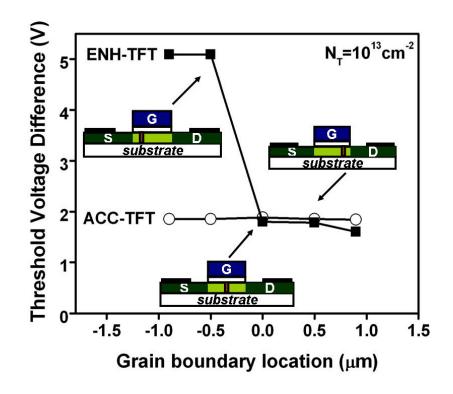

| 4.13 | Increase in threshold voltage due to a single grain boundary                                                                                                                                                                                                                                                                                                                                                                       | 65 |

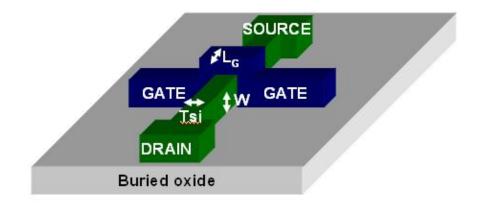

| 4.14 | Proposed structure for accumulation-mode TFT. The transistor gate length $(L_G)$ , width $(W)$ and thickness $(T_{SI})$ are labelled.                                                                                                                                                                                                                                                                                              | 66 |

| 4.15 | Process flow for vertical accumulation-mode TFT.                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

| 5.1  | Poly-Si tunneling field effect transistor structure                                                                                                                                                                                                                                                                                                                                                                                | 72 |

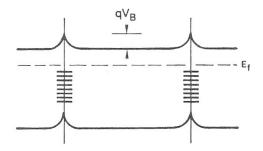

| 5.2  | Energy band diagrams in (a) off-state, (b) on-state at the source junction with a positive $V_{GS}$ bias and (c) on-state at the drain junction with a negative $V_{GS}$ bias.                                                                                                                                                                                                                                                     | 73 |

| 5.3  | Fabrication process for control n-type poly-Si TFT (left) and poly-Si TFET (right)                                                                                                                                                                                                                                                                                                                                                 | 74 |

| 5.4  | (a) Transfer characteristics for $V_{DS}=1$ , 4, 7 V and (b) output characteristics for $V_{GS}=6$ , 10 V for TFET (open symbols) and nTFT (closed symbols) of $L_G=2 \ \mu m. \ldots $                                                                                                                     | 76 |

| 5.5  | (a) Transfer characteristics for $V_{DS}=1$ , 4, 7 V and (b) output characteristics for $V_{GS}=6$ , 10 V for TFET (open symbols) and nTFT (closed symbols) of $L_{G}=10 \ \mu m$ .                                                                                                                                                                                                                                                | 76 |

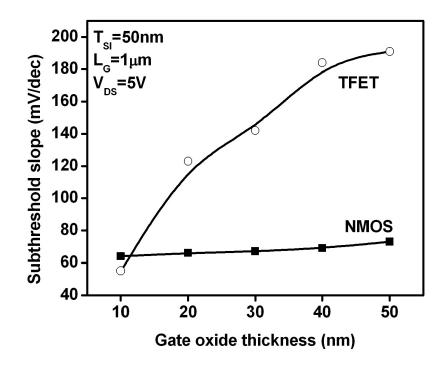

| 5.6  |                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78 |

| 5.7  | Simulation data showing subthreshold slope scaling as $T_{OX}$ decreases for a single crystalline TFET and n-channel MOSFET                                                                                                                                                                                                                                                                                                        | 79 |

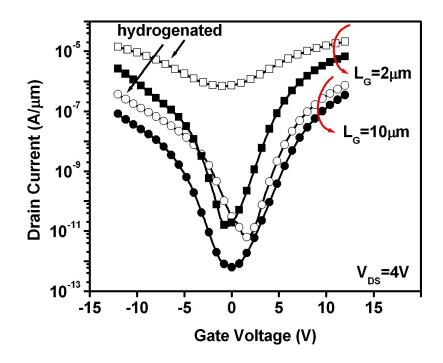

| 5.8  | Transfer characteristics for hydrogenated (open symbols) and non-<br>hydrogenated (closed symbols) TFET with gate length of $2-\mu m$ and $10-\mu m$<br>for $V_{DS}=4$ V                                                                                                                                                                                               | 79  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

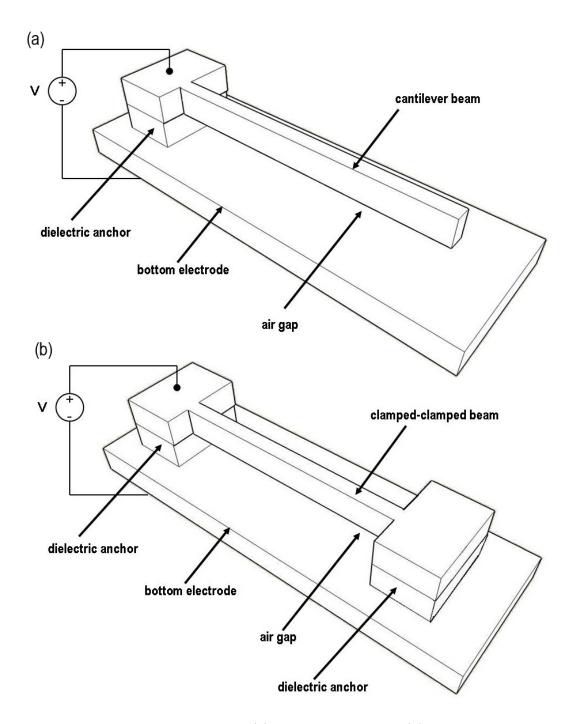

| 6.1  | Schematics of two-terminal (a) cantilever beam and (b) clamped-clamped beam relays                                                                                                                                                                                                                                                                                     | 86  |

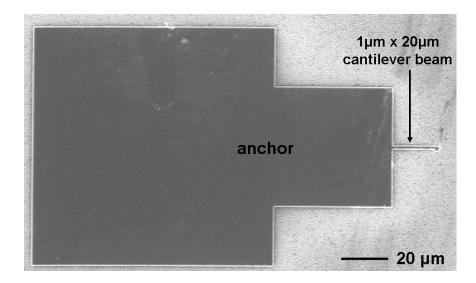

| 6.2  | Plan view scanning electron micrograph of an unreleased $1-\mu m \times 20-\mu m$ cantilever beam.                                                                                                                                                                                                                                                                     | 87  |

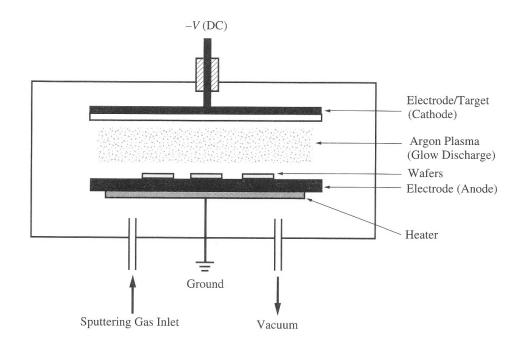

| 6.3  | Schematic of a parallel plate DC sputter deposition chamber [10]                                                                                                                                                                                                                                                                                                       | 90  |

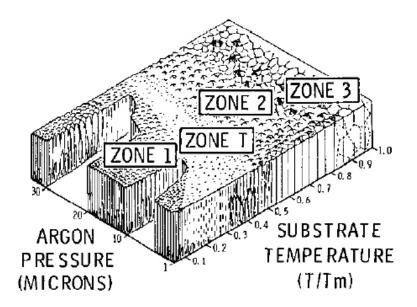

| 6.4  | The zone model for films deposited by sputtering. The film structures for sputtering pressure and temperatures are illustrated [15]                                                                                                                                                                                                                                    | 92  |

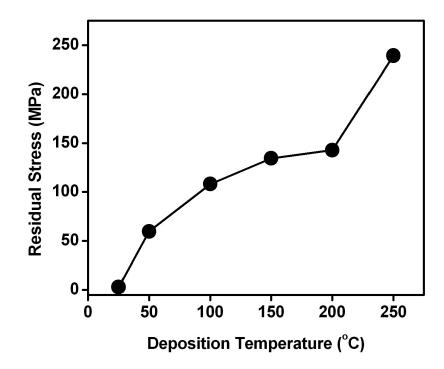

| 6.5  | Effect of deposition temperature on average residual stress for 500-nm thick Al films                                                                                                                                                                                                                                                                                  | 93  |

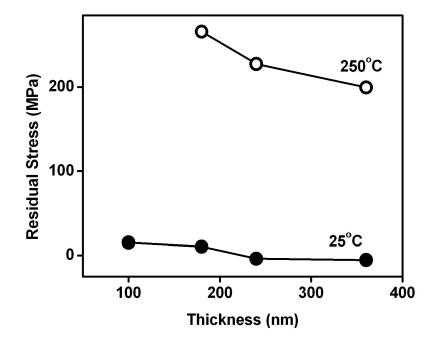

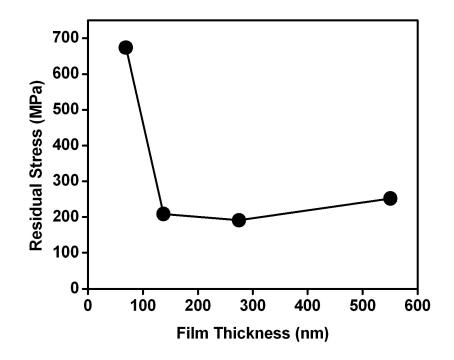

| 6.6  | Effect of Al film thickness on average residual stress for deposition temperatures of $25^{\circ}$ C (lower curve) and $250^{\circ}$ C (upper curve)                                                                                                                                                                                                                   | 93  |

| 6.7  | Effect of Ni film thickness on average residual stress                                                                                                                                                                                                                                                                                                                 | 94  |

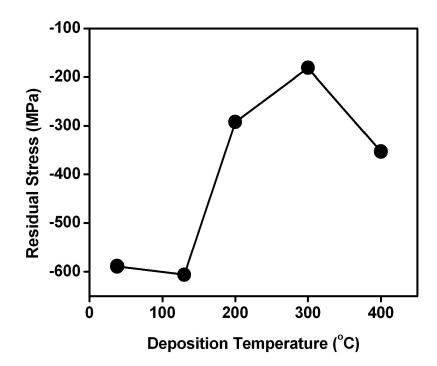

| 6.8  | Effect of deposition temperature on average residual stress of 250-nm thick TiN films [17].                                                                                                                                                                                                                                                                            | 95  |

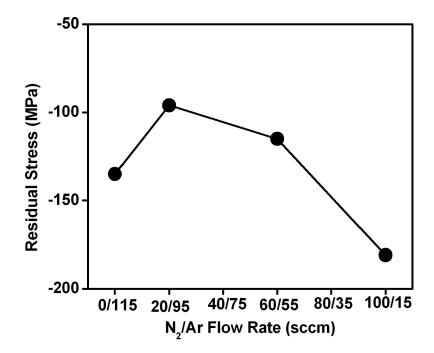

| 6.9  | Effect of $N_2$ to Ar gas flow ratios on average residual stress of 120-nm thick<br>Ti and TiN films [18]                                                                                                                                                                                                                                                              | 96  |

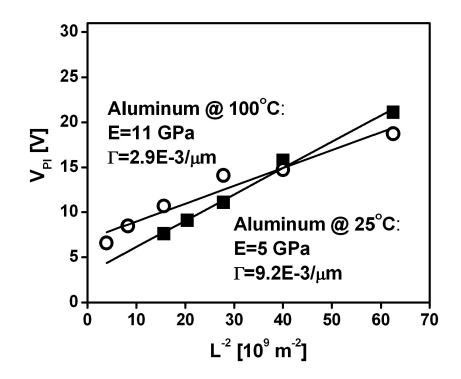

| 6.10 | Young's modulus (E) and strain gradient ( $\Gamma$ ) extraction from pull-in voltage measurements of Al cantilever beams of various lengths, deposited at 25°C (closed symbols) and 100°C (open symbols)                                                                                                                                                               | 98  |

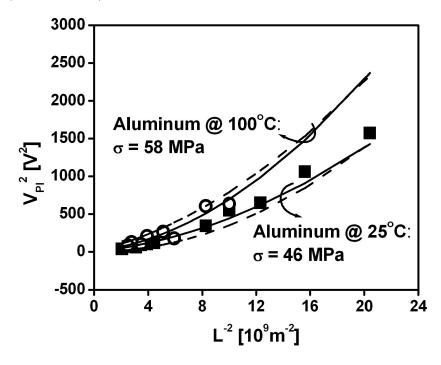

| 6.11 | Residual stress ( $\sigma$ ) extraction from pull-in voltage measurements of Al clamped-clamped beams deposited at 25°C (closed symbols) and 100°C (open symbols). The dashed curves represent expected values from wafer curvature measurements.                                                                                                                      | 98  |

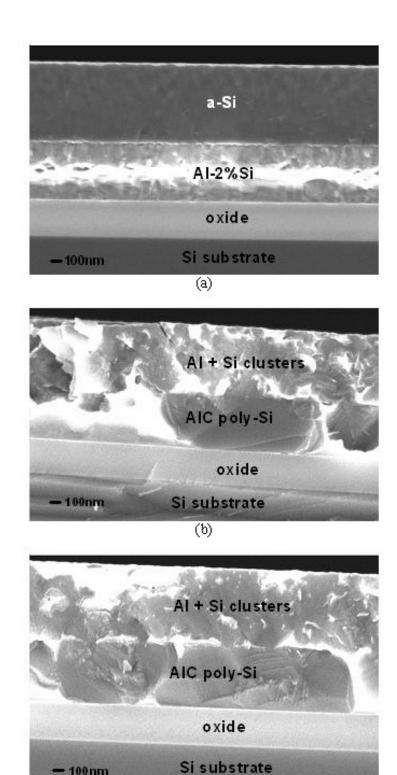

| 6.12 | Cross-sectional scanning electron micrographs of (a) as-deposited Al-2%Si/a-Si thin-film stack, (b) film stack after a $350^{\circ}$ C, 3 hr anneal, and (c) film stack after a $350^{\circ}$ C, 3 hr anneal + an ELA treatment.                                                                                                                                       | 101 |

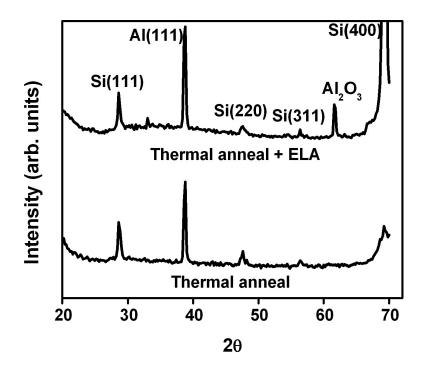

| 6.13 | XRD $2\theta$ scans of annealed thin film stacks prior to removal of the top Al layer.<br>The lower curve is for a sample which did not receive an ELA treatment; the<br>upper curve is for a sample which received an additional ELA treatment. The<br>Si(111) peak and the weaker Si(220) and Si(311) peaks indicate the successful<br>formation of a poly-Si layer. | 102 |

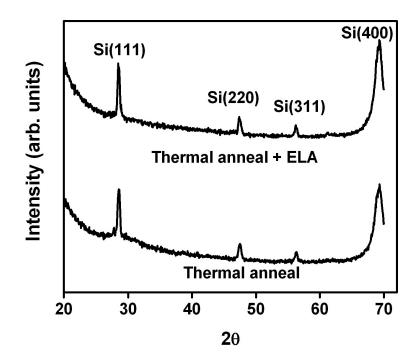

| 6.14 | XRD $2\theta$ scans of annealed thin film stacks after removal of the top Al layer.<br>The lower curve is for a sample which did not receive an ELA treatment; the<br>upper curve is for a sample which received an additional ELA treatment.                                                                                                                          | 103 |

|      |                                                                                                                                                                                                                                                                                                                                                                        |     |

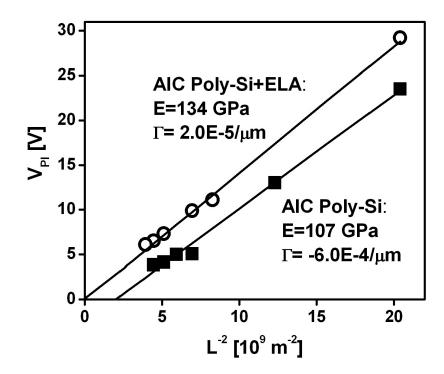

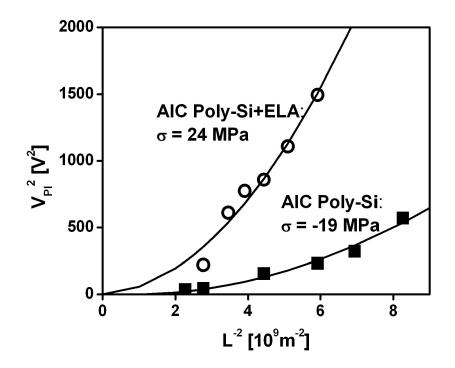

| 6.15 | Young's modulus (E) and strain gradient $(\Gamma)$ extraction from pull-in voltage measurements of AIC poly-Si cantilever beams of various lengths, with and without ELA treatment, shown by open and closed symbols, respectively. | 104 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.16 | Residual stress ( $\sigma$ ) extraction from pull-in voltage measurements of AIC poly-<br>Si clamped-clamped beams with and without ELA treatment, shown by open<br>and closed symbols, respectively.                               | 105 |

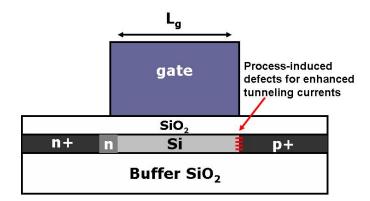

| 7.1  | Optimal TFET design with process-induced defects for enhanced tunneling currents.                                                                                                                                                   | 115 |

# List of Tables

| 1.1 | Substrate materials for TFTs [1, 2]                                                                                                                                                                                                                                                                                       | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Parameters extracted from HFCV and IV measurements for the four oxides.                                                                                                                                                                                                                                                   | 25 |

| 3.1 | Average and standard deviation for effective mobility (in $\frac{\text{cm}^2}{\text{V}\cdot\text{s}}$ ) for<br>unpassivated, Se-passivated and H-passivated TFTs. The standard deviation<br>is noted in parentheses on the second line                                                                                    | 38 |

| 3.2 | Average and standard deviation for various performance parameters for control and Selenium-passivated TFTs                                                                                                                                                                                                                | 40 |

| 3.3 | Average and standard deviation for various device parameters for<br>hydrogenated control and Selenium-doped TFTs                                                                                                                                                                                                          | 44 |

| 4.1 | Simulation parameters for n-type accumulation-mode TFT device                                                                                                                                                                                                                                                             | 56 |

| 4.2 | Simulation parameters for single grain boundary accumulation-mode and enhancement-mode TFT devices.                                                                                                                                                                                                                       | 63 |

| 5.1 | Average and standard deviation for various device parameters for control poly-Si nTFTs and TFETs for 2 $\mu$ m and 10 $\mu$ m gate lengths                                                                                                                                                                                | 77 |

| 6.1 | Etch rates of candidate structural and sacrificial materials for a chlorine-<br>based etch recipe. The etch is performed at a pressure of 250 mT, power of<br>250 W and gas flows for Cl <sub>2</sub> , N <sub>2</sub> , BCl <sub>3</sub> and CHCl <sub>3</sub> of 30 sccm, 50 sccm, 50<br>sccm and 20 sccm, respectively | 89 |

| 6.2 | Sputtering conditions for candidate structural metal films                                                                                                                                                                                                                                                                | 91 |

| 6.3 | Comparison of residual stress for 200-nm thick metal films                                                                                                                                                                                                                                                                | 96 |

#### Acknowledgements

I would like to thank Prof. Tsu-Jae King Liu, my graduate advisor. She has taken me in her group and taught me so much during my time in graduate school. Her time and effort in guiding and teaching me have been invaluable. She has been the best advisor and her support through the years has meant so much.

I would like to thank Prof. Nathan Cheung who sat on my prelim to qualifying exam to dissertation committee. You have given a lot of time and advice in my research. I would like to thank Prof. Costas Grigoropoulos for sitting on my dissertation committee and for helping me when I was in a bind. I would like to thank Prof. Ming Wu for letting me work with him on the silicon optical modulator project and for sitting on my qualifying exam committee. He has been a great advisor to me. I would also like to thank Prof. Oscar Dubon for sitting on my qualifying exam committee and giving me advice throughout the years.

I am grateful for the guidance from the device group alumni. Special thanks to Hideki Takeuchi for his technical discussions and wisdom. Thanks to Leland Chang and Kathy Boucart for all the times spent procrastinating and eating all those potato puffs. Special thanks to Hiu-Yung Wong, Sriram Balasubramanian, Marie-Ange Eyoum, Mohan Dunga, Chung-Hsun Lin and Vidya Varadarajan for welcoming me into the family. We had many great laughs in the office. I would also like to thank other device group alums, including Yang-Kyu Choi, Daewon Ha, Min She, Josei Chang, Brian Mattis, Kyoungsub Shin, Dan Good, Drew Carlson, Pankaj Kalra, Blake Lin, Alvaro Padilla and Woo Young Choi.

Thanks to all my current labmates, especially Donovan Lee, Xin Sun, Hei (Anderson) Kam, Steve Volkman, Alejandro de la Fuente, Tim Bakhishev, Frank Liao, Cheuk Chi Lo, Changhwan Shin, Rhesa Nathanael, Pete Matheu, Reinaldo Vega, Nate Emley, Dave Carlton, Vincent Pott, Pratik Patel, Anu Bowonder, Darsen Lu, Yibo Yu, Helen Tran, Byron Ho and Michael Tseng for making it worthwhile to slave in the office and Microlab. I would like to thank the industrial visitors, including Yuri Yasuda-Masuoka, Taro Osabe, Takuro Matsutoya, Koichi Fukuda, Si-Woo Lee and Akira Hokazono for imparting so much knowledge and keeping our offices so lively.

I appreciate the opportunity to work with Frank DelRio and Sagi Mathai; they are both great collaborators and friends. I am also grateful to Noel Arellano, Sunil Bhave, Carrie Low, Johnny Ho, and Ming-Chun Tien for all their help in the Microlab. I will always be indebted to all the Microlab staff for their help with getting my projects completed, especially Sia Parsa, Kim Chan, Marilyn Kushner, Evan Stateler, Jay Morford, David Lo, Attila Horvath, Laszlo Petho, Xiaofan Meng, Rosemary Spivey and Anita Pongracz. I would especially like to thank Joe Donnelly for spending fixing novellus day in and day out - he made life less frustrating!

Thanks to all the people at Kovio Inc., for housing and maintaining the excimer laser system. Special thanks go to Pat Smith and Gloria Wong for allowing us to use the system.

I would like to thank the Palo Alto Research Center and ITRI research staff for great internships. I'd especially like to thank the guidance given to me by Jackson Ho and Jeng-Ping Lu from PARC and Yung-Hui Yeh and Chun-Cheng Cheng from ITRI. I have learned so much from them.

A special shout out to Ruth Gjerde, Mary Byrnes, Pat Hernan, Loretta Lutcher and Sheila Humphreys for always being so approachable and helpful to guiding me through my grad student experience.

Thanks to all my friends who have been with me from the start of grad school, especially Erik Steltz, Dave Nguyen, Dan Ceperley, Kofi Boakye, Ryan White, Lara Stoll, Leslie Hsu, Eric Tang and Anand Sarwate. We've come a long way! I'd like to thank Donovan Lee for being the best officemate and the closest thing to family on the West Coast. A very special thanks goes to Tim Bakhishev for his support and patience. He stuck with me through the stressful times and made life better, richer and fuller.

I would like to thank God for giving me the opportunity to go to grad school and for giving me such a blessed life and a wonderful family. My family has supported me through so much and has taught me to persevere. To Stan and Betty, you guys have been great, always calling me and keeping me upbeat. Stan, thanks for teaching me almost everything I know and for being the best brother anyone could ask for. To Mom and Dad, no words can describe what you've done for me. You have given me the support and the encouragement to do what I want. Without your sacrifices, I would not be here today. Thank you and God bless you!

### Chapter 1

### Introduction

### 1.1 Low-Thermal-Budget Device Fabrication for Large-Area Electronics and 3-D Integration with CMOS Electronics

Low-temperature fabrication of switching devices, such as thin film transistors and microelectromechanical (MEM) relays, is necessary for fabrication of large-area electronics, such as displays and RFID tags, fabricated on glass or plastic substrates, and for 3dimensional (3-D) integration with complementary metal-oxide-semiconductor (CMOS) electronics for enhanced integrated circuit (IC) chip functionality. In display applications, the process thermal budget is limited by the low strain point temperature of large-area glass or plastic substrates. Table 1.1 shows the maximum process temperature and optical transmission of some display substrates commonly used for large-area electronics [1, 2].

3-D integration of switching devices over CMOS electronics can enhance system functionality, improve packing density and reduce off-chip interconnects for better system performance. Fabrication of any device over CMOS electronics has process thermal budget limitations to prevent severe degradation of the underlying CMOS circuitry. Depending on the material of the CMOS metal layers, the maximum process thermal budget can range from  $450^{\circ}$ C for a standard 0.25- $\mu$ m foundry CMOS technology with aluminum

| Substrate                        | Maximum Process  | Optical      |

|----------------------------------|------------------|--------------|

| Material                         | Temperature (°C) | Transmission |

| Glass                            | 550-600          | >92%         |

| PET (polyethylene terephthalate) | 115-170          | $\sim 80\%$  |

| PES (polyethesulphone)           | 180-220          | < 80%        |

| PAR (polyarylate)                | 180              | $\sim 80\%$  |

| PA (polycarbonate)               | 115-130          | $\sim 80\%$  |

Table 1.1. Substrate materials for TFTs [1, 2].

interconnects [3] to 850°C for a specialized CMOS technology with tungsten interconnects [4]. It is desirable to limit the post-CMOS process thermal budget so as to be compatible with a conventional foundry process. That way, the benefits of a low-cost, reliable, high-performance CMOS foundry process can be leveraged.

Polycrystalline silicon thin film transistors (poly-Si TFTs) presently offer the highest performance among low-thermal budget devices. However, challenges for poly-Si TFT technology include formation of high-quality gate dielectric interfaces, passivation of defects, low on-state current, and performance non-uniformity. In this work, processes and device structures are discussed to alleviate these device issues.

### 1.2 Active Matrix Liquid Crystal Display Technology

Active matrix liquid crystal displays (AMLCDs) utilize TFTs to control an array of light valves. An exploded view of a twisted nematic liquid crystal display is shown in Fig. 1.1. Light from a backlight goes through a polarizing film. The polarized light then travels through an active matrix backplane consisting of pixels arranged in rows and columns with a TFT to control the light transmission at each pixel. Each pixel TFT drives a pixel electrode, which forms a liquid crystal capacitor with a common counter electrode on the cover sheet. The liquid crystal material is sandwiched between the backplane and cover sheet. The electric field across the liquid crystal determines whether it changes the

Figure 1.1. Schematic cross section of a liquid crystal display [5].

direction of light polarization. The light passes through the liquid crystal and is filtered to allow only red, green or blue light to reach the second polarizing film, which is typically oriented perpendicular to the first polarizing film.

A circuit schematic of the active matrix backplane is shown in Fig. 1.2. Here, the pixels are driven systematically row by row, by applying a voltage pulse to the row lines (which run horizontally across the backplane) to turn on the gates of the TFTs one row at a time. The row lines are often referred to as gate lines (denoted by "G" in Fig. 1.2). In this manner, the pixel electrodes are connected through the TFTs to the data lines (which run vertically across the backplane) and charged/discharged to the appropriate voltage for generating the desired image. Before each row is selected, the data voltages are applied to the column lines or data lines (denoted by "D" in Fig. 1.2) which are connected to the TFT drain electrodes. In the case of a twisted nematic liquid crystal display, if no electric field is applied, the liquid crystal molecules are twisted, rotating the direction of polarized light passing through them, so that light passes through the second polarizing film. If a voltage is applied, the liquid crystal molecules become aligned with the electric field, and do not rotate the direction of polarized light. In this case, the second polarizer blocks the

Figure 1.2. Circuit schematic of an active matrix backplane for a liquid crystal display.

light from passing through the front surface of the display [6]. From this description, it can be seen that the TFTs serve simply as pass-gates. Ideally, they should have moderately large on-state drive current, typically achieved with carrier mobility > 1  $\frac{\text{cm}^2}{\text{V}\cdot\text{s}}$  (to allow for the pixel electrodes to be charged/discharged with one row address time) and low off-state leakage (to maintain the pixel electrode voltage over one frame time).

#### **1.2.1** Thin Film Transistor Technologies

Many TFT channel materials and structures have been explored for AMLCD technology. Hydrogenated amorphous Si (a-Si:H) is the most widely used for large-area displays such as high-definition LCD televisions. However, this technology is limited to n-type TFTs due to electron mobilities of ~ 3 to 5  $\frac{\text{cm}^2}{\text{V}\cdot\text{s}}$  and hole mobilities that are ~100× lower [7].

Organic TFTs (oTFTs), on the other hand, have been explored as an alternative channel material for fabrication on low-cost, flexible substrates. Though oTFTs can be fabricated at ultra-low fabrication temperatures, the highest reported carrier mobilities are well below  $10 \frac{\text{cm}^2}{\text{V}\cdot\text{s}}$  for a pentacene channel material [8]. Organic TFTs are mostly p-type TFTs and complementary TFTs cannot be obtained using a single channel material.

Figure 1.3. Typical top gate, coplanar poly-Si TFT structure [12].

Poly-Si has the highest reported electron and hole carrier mobilities of all TFT materials. Using a conventional pulsed excimer laser crystallization technique to form the poly-Si channel material, electron and hole mobilities of at least 180  $\frac{\text{cm}^2}{\text{V}\cdot\text{s}}$  and 120  $\frac{\text{cm}^2}{\text{V}\cdot\text{s}}$ , respectively, can be achieved [9, 10]. Both n-type and p-type poly-Si TFTs can be fabricated to implement low-power CMOS display driver circuitry directly on the display panel. By integrating the display driver circuitry directly on the panel, off-panel connections to driver IC chips can be minimized to reduce form factor. The uniformity and reliability of poly-Si TFTs need to be improved in order to enable system-on-panel [11].

A top-gated, coplanar poly-Si TFT structure with self-aligned source and drain regions is usually employed (see Fig. 1.3). Typically, amorphous Si (a-Si) is deposited and crystallized to form the polycrystalline active layer. The active region is patterned and etched, followed by gate dielectric and gate layer deposition (either highly-doped poly-Si or metal). Next, the gate is patterned and etched. The dopants are then implanted by ion shower or ion implantation, forming self-aligned source and drain regions. Dopant activation by furnace annealing or laser annealing is typically performed afterwards. The device is completed by an silicon dioxide layer deposition, contact hole patterning, and lastly metallization deposition and patterning [12].

#### 1.2.2 Challenges for Poly-Si Thin Film Transistor Technology

Poly-Si is a heterogeneous material that consists of small crystalline grains that are randomly distributed throughout the film. The crystalline sizes range from tens of nanometres to several micrometres, depending on deposition and crystallization process conditions. Between the poly-Si grains exist grain boundaries, which are rich in Si dangling bonds. These dangling bonds create carrier trap sites that introduce localized energy states in the Si bandgap. The density and location of the dangling bond defects have significant impact on the electrical properties of the resulting poly-Si films.

Three crystallization methods are typically used in the fabrication of poly-Si TFTs: solid phase crystallization (SPC), excimer laser annealing (ELA) and metal-induced crystallization (MIC) or metal-induced lateral crystallization (MILC). In an SPC process, an a-Si film is furnace annealed at temperatures ranging from 550 to 600°C for up to 24 hours. The resulting film has moderate grain sizes with electron mobilities of ~40  $\frac{\text{cm}^2}{\text{V}\cdot\text{s}}$  [13]. Its process thermal budget is the highest of the three crystallization techniques.

In the MIC process, a metal deposited on top of an a-Si film decreases the crystallization temperature [14]. A thin metal film, such as nickel (Ni), is deposited on the a-Si film and the film stack is annealed. The metal promotes crystallization which occurs at lower temperatures and shorter anneal times compared to SPC. Metal traces in the channel region of a poly-Si TFT can be reduced by selectively depositing Ni only in the TFT source and drain regions and performing MILC. Longer anneals (*e.g.* 500°C, 5 hours) allow the Ni to move laterally across the channel, creating poly-Si films with large grain sizes and lower metal contaminants in the channel region. High performance poly-Si TFTs have been fabricated with reported electron mobilites of 120  $\frac{\text{cm}^2}{\text{V}\cdot\text{s}}$ , but at the trade-off of high leakage currents [15].

The most common crystallization method is pulsed ELA in which the a-Si film is exposed to an excimer laser beam of wavelength  $\lambda$ =193, 248 or 308 nm. The light is absorbed well

Figure 1.4. Dependence of the average Si grain size as a function of pulsed excimer laser fluence, from [16].

in Si at these wavelengths, causing the Si film to melt and resolidify in a polycrystalline state.

As shown in Fig. 1.4, the average grain radius size in a 100-nm thick Si film has a strong dependence on the laser energy density. At low laser energy densities, the film grain size slightly increases with increasing laser energy density. However, at some point, small increases in energy density result in much larger grain size due to the super lateral growth (SLG) phenomenon. In the SLG regime, the Si film is nearly completely melted. Most of the Si film melts upon the laser pulse, leaving isolated unmelted Si islands to nucleate grain growth, allowing considerable lateral grain growth. For laser fluences above the SLG regime, the Si film fully melts. Many nucleation sites are created upon super cooling, which results in poly-Si films with fine grains. The poly-Si TFTs with the best performance can be achieved when crystallized in the SLG regime [16]; however ELA has a narrow process window. Slight deviations in laser fluence and Si film thickness vary the average poly-Si grain size, contributing to device nonuniformity [16, 17]. Further improvements in carrier mobilities can be achieved by advanced laser crystallization techniques such as solid lateral solidification (SLS) to achieve larger Si grain sizes [18, 19].

Further TFT performance improvements can be made by defect passivation. Conventionally, TFTs are passivated by atomic hydrogen (H) from hydrogen plasma. At moderate temperatures (*e.g.* 350°C to 425°C), the H diffuses through the Si film and bonds with Si at the dangling bond defect sites. Defect passivation is easily integrated into the poly-Si TFT process after source/drain dopant activation and improves the performance and device uniformity across the large substrate [20]. However, weak Si-H bonds can break under electrical stress, which affects the device reliability [21].

### **1.3** Three-Dimensional Integrated Circuit Technology

Three-dimensional integration of active devices on top of CMOS electronics has been explored as the performance of devices has improved with scaling, so that interconnect RC delay can limit system performance. A schematic cross-section is shown in Fig. 1.5. Vertical integration can improve the device packing density, decrease interconnect resistance and capacitance (by using short vertical interconnects instead of long horizontal ones), or enhance functionality [22].

Many devices have been explored for vertical integration, such as poly-Si TFTs for high density SRAM cells [23, 24], MEMS inertial sensors [4], and transistors for 3-D nonvolatile memory [25] and logic applications [26, 27]. From Saraswat *et al.*'s analysis, variation in poly-Si TFTs due to grain boundary defects are too large to fulfill the requirements for 3-D ICs [22]. Of all the potential low-thermal-budget devices, microelectromechanical (MEM) relays have ideal switching behaviour, such as almost zero off-state current and steep subthreshold slope. Various relay designs for logic and memory applications have been proposed by several groups [28, 29, 30, 31, 32] which show ideal switching characteristics. However, it is necessary to form a high-quality structural material with excellent mechanical properties for integration on top of CMOS electronics.

Figure 1.5. Schematic cross-section of a 3-D integrated circuit with low-temperature transistors fabricated over CMOS electronics for memory applications, from [22].

### 1.3.1 Low-Thermal-Budget Structural Materials for MEMS

Silicon has excellent mechanical properties for MEMS devices. However, the process of depositing poly-Si by low pressure chemical vapor deposition (LPCVD) requires temperatures too high for post-CMOS integration. The deposition of a-Si is possible at low temperatures by sputtering or plasma enhanced chemical vapor deposition (PECVD) and a low-thermal-budget crystallization technique can be employed if it yields acceptable mechanical properties.

To date, poly-Si<sub>1-x</sub>Ge<sub>x</sub>, where x < 0.6, is a promising material for MEMS integration with CMOS technology. Poly-Si<sub>1-x</sub>Ge<sub>x</sub> can be deposited at temperatures down to 410°C. However, lower deposition temperatures lead to worse mechanical properties such as high strain gradient and high compressive residual stress [33]. Thus, there is a need to develop a suitable structural material that can be formed at low process temperatures with better mechanical properties.

### 1.4 Thesis Organization

This thesis is first motivates low-thermal-budget device structures and processes. Improvements that can be made to poly-Si TFT technology are then described. Then the mechanical properties of low-thermal-budget materials is investigated for MEMS integration with CMOS electronics.

In chapter 2, an ultra-low-temperature gate dielectric formation process is investigated for compatibility with flexible plastic substrates, with maximum substrate temperature  $\leq$  150°C. At such low temperatures, conventional gate oxide formation processes result in a high density of interface traps and oxide charge. A UV-enhanced oxidation process is introduced to form an ultrathin high-quality gate dielectric interfacial layer between the semiconductor and the gate dielectric.

In chapter 3, ion implantation of selenium (Se) into the a-Si channel layer prior to ELA is investigated as a means for defect passivation. The Se is shown to successfully passivate defects in the poly-Si film and improve the performance of the TFT. In comparison with a conventional hydrogen plasma passivation treatment, Se passivation yields improvement in TFT reliability.

Further improvements to minimize the TFT performance sensitivity to grain boundaries is examined in chapter 4, where an alternative TFT design is proposed. The accumulationmode TFT employs higher channel doping which is the same type as the source and drain regions to decrease the effects of grain boundary defects. Two-dimensional device simulations are performed to optimize and assess the advantages of the design.

In chapter 5, a poly-Si tunneling field effect transistor (TFET) structure is fabricated to explore the possibility of enhancing TFET on-state performance. The presence of a large lateral electric field at the drain junction allows band-to-band tunneling and trap-assisted tunneling components. Large on-state current can be achieved as compared to a control TFT.

In chapter 6, the mechanical properties of low-thermal-budget materials are investigated

for post-CMOS MEMS integration. Both sputtered metals and poly-Si crystallized at low-temperatures are examined and compared to state-of-the-art polycrystalline silicongermanium technology.

Lastly, chapter 7 summarizes the contributions of this research and proposes future work that builds upon this work.

### 1.5 References

- Wagner, S., and Conde, J. P., Thin-film silicon materials and devices for large-area electronics 2004 MRS Spring Meeting Symopsium Tutorial Program, Apr. 12 2004.

- [2] Kuo, Y. Thin film transistors materials and processes, volume 2: Amorphous silicon thin film transistors, Norwell: Kluwer Academic Publishers, 2004, p. 56.

- [3] Takeuchi, H., Wung, A., Sun, X., Howe, R. T., and King, T.-J., "Thermal budget limits of quarter-micrometer foundry CMOS for post-processing MEMS devices," *IEEE Transactions on Electron Devices*, vol. 52, no. 9, pp. 2081-2086, Sept. 2005.

- [4] Yun, W., Howe, R. T., and Gray, P. R., "Surface micromachined, digitally force-balanced accelerometer with integrated CMOS detection circuitry," *Proceedings of IEEE Solid-State Sensor Actuator Workshop*, Hilton Head, SC, pp. 126-131, June 1992.

- Britannica Online Encyclopedia, liquid crystal display: active-matrix TFT liquid crystal display, http://media-2.web.britannica.com/eb-media/28/70028-004-169E2ED7.gif (accessed Nov. 16, 2008).

- Kuo, Y., Thin film transistors materials and processes, volume 2: Polycrystalline silicon thin film transistors, Norwell: Kluwer Academic Publishers, 2004, pp. 360-362.

- [7] Lin, J.-L., Sah, W.-J., and Lee, S.-C., "Amorphous-silicon thin-film transistors with very high field-effect mobility," *IEEE Electron Device Letters*, vol. 12, no. 3, pp. 120-121, Mar. 1991.

- [8] Dimitrakopoulos, C. D., and Mascaro, D. J., "Organic thin film transistors: A review of recent advances," *IBM Journal of Research and Development*, vol. 45, no. 1, pp. 11-27, Jan. 2001.

- [9] Sameshima, T., Usui, S., and Sekiya, M., "XeCl excimer laser annealing used in the fabrication of poly-Si TFT's," *IEEE Electron Device Letters*, vol. EDL-7, no. 5, pp. 276-278, May 1986.

- [10] Uchikoga, S., and Ibaraki, N., "Low temperature poly-Si TFT-LCD by excimer laser anneal," *Thin Solid Films*, vol. 383, pp. 19-24, 2001.

- [11] Voutsas, T., Schuele, P., Crowder, B., Joshi, P., Sposili, R., Kisdarjono, H., Afentakis, T., and Hartzell, J., "Next generation of poly-Si TFT technology: material improvements and novel device architectures for system-on-panel (SOP)," *Sharp Technical Journal*, vol. 92, pp. 29-34, 2005.

- [12] Brotherton, S. D., "Polycrystalline silicon thin film transistors," Semiconductor Science and Technology, vol. 10, no. 6, pp. 721-738, June 1995.

- [13] Aoyama, T., Kawachi, G., Konishi, N., Suzuki, T., Okajima, Y., and Miyata, K., "Crystallization of LPCVD silicon films by low temperature annealing," *Journal of Electrochemical Society*, vol. 136, no. 4, pp. 1169-1173, Apr. 1989.

- [14] Hiraki, A., "Low temperature reactions at Si/metal interfaces: what is going on at the interfaces," *Surface Science Reports*, vol. 3, no. 7, pp. 357-412, 1984.

- [15] Lee, S.-W., and Joo, S.-K., "Low temperature poly-Si thin-film transistor fabrication by metal-induced lateral crystallization," *IEEE Electron Device Letters*, vol. 17, no. 4, pp. 160-162, Apr. 1996.

- [16] Im, J. S., Kim, H. J., and Thompson, M. O., "Phase transformation mechanisms involved in excimer laser crystallization of amorphous silicon films," *Applied Physics Letters*, vol. 63, no. 14, pp. 1969-1971, Oct. 1993.

- [17] Brotherton, S. D., McCulloch, D. J., Gowers, J. P., Ayres, J. R., and Trainor, M. J.,

"Influence of melt depth in laser crystallized poly-Si thin film transistors," *Journal of Applied Physics*, vol. 82, no. 8, pp. 4086-4094, Oct. 1997.

- [18] Sposili, R. S., and Im, J. S., "Sequential lateral solidification of thin silicon films on SiO<sub>2</sub>," *Applied Physics Letters*, vol. 69, no. 19, pp. 2864-2866, Nov. 1996.

- [19] Im, J. S., Sposili, R. S., and Crowder, M. A., "Single-crystal Si films for thin-film transistor devices," *Applied Physics Letters*, vol. 70, no. 25, pp. 3434-3436, June 1997.

- [20] Higashi, S., Abe., D., Hiroshima, Y., Miyashita, K., Kawamura, T., Inoue, S., and Shimoda, T., "Development of high-performance polycrystalline silicon thin-film transistors (TFTs) using defect control process technologies," *IEEE Electron Device Letters*, vol. 23, no. 7, pp. 407-409, July 2002.

- [21] Wu, I.-W., Jackson, W. B., Huang, T.-Y., Lewis, A. G., and Chiang, A., "Mechanism of device degradation in n- and p-cheannel polysilicon TFT's by electrical stressing," *IEEE Electron Device Letters*, vol. 11, no. 4, pp. 167-170, Apr. 1990.

- [22] Saraswat, K. C., Banerjee, K., Joshi, A. R., Kalavade, P., Kapur, P., and Souri, S. J.,

"3-D ICs: Motivation, performance analysis and technology," *Proceedings of the 26th European Solid State Circuits Conference*, pp. 406-414, Sept. 2000.

- [23] Yamanaka, T., Hashimoto, T., Hashimoto, N., Nishida, T., Shimizu, A., Ishibashi, K., Sakai, Y., Shimohigashi, K., and Takeda, E., "A 25 μm<sup>2</sup> new poly-Si PMOS load (PPL) SRAM cell having excellent soft error immunity," *IEEE International Electron Device Meeting*, pp. 48-51, Dec. 1988.

- [24] Ohkubo, H., Horiba, S., Hayashi, F., Andoh, T., Kawaguchi, M., Ochi, Y., Soeda, M., Nozue, H., Miyamoto, H., Ohkawa, M., Shimizu, T., and Sasaki, I., "16Mbit SRAM cell technologies for 2.0V operation," *IEEE International Electron Device Meeting*, pp. 481-484, Dec. 1991.

- [25] Endoh, T., Kinoshita, K., Tanigami, T., Wada, Y., Sato, K., Yamada, K., Yokoyama, T., Takeuchi, N., Tanaka, K., Awaya, N., Sakiyama, K., and Masuoka, F., "Novel ultrahigh-density flash memory with a stacked-surrounding gate transistor (S-SGT) structured cell," *IEEE Transactions on Electron Devices*, vol. 50, no. 4, pp. 945-951, Apr. 2003.

- [26] Varadarajan, V., Yasuda, Y., Balasubramanian, S., and King Liu, T.-J., "WireFET technology for 3-D integrated circuits," *IEEE International Electron Device Meeting*, San Francisco, CA, Dec. 2006.

- [27] Wang, Y. A., and Ferendeci, A. M., "RF MEMS switches for 3D-IC phased array antenna modules." *IEEE Radio and Wireless Conference*, pp. 269-272, 2002.

- [28] Kam, H., Lee, D. T., Howe, R. T., and King, T.-J., "A new nano-electro-mechanical field effect transistor (NEMFET) design for low-power electronics," *IEEE International Electron Device Meeting*, Washington D.C., pp. 477-480, Dec. 2005.

- [29] Abele, N., Fritschl, R., Boucart, K., Casset, F., Ancey, P., and Ionescu, A.M., "Suspended-gate MOSFET: bringing new MEMS functionality into solid-state MOS transistor," *IEEE International Electron Device Meeting*, Washington D.C., pp. 1075-1077, Dec. 2005.

- [30] Jang, W. W., Yoon, J.-B., Kim, M.-S., Lee, J.-M., Kim, S.-M., Yoon, E.-J., Cho, K. H., Lee, S.-Y., Choi, I.-H., Kim, D.-W., and Park, D. "NEMS switch with 30 nm-thick beam and 20-nm-thick air-gap for high density non-volatile memory applications," *Solid-State Electronics*, vol. 52, pp. 1578-1583, Aug. 2008.

- [31] Jang, W. W., Lee, J. O., Yoon, J.-B., Kim, M.-S., Lee, J.-M., Kim, S.-M., Cho, K. H., Kim, D.-W., Park, D., and Lee, W.-S., "Fabrication and characterization of a nanoelectromechanical switch with 15-nm-thick suspension air gap," *Applied Physics Letters*, vol. 92, pp. 103110-1-103110-3, Mar. 2008.

- [32] Choi, W. Y., Kam, H., Lee, D., Lai, J., King Liu, T.-J., "Compact nano-electro-

mechanical non-volatile memory (NEMory) for 3D integration," *IEEE International Electron Device Meeting*, Washington D.C., pp. 603-606, Dec. 2007.

[33] Low, C. W., King Liu, T.-J., and Howe, R. T., "Characterization of polycrystalline silicon-germanium film deposition for modularly integrated MEMS applications," *Journal of Microelectromechanical Systems*, vol. 16, no. 1, pp. 68-77, Feb. 2007.

### Chapter 2

# Ultra-Low-Temperature Gate Oxide Interface Formation

### 2.1 Introduction

High-performance polycrystalline silicon thin film transistors (poly-Si TFTs) fabricated on plastic substrates have been demonstrated by several groups [1, 2, 3, 4]. Due to the low strain point of plastic substrates, the maximum substrate process temperature is limited to  $\sim 150^{\circ}$ C. At ultra-low deposition temperatures, it is difficult to obtain a dense silicon dioxide (SiO<sub>2</sub>) gate dielectric with a high-quality Si/SiO<sub>2</sub> interface. Since thermal oxidation is incompatible with low-temperature processing, typical methods for poly-Si TFT oxide formation have been plasma-enhanced chemical vapor deposition (PECVD) [1, 2] and physical vapor deposition (PVD) by reactive sputtering [5]. High-density-plasma chemical vapor deposition processes, including electron cyclotron resonance chemical vapor deposition (ECR-CVD) [3] and inductively-coupled plasma chemical vapor deposition (ICP-CVD) [4], have achieved improved gate oxide characteristics.

Gate oxides can be deposited by PECVD at low temperatures compatible with plastic substrates; however, common parallel-plate PECVD systems cause damage at the  $Si/SiO_2$