## **Compact Modeling of Nanoscale CMOS**

Chung-Hsun Lin

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2007-169 http://www.eecs.berkeley.edu/Pubs/TechRpts/2007/EECS-2007-169.html

December 19, 2007

Copyright © 2007, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### **Compact Modeling of Nanoscale CMOS**

by

### Chung-Hsun Lin

B.S. (National Taiwan University, Taiwan) 1999 M.S. (National Taiwan University, Taiwan) 2001

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

#### GRADUATE DIVISION

of the

### UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Chenming Hu, Chair Professor Ali M. Niknejad Professor Oscar Dubon

Fall 2007

The dissertation of Chung-Hsun Lin is approved:

| Prof. Chenming Hu, Chair | Date |

|--------------------------|------|

|                          |      |

| Prof. Ali M. Niknejad    | Date |

|                          |      |

| Prof. Oscar Dubon        | Date |

University of California, Berkeley

Fall 2007

## **Compact Modeling of Nanoscale CMOS**

Copyright 2007

by

Chung-Hsun Lin

#### Abstract

#### **Compact Modeling of Nanoscale CMOS**

by

Chung-Hsun Lin

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Chenming Hu, Chair

The scaling of bulk CMOS technology results in incredible reduction of cost-percomputation with higher computational performance. It is conventionally achieved through the combination of thinner gate oxide, higher effective channel doping and shallower source/drain junction depth. However, these techniques are rapidly approaching material and process limits. The multi-gate FET such as FinFET has emerged as the most promising candidate to extend CMOS scaling beyond the 22nm technology node. The strong electrostatic control over the channel originating from the use of multiple gates reduces the coupling from source and drain. It enables the multigate transistor to be scaled beyond bulk planar CMOS for a given dielectric thickness.

A compact model serves as a link between process technology and circuit design. It maintains a fine balance between accuracy and simplicity. An accurate model based on physics allows the process engineers and circuit designers to make projections beyond the available silicon data for scaled dimensions and also enables fast circuit and device cooptimization. It is thus necessary to develop a compact model of multi-gate FETs for technology and circuit development in the short term and for product design in the longer term.

Full scale multi-gate FET compact models are developed. Unique device physics in the multi-gate MOSFET due to extra gates are studied and investigated. Modeling methodologies are proposed to incorporate these unique multi-gate physics in the compact model. Different flavors of the multi-gate FETs are modeled in two categories: the symmetric/common-gate multi-gate FETs and the independent/asymmetric multi-gate FETs. The complete multi-gate compact models are verified with TCAD simulation results and experimental data.

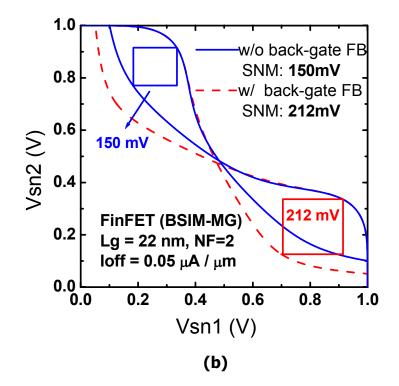

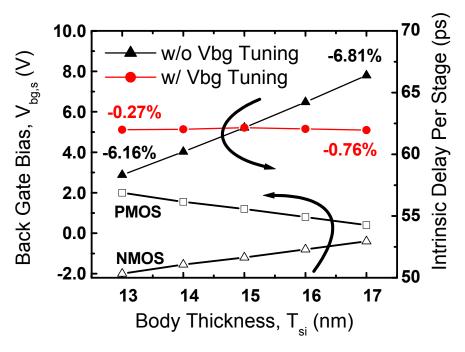

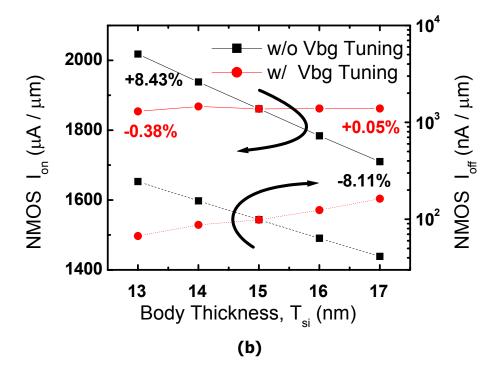

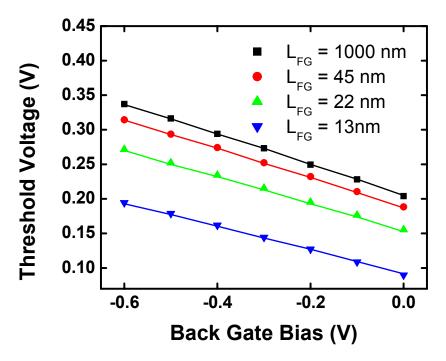

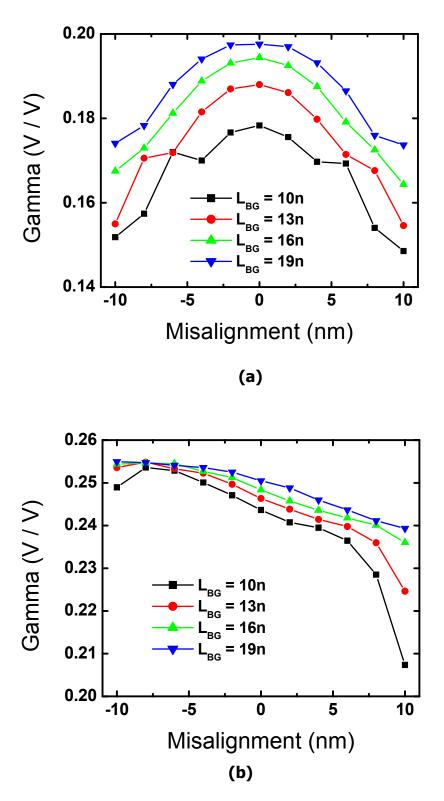

The performance comparison and design concepts of multi-gate-based logic and memory circuits are studied using the BSIM-MG model. The impact of the process variation can be tuned out by using back-gate tuning. The impact of back-gate length and misalignment on the threshold voltage is discussed.

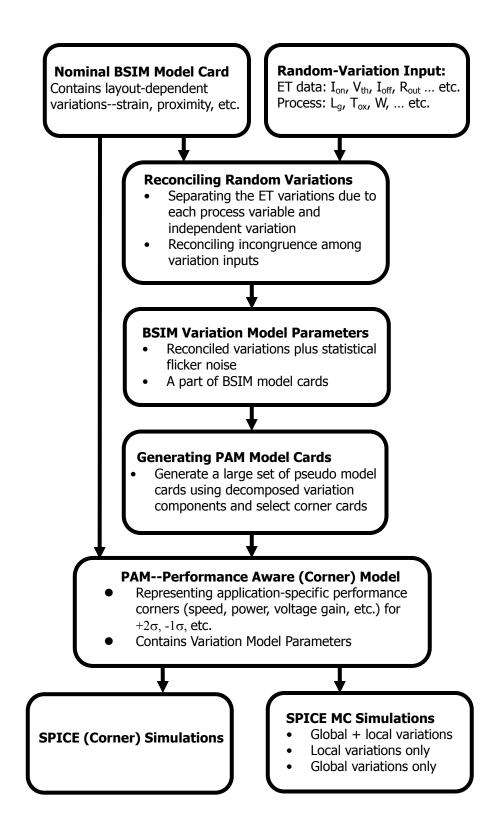

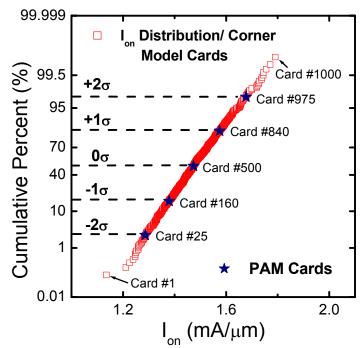

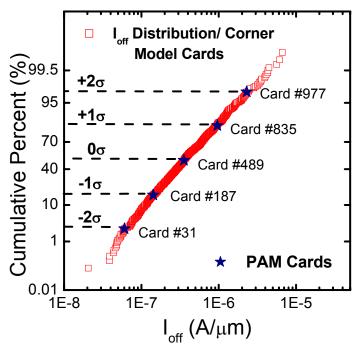

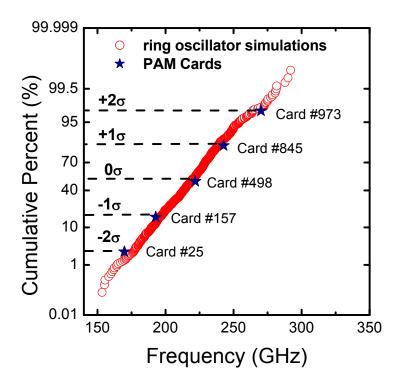

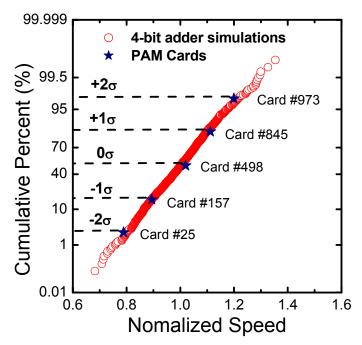

In the sub-45nm CMOS technology regime, the impact of device variations on circuit functionality becomes critical. The scaling of the device geometry makes device characteristics more sensitive to the fluctuation of process steps. A novel methodology for generating Performance Aware Models (PAM) cards is presented for accurately predicting the statistical variations of VLSI circuit performance due to process variation. The PAM cards also improve the accuracy of Monte Carlo simulations by reconciling the physical and electrical-test variances.

Professor Chenming Hu Dissertation Committee Chair To my family, for the their love, encouragement, and support

### **Table of Contents**

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 1.1 CMOS Technology Scaling and Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                |

| 1.2 Advanced CMOS Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                  |

| 1.3 Compact Modeling of Multi-Gate MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                                                |

| 1.4 Process Variations in Compact Models                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                                |

| 1.5 Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                  |

| 1.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                                                                                                               |

| Chapter 2: Modeling of Physical Effects in Multi-Gate MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                          | ſs14                                                                                                             |

| 2.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14                                                                                                               |

| 2.2 Quantum Mechanical Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17                                                                                                               |

| 2.3 Short Channel Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                  |

| 2.4 Corner Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                  |

| 2.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                  |

| 2.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                                                                                               |

| Chapter 3: BSIM-CMG: A Compact Model for Symmetric/Com                                                                                                                                                                                                                                                                                                                                                                                                                                | C (                                                                                                              |

| Multi-Gate MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                  |

| Multi-Gate MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b></b>                                                                                                          |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.                                                                                                                                                                                                                                                                                                                                                                                              | <b>48</b><br>48<br>53                                                                                            |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.                                                                                                                                                                                                                                                                                                                                                             | <b>48</b><br>48<br>53<br>59                                                                                      |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.                                                                                                                                                                                                                                                                                                                   | <b>48</b><br>48<br>53<br>59<br>66                                                                                |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.                                                                                                                                                                                                                                                                      | <b>48</b><br>48<br>53<br>59<br>66<br>70                                                                          |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.         3.6 Experimental Verification.                                                                                                                                                                                                                               | <b>48</b><br>48<br>53<br>59<br>66<br>70<br>72                                                                    |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.         3.6 Experimental Verification.         3.7 Summary.                                                                                                                                                                                                          | <b>48</b><br>48<br>53<br>59<br>66<br>70<br>72<br>78                                                              |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.         3.6 Experimental Verification.                                                                                                                                                                                                                               | <b>48</b><br>48<br>53<br>59<br>66<br>70<br>72<br>78                                                              |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.         3.6 Experimental Verification.         3.7 Summary.                                                                                                                                                                                                          | <b>48</b><br>48<br>53<br>59<br>66<br>70<br>72<br>78                                                              |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.         3.6 Experimental Verification.         3.7 Summary.         3.8 References.                                                                                                                                                                                  | 48         48         53         59         66         70         72         78         79                       |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.         3.6 Experimental Verification.         3.7 Summary.         3.8 References.         Chapter 4: Independent Multi-Gate MOSFETs – Model and Circuit Implications.         4.1 Introduction.                                                                    | 48         48         53         59         66         70         72         78         79         83         83 |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.         3.6 Experimental Verification.         3.7 Summary.         3.8 References.         Chapter 4: Independent Multi-Gate MOSFETs – Model and Circuit Implications.         4.1 Introduction.         4.2 BSIM-IMG: A Compact Model for Independent Multi-Gate N | 48<br>48<br>53<br>59<br>66<br>70<br>72<br>72<br>78<br>79<br><b>83</b><br>83<br>MOSFETs86                         |

| Multi-Gate MOSFETs.         3.1 Introduction.         3.2 Surface Potential Calculation.         3.3 Drain Current Model.         3.4 Charge and Capacitance Model.         3.5 Physical Effects of Real Device.         3.6 Experimental Verification.         3.7 Summary.         3.8 References.         Chapter 4: Independent Multi-Gate MOSFETs – Model and Circuit Implications.         4.1 Introduction.                                                                    | 48<br>48<br>53<br>59<br>66<br>70<br>72<br>72<br>78<br>79<br><b>83</b><br>MOSFETs86<br>98                         |

| Chapter 5: Circuit Design Using Multi-Gate Transistors              | 110            |

|---------------------------------------------------------------------|----------------|

| 5.1 Introduction                                                    | 110            |

| 5.2 Evaluation of Circuit Performance for Double-Gate MOSFETs       | 113            |

| 5.3 Circuit Performance Comparison of CMG and IMG                   | 124            |

| 5.4 VDD Scaling for FinFET Logic and Memory Circuits:               |                |

| Impact of Process Variations and SRAM Stability                     | 133            |

| 5.5 Summary                                                         | 144            |

| 5.6 References                                                      | 145            |

| Chapter 6: Statistical Compact Modeling of Variations in Nano MOSFI | E <b>Ts148</b> |

| 6.1 Introduction                                                    | 148            |

| 6.2 Methodology of Generating PAM Cards                             | 151            |

| 6.3 Results and Discussion                                          | 159            |

6.4 Summary.

164

6.5 References.

164

#### Acknowledgements

First and foremost, I would like to express my gratitude to Professor Chenming Hu for being my Ph.D. research advisor during my Ph.D. study at U.C. Berkeley. His enthusiasm, guidance and wealth of technical knowledge provided excellent inspiration and insight to my research. I always felt excited and refreshed after our group and individual meetings. He was also an outstanding mentor while I was a teaching assistant for EE130. I am very grateful for his valuable suggestions and help regarding many other aspects of my life, especially being my witness at my wedding at San Francisco City Hall. It is my great pleasure and honor to have known him and his family.

I would also like to thank Professor Ali Niknejad for co-directing the BSIM project, serving as the chair of my qualifying exam committee, and the member of my dissertation committee. Our technical discussions were always rich and fruitful. His insights on RF applications and device modeling have inspired me a lot during the past years. Thanks to Professor Vivek Subramanian for serving as the member in my qualifying exam committee, providing valuable discussion on device physics, and mentoring the Cal VIEW consultant task. I am also grateful to Professor Oscar Dubon for serving as the member in my qualifying exam committee. Thanks to Professor Tsu-Jae King Liu for her helpful discussion regarding my research.

I am grateful to Professor Mansun Chan of Hong Kong UST for serving as my research co-advisor during my first year at Berkeley when Professor Hu was on sabbatical leave. Thanks to him for leaving me his nice car to me when he went back to Hong Kong.

I am indebted to many former and current members of the device group in 373

iv

Cory Hall. Special thanks to my cubicle-mates: Jo, DT Lee, Hiu-Yung, Dunga, and Blake. I would like to thank fellow group members Mohan Dunga, Jane Xi, Hui Wan, Darsen Lu, Morgan Yang, Jodie Zhang, Koichi Fukuda, and Yuri Masuoka for invaluable discussions. I would also like to thank Wen-Chin Lee, Yee-Chia Yeo, Qiang Lu, Kevin Yang, Kevin Cao, Leland Chang, Xuejue Huang, Yang-Kyu Choi, Hideki Takeuchi, Pin Su, Pushkar Ranade, Patrick Xuan, Min She, Shiying Xiong, Sriram Balasubramanian, Kyoungsub Shin, Dae-Won Ha, Hiu-Yung Wong, Vidya Varadarajan, Marie-Ange Eyoum, Alvaro Padilla, Donovan Lee, Joanna Lai, Josei Chang, Paul Chang, Yu-Chih Tseng, Blake Lin, Pankaj Kalra, Andrew Carlson, Hei Kam, Xin Sun, Anu Bowonder, Pratik Patel, and Taro Osabe for their friendship and fruitful discussions.

In the summer of 2004 and 2005, I was fortunate to work at IBM T. J. Watson Research Center. I learned an extraordinary amount from many outstanding researchers in the semiconductor field. Special thanks to Wilfried Haensch, Leland Chang, Mark Ketchen, and Paul Solomon for supervising me. I am also grateful to Koushik Das, Meikei Ieong, Bruce Doris, Richard Williams, Robert Dennard, Shih-Hsien Lo, Phil Oldiges, and Robert Miller for valuable discussions.

I would like to thank industrial liaisons for their valuable support and feedbacks. I would like to thank Richard Williams and Wilfried Haensch from IBM for SOI device concept and modeling issues; Judy An, Brain Chen and Jung-Suk Goo from AMD for BSIMSOI model discussion; Weidong Liu and Joddy Wang from Synoposys for BSIM model discussion; Fu-Liang Yang, Jiun-Ren Hwang and Sally Liu from TSMC for providing data and discussing models; Keith Green and Wade Xiong, from TI for valuable discussions and providing data. This research was supported by Semiconductor Research Corporation. I am thankful for the efficient assistance from administrative staff in the EECS Department. Thanks to Judy Fong, Elise Mills, and Charlotte Jones for their warmhearted support. Special thanks to Ruth Gjerde for her timely information regarding department policy.

I am honored that I could play euphonium in Berkeley University Wind Ensemble throughout my whole Ph.D. career. Thanks to Robert Calonico for his outstanding conducting and music skills. I am also honored to have served as the course consultant of Cal VIEW EE231 class for ten semesters. It was a great experience to interact with industrial engineers. Thanks for the valuable guidance and administrative help from Pam Atkinson, and Isabel Blanco.

During my life at Berkeley, I am fortunate to know many wonderful friends from Taiwan. Special thanks to Stanley Wang, Enyi Lin for picking me up at SFO on the first day of my life in the U.S. Thanks to Victor, Wanwan, Emelie, Yu-Chieh, Mike, Jackey, Ilin, Kai, Sandy, Blake, and Vivian for all the joyful and exciting activities, such as biking, pig, poker, board game, chatting and drinking.

Most importantly, I would like to thank my family for their support throughout my life. My lovely wife, Pei Chen, has been a great blessing to me. I am very grateful to her loving support and patience during my Ph.D. career at Berkeley.

# Chapter 1

# Introduction

## **1.1 CMOS Technology Scaling and Challenges**

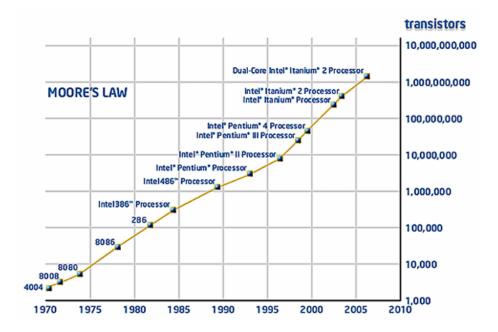

Throughout recent history, silicon-based mircoelectronics has experienced tremendous growth and performance improvements since the innovative concept of integrated circuit (IC) was invented by J. Kilby in late 1950's [1.1]. The computational power is enhanced at a tremendous rate with chpeaper cost, resulting in incredible reduction of cost-per-computation with higher computational performance. In 1965, Gordon Moore made a very famous and important oberservation that the complexity of ICs approximately doubles every year (Moore later refined the period to two years) [1.2]. This obeservation is the well known "Moore's Law" [1.3]. Over the past four decades, the

scaling of the conventional metal-oxide-semiconductor field-effect transistor (MOSFET) has been accomplished with technology innovations and led the device dimensions well into the nanometer era as shown in Fig. 1.1.

Fig. 1.1 Moore's Law has delivered exponential increases in the number of transistors integrated into microprocessors and other leading platform ingredients. [Source: Intel Corporation]

The scaling of MOSFET is conventionally achieved through the combination of thinner gate oxide, higher effective channel doping, and shallower source/drain junction depth [1.4-1.5]. However, the performance improvement by scaling the dimension of MOSFET is approaching a limit. The channel potential control from the gate electrode

degrades as the gate length decreases. The potential penetration from the drain electrode leads to severe short channel effects (SCE), such as threshold voltage roll-off, subthreshold swing degradation, and drain-induced barrier lowering (DIBL). SCE leads to significant increase of off-state drain current, which will limit the scaling of MOSFET due to significant leakage power consumption. The thinner gate oxide leads to an exponentially increased leakage current due to direct tunneling through the dielectric [1.6]. The higher effective channel doping degrades the carrier mobility and increases source/drain junction leakage. The higher channel doping also induces doping fluctuation, and thus threshold voltage variation, in the nanoscale transistor [1.7]. The formaiton of shallower source/drain junction depth is limited due to the thermal budget of dopant activation [1.8].

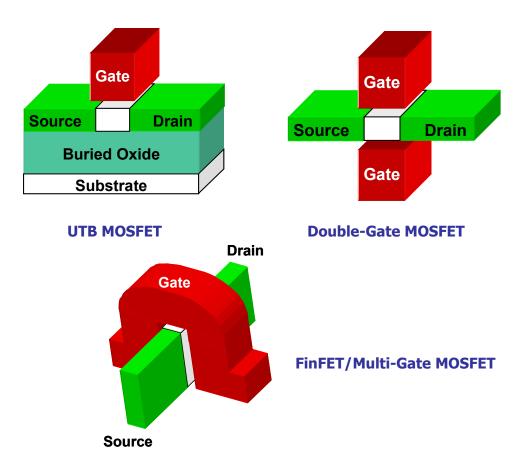

To overcome the above issues, the mobility-enhanced technology and high-K/metal-gate are introduced to improve the on-state drive current without degrading off-state leakage current [1.9, 1.10]. To further maintain the performance improvement by scaling the device dimension, the advanced transistor structures such as ultra-thin-body (UTB) MOSFET and multi-gate (MG) MOSFET are expected to be introduced in the future technology nodes.

## **1.2 Advanced MOSFET Structures**

As mentioned in the previous section, the off-state leakage current increases as gate length decreases. The leakage path is located far from the dielectric/channel interface, which is least effectively controlled by the gate electrode. Advanced MOSFET structures utilize the thin body to suppress the off-state leakage path [1.11, 1.12]. The short channel behavior is controlled by the thickness of the thin body instead of the channel doping. Therefore, the channel can be lightly doped. The lightly doped channel of advanced MOSFET structures provides several advantages compared to the conventional planar MOSFET:

- (i) Improved mobility due to lower vertical field and less columbic scattering

- (ii) Improved subthreshold swing due to better control of SCE

- (iii) Less parasitic junction capacitance

However, the fabrication of such advanced structures has difficulties of process integration. Maintaining uniformity of thin-body thickness over the entire wafer is very challenging. The series resistance could be potentially problematic due to the nature of ultra-thin film.

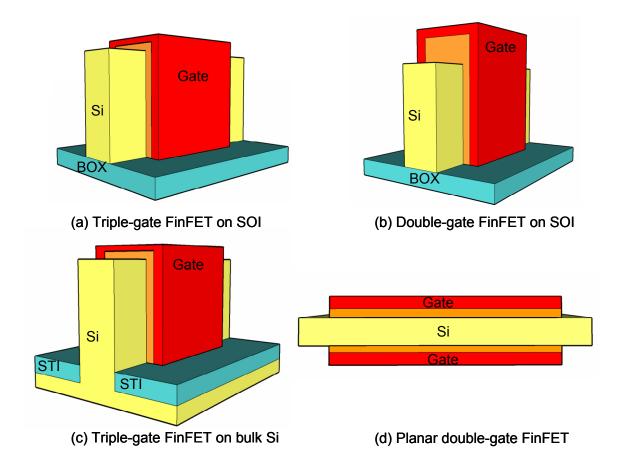

Multi-gate FETs such as FinFETs have emerged as the most promising candidates to extend the CMOS scaling beyond 22nm technology node [1.13]. FinFET is known to be

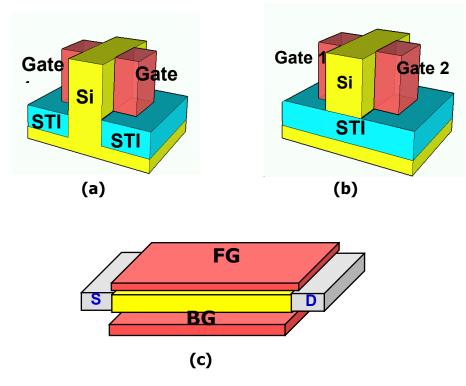

the most manufacturable thin-body devices due to self-aligned gate electrodes which are compatible with conventional planar bulk CMOS process. The FinFET can be built on either SOI or bulk silicon substrate. The strong electrostatic control over the channel originating from the use of multiple gates reduces the coupling between source and drain in the subthreshold region and it enables the multi-gate transistor to be scaled beyond bulk planar CMOS for a given dielectric thickness. Fig. 1.2 shows examples of advanced thin-body MOSFET structures.

Fig. 1.2 Examples of advanced thin-body MOSFET structures

## **1.3 Compact Modeling of Multi-Gate MOSFETs**

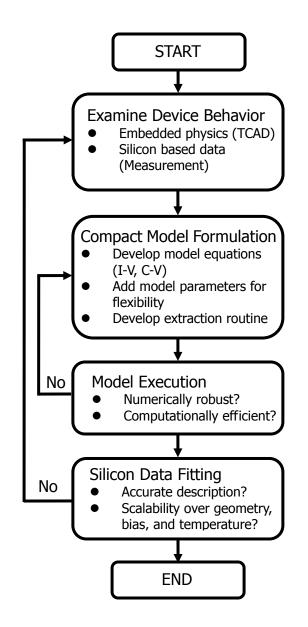

A compact model serves as a link between process technology and circuit design. It is a concise mathematical description of the complex device physics in the transistor. A compact model maintains a fine balance between accuracy and simplicity. An accurate model based on physics allows the process engineer and circuit designer to make projections beyond the available silicon data (scalability) for scaled dimensions and also enables fast circuit and device co-optimization. The simplifications in the physics enable very fast analysis of device/circuit behavior compared to the much slower numerical based TCAD simulations. It is thus necessary to develop a compact model of multi-gate FETs for technology/circuit development in the short term and for product design in the longer term.

One of the biggest challenges in modeling multi-gate FETs is the need to model several flavors of multi-gate FETs. The silicon body can be controlled by either two gates or three gates or four gates. The gates can all be electrically interconnected or they can be biased independently. Multi-gate FETs can be built on SOI or bulk silicon. It is important to obtain a versatile model which can model all the different types of multi-gate FETs without making the model computationally intensive. Fig. 1.3 shows the development cycle for a compact model [1.14].

Fig. 1.3 The development cycle for a compact model [1.14]

## **1.4 Process Variations in Compact Models**

In the sub-45nm CMOS technology regime, the impact of device variations on circuit

functionality becomes critial. The scaling of the device geometry makes device characteristics more sensitive to the fluctuation of process steps. The control of the critical diemension such as gate length continues to be a difficult challenge since the physical gate length is considerably smaller than the lithography printed line width in the nanoscale regime. The fluctuations during the processing lead to variability in device characteristics both within the die and between the dies. This leads to greater variance of device/circuit performance around the nominal technology node of circuit design. Statistical modeling techniques are essential for estimating circuit yields, designing manufacturable and robust systems. Therefore, statistical compact modeling for considering process variation becomes more important than ever.

## **1.5 Objectives**

In this dissertation, compact models are developed for multi-gate MOSFET and statistical process variations. The unique device physics of multi-gate MOSFET are studied and modeled for inclusion in the multi-gate compact model. The circuit design concept of the advanced MOSFET structures are studied and discussed using the developed compact model.

Chapter 2 presents the proposed modeling methodologies and approaches to

incorporate these unique multi-gate physics in the compact model. The proposed models are verified with 2-D and 3-D TCAD simulation results.

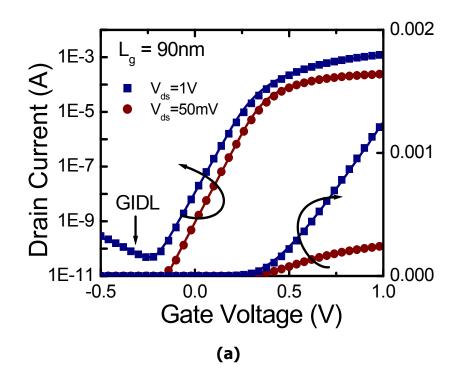

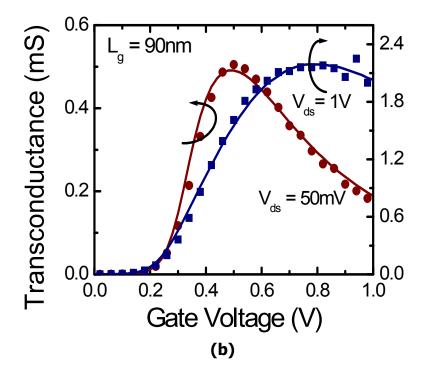

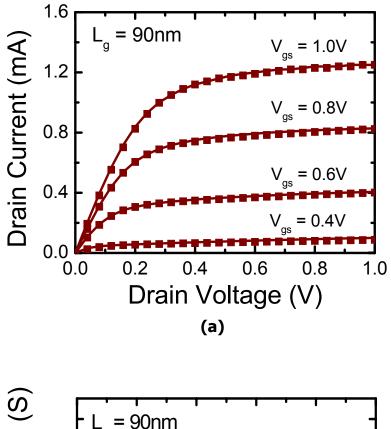

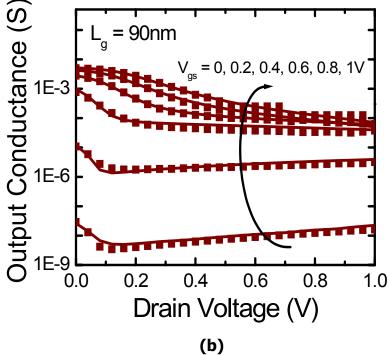

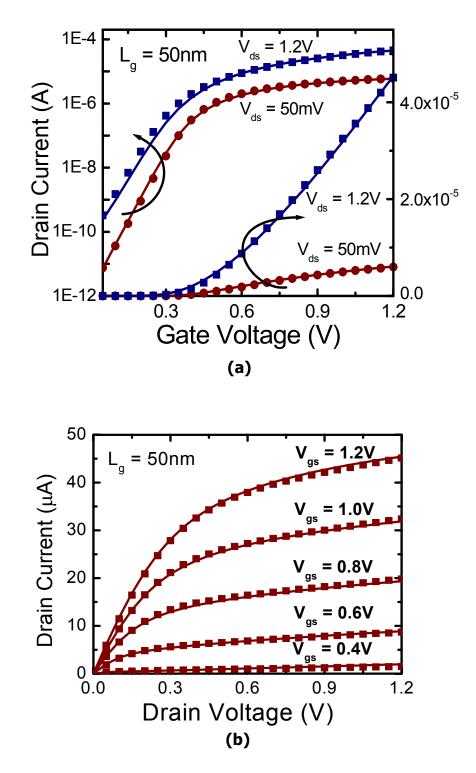

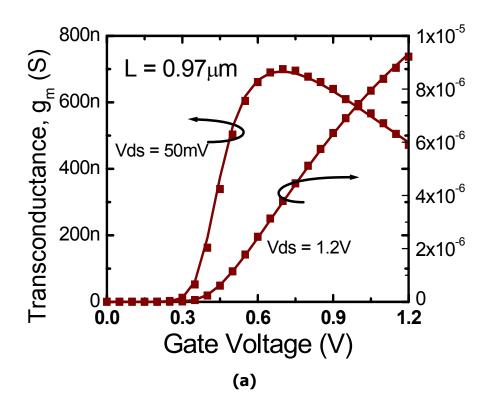

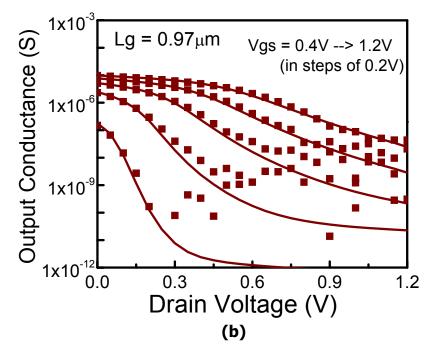

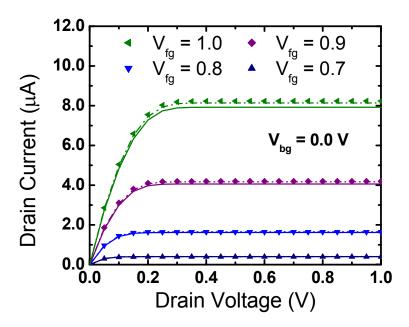

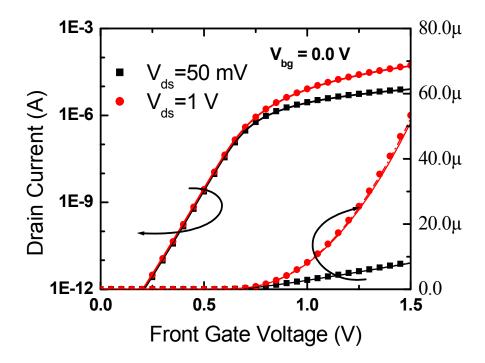

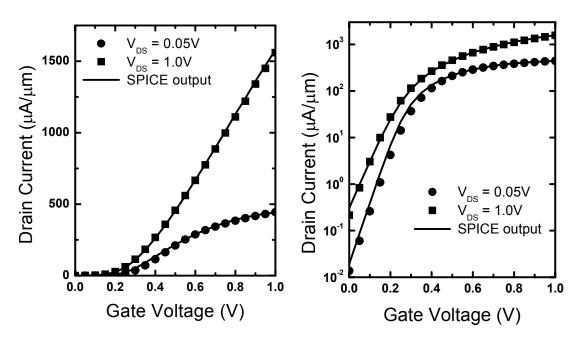

In Chapter 3, the core formulation and physical effects of real device modeled in BSIM-CMG (Berkeley Short-channel IGFET Model – Common Multi-Gate) are presented. The core model agrees with TCAD simulation very well without using any fitting parameter. The complete model is verified against experimental data for two different FinFET technologies – SOI FinFETs and bulk FinFETs.

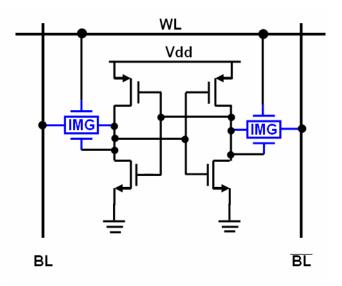

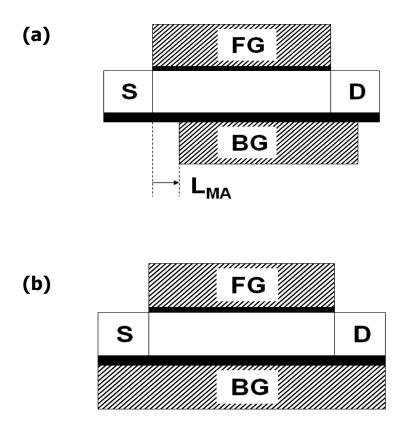

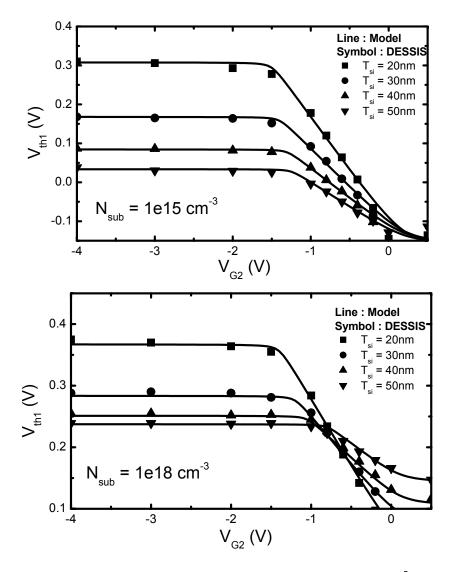

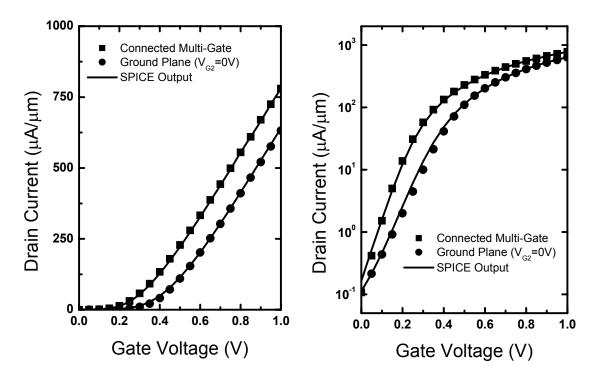

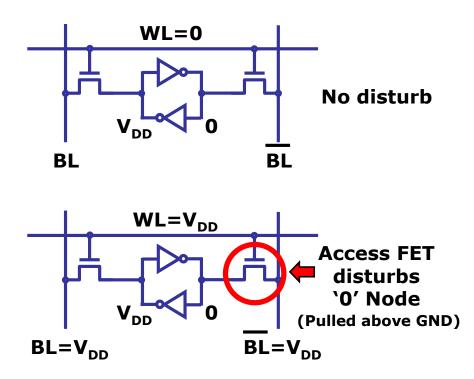

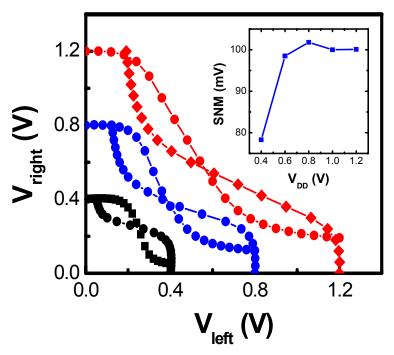

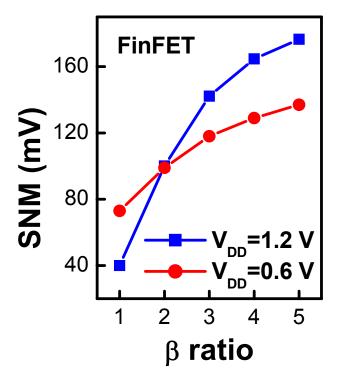

Compact model for the independent multi-gate device (BSIM-IMG, Berkeley Short-channel IGFET Model – Independent Multi-Gate) is introduced in Chapter 4. The model is used to study FinFET based SRAM cells and device variation tuning using back gate bias, highlighting its use for both circuit and technology development. The impact of back-gate length and misalignment of planar double-gate (DG) MOSFET on threshold voltage is also discussed.

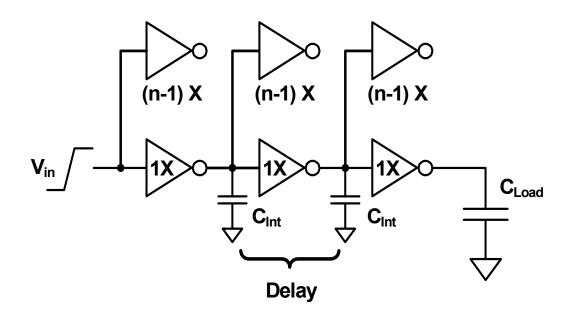

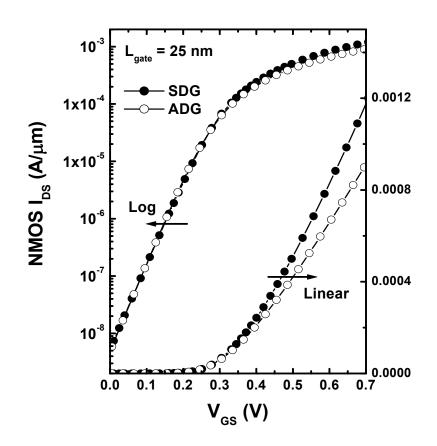

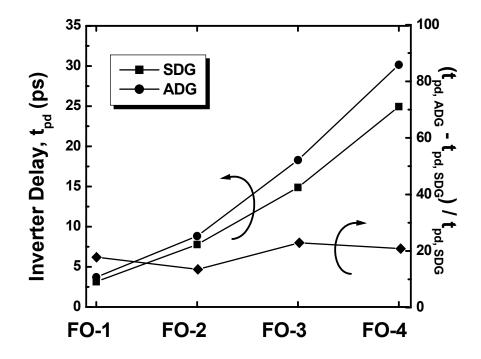

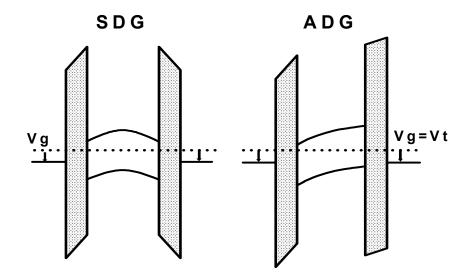

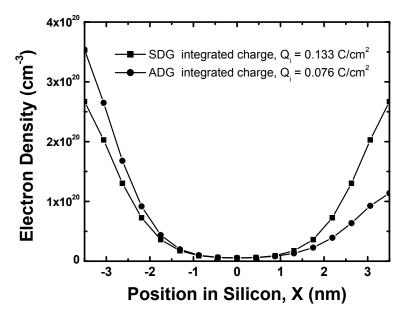

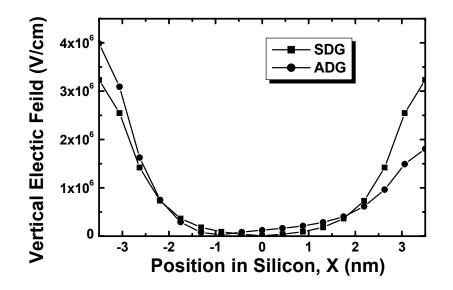

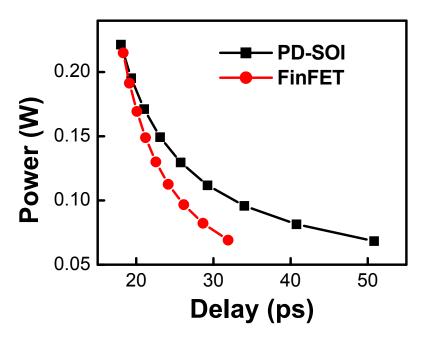

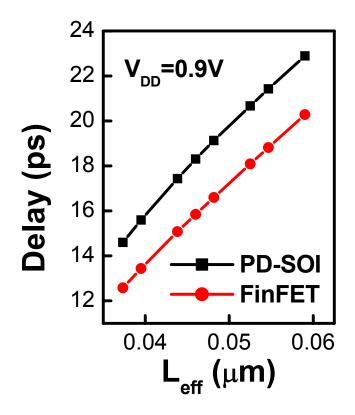

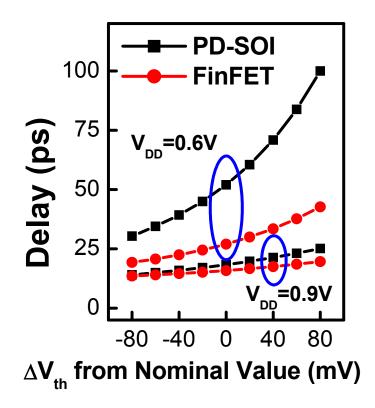

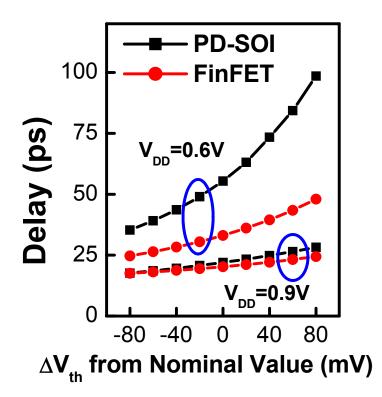

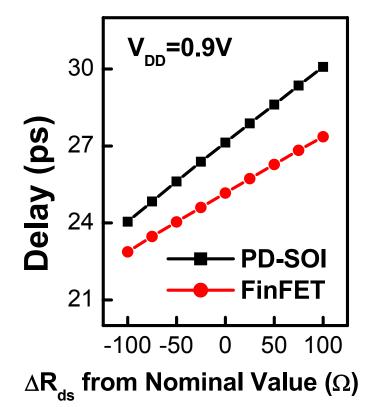

In Chapter 5, the circuit design issues and concepts of MG-based circuits are discussed. The circuit design trade-off of two main types of DG MOSFETs: (i) the symmetric/common DG (SDG) and (ii) the asymmetric/independent DG (ADG) are discussed. The performance of FinFET technology in digital circuit applications is studied compared to the planar SOI technology under various device parameter variations.

A novel methodology for generating Performance Aware (Corner/Distribution) Models (PAM) cards is presented in Chapter 6. More accurate and application-specific (for speed, power, gain, etc) model cards can be easily generated at any distribution levels (such as  $+2\sigma$ ,  $-1\sigma$ ). The accuracy improvement of generated PAM cards is demonstrated by applying it to different scale of logic circuits. The PAM cards also improve the accuracy of Monte Carlo simulation by reconciling the physical and electrical-test (ET) variances.

An overall summary of this dissertation is presented in Chapter 7. Key research contributions and suggestions for future research direction are highlighted.

## **1.6 References**

- [1.1] J. S. Kilby, "Miniaturized electronic circuits," U.S. Patent #3,138,743, issued June 23, 1964.

- [1.2] G. E. Moore, "Cramming more components onto integrated circuits," Electronics, vol. 38, pp. 114–117, 1965.

- [1.3] G. E. Moore, "Progress in digital integrated electronics," IEDM Tech. Dig., Dec. 1975, pp. 11-13.

- [1.4] R. H. Dennard, F. H. Gaensslen, H. N. Yu, V. L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions," IEEE J. Solid-State Circuits, vol. 9, pp. 256-268, 1974.

- [1.5] J. R. Brews, W. Fichtner, E. H. Nicollian, and S. M. Sze, "Generalized Guide for MOSFET Miniaturization," IEEE Electron Device Lett., vol. 1, pp. 2-4, 1980.

- [1.6] S.-H. Lo, D. A. Buchanan, Y. Taur, and W. Wang, "Quantum-Mechanical Modeling of Electron Tunneling Current from the Inversion Layer of Ultra-Thin-Oxide nMOSFET's," IEEE Electron Device Lett., vol. 18, no. 5, 209-211, 1997.

- [1.7] T. Tanaka, T. Usuki, T. Futatsugi, Y. Momiyama, and T. Sugii, "Vth Fluctuation Induced by Statistical Variation of Pocket Dopant Profile," IEEE International Electron Devices Meeting, pp. 271-274, 2000.

- [1.8] A. Hokazono, K. Ohuchi, M. Takayanagi, Y. Watanabe, S. Magoshi, Y. Kato, T. Shimizu, S. Mori, H. Oguma, T. Sasaki, H. Yoshimura, K. Miyano, N. Yasutake, H. Suto, K. Adachi, H. Fukui, T. Watanabe, N. Tamaoki, Y. Toyoshima, and H. Ishiuchi, "14nm Gate Length CMOSFETs utilizing Low Thermal Budget Process

with Poly-SiGe and Ni Salicide," IEEE International Electron Devices Meeting, pp. 639-642, 2002.

- [1.9] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, and M. Bohr, "A 90nm High Volume Manufacturing Logic Technology Featuring Novel 45nm Gate Length Strained Silicon CMOS Transistors," IEEE International Electron Devices Meeting, pp. 978-980, 2003.

- [1.10] Robert Chau, Suman Datta, Mark Doczy, Brian Doyle, Jack Kavalieros, and Matthew Metz, "High-K/Metal Gate Stack and Its MOSFET Characteristics," IEEE Electron Device Lett., vol. 25, no.6, pp.408-410, 2004

- [1.11] L. Chang, Y.-K. Choi, J. Kedzierski, N. Lindert, P. Xuan, J. Bokor, C. Hu, and T.-J. King, "Moore's Law Lives On: Ultra-Thin Body SOI and FinFET CMOS Transistors Look to Continue Moore's Law for Many Years to Come," IEEE Circuits and Devices Magazine, vol. 19, iss. 1, January 2003, pp. 35-42.

- [1.12] D.J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur and H.-S.P. Wong,

"Device Scaling Limits of Si MOSFETs and Their Application Dependencies,"

Proceedings of IEEE, vol. 89, pp. 259-288, March 2001.

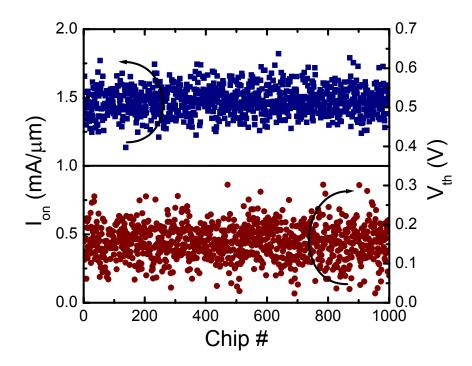

- [1.13] D. Hisamoto, Wen-Chin Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, Tsu-Jae King, J. Bokor and Chenming Hu, "FinFET A Self-Aligned Double Gate MOSFET Scalable to 20nm," IEEE Trans. Electron Devices, vol. 47, pp. 2320-2325, Dec. 2000.

- [1.14] M. Dunga, Ph.D. Dissertation, University of California at Berkeley, Fall 2007.

# Chapter 2

# Modeling of Physical Effects in Multi-Gate MOSFETs

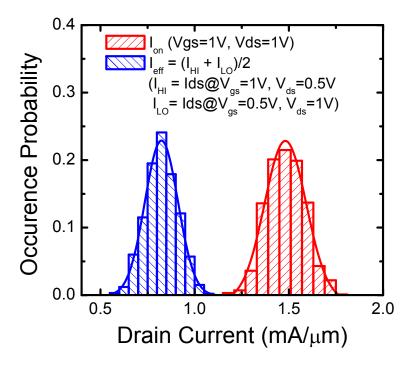

### 2.1 Motivation

The continuous evolution and enhancement of bulk CMOS technology has fueled the growth of the microelectronics industry for the past several decades. When we reach the end of the technology roadmap for the classical CMOS, multi-gate CMOS structures will take up the baton. The multi-gate structure can be scaled to the shortest channel length for a given oxide thickness due to the enhanced electrostatic control from the multiple gates. It is thus necessary to develop a compact model of multi-gate MOSFETs for technology/circuits development in the short term and for product design in the longer term.

There are several important unique device physics in the multi-gate MOSFET due to extra gates from sidewall. The prediction and completion of a compact model relies on the inclusion of these unique device physics in the model with appropriate flexibility. In this chapter, the quantum mechanical effects, short channel effects, and corner effects in the multi-gate MOSFET are studied. Modeling methodologies and approaches are proposed to incorporate these unique multi-gate physics in the compact model.

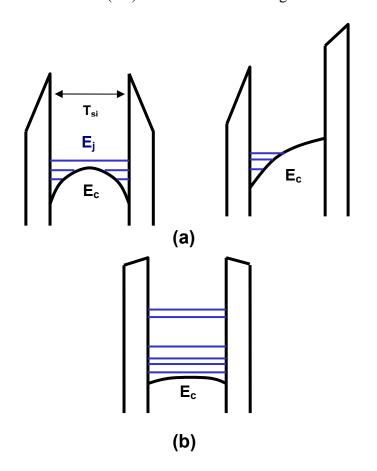

The quantum effect is already important in advanced planar single gate transistors. In the multi-gate devices, the additional confinement of the thin body makes the quantum effect an indispensable part of the model. Several quantum model approaches for the common double-gate structures are available in the literature. However, these approaches are limited to the carrier distribution and electrostatic potential profile, but not extended to device characteristics, such as I-V and C-V. In section 2.2, we developed an accurate quantum mechanical compact model for multi-gate MOSFET. Both V<sub>th</sub> shift in the subthreshold and strong inversion regions and gate capacitance degradation in the strong inversion region due to QM are corrected simultaneously. The model can predict the complicated QM effect dependence on various device parameters.

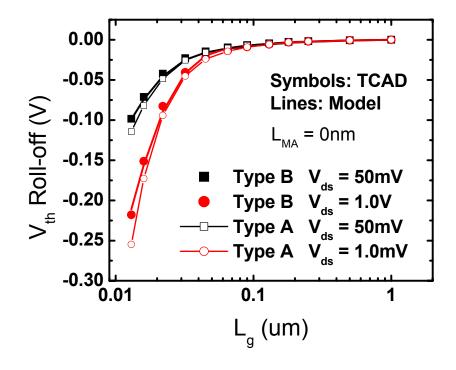

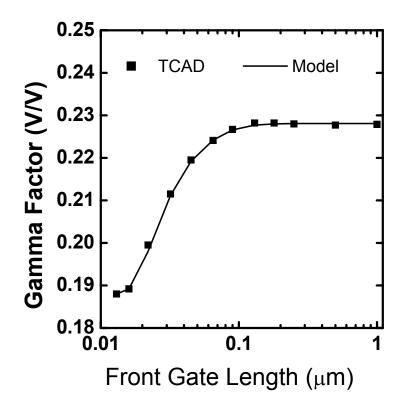

The multi-gate structure has better short channel behaviors due to enhanced electrostatic control from the multiple gates. Critical geometry parameters which determine device short-channel behaviors include gate length, fin thickness, fin height, oxide thickness, and channel doping. It is very important to include all these parameters in the short channel model to give correct scalability over a wide range of device parameters. In section 2.3, the short channel model is developed based on the quasi 2-D potential profile in the conduction channel. The degree of SCE (V<sub>th</sub> roll-off, drain-induced-barrier-lowering (DIBL), and subthreshold slope degradation) depends on strength of gate control which is modeled by a characteristic field penetration length ( $\lambda =$ f(T<sub>ox</sub>, T<sub>si</sub>)) derived from quasi 2-D Poisson's equation. The SCE model shows excellent agreements with 2-D TCAD simulation results without the use of any fitting parameters. The SCE model implementation captures V<sub>th</sub> roll-off, DIBL and subthreshold slope degradation for short channel multi-gate FETs simultaneously.

The corner effect is important for extending the double-gate model to cover triple gate (and all-around gate) structures. These effects are known to dominate the subthreshold and weak inversion current. Therefore accuracy is of paramount importance. The corner effect is studied using the 3-D TCAD device simulation. Section 2.4 shows the proposed modeling methodology by introducing the "cap" transistor.

## **2.2 Quantum Mechanical Effects**

Carrier energy quantization has become significant in the state-of-the-art MOSFETs due to increased vertical E-field. The energy quantization and the shift of the inversion charge centroid will delay the formation of inversion charge (threshold voltage (V<sub>th</sub>) shift) and reduce the current driving capability (increase the effective oxide thickness). The quantization effect is more complicated in double-gate (DG) MOSFETs than in bulk MOSFETs due to the extra structural confinement by the body thickness  $(T_{si})$ . The quantum mechanical (QM) effect has been included in the compact models by introducing the effective oxide thickness for a bias-dependent reduction of the gate capacitance, and bias-independent correction for the V<sub>th</sub> shift, separately [2.1]. However, the lack of predictivity of this approach is particularly undesirable for the DG MOSFETs compact model since less DG MOSFETs Si data are available than single-gate MOSFETs. Several groups have investigated the influence of T<sub>si</sub> on the quantized carrier distribution and threshold voltage shift numerically [2.2] and analytically [2.3-2.5] in DG MOSFETs. However, these approaches are limited to the carrier distribution and electrostatic potential profile, but not extended to device characteristics, such as I-V and C-V.

While the channel carriers are confined in one-dimension, the subband splitting due to the field-induced electrical confinement (EC, Fig. 2.1(a)) has significant impact on device

characteristics. The energy quantization is more complicated in the DG MOSFETs due to the extra structural confinement (SC) in the subthreshold region as shown in Fig. 2.1(b).

Fig. 2.1 Energy-band diagrams of DG-MOSFET under different operation modes illustrate two mechanisms of carrier energy quantization in DG MOSFETs: (a) electrical confinement (EC); (b) structural confinement (SC).

The quantum confinement in DG MOSFETs is affected by the gate work function, gate insulator dielectric thickness, body thickness, substrate doping, and gate bias. In order to study these complicated device parameter dependences of QM effects, a self-consistent 1-D Schrödinger solver, SCHRED 2.1, is used for simulating QM effects in DG structure

[2.6].

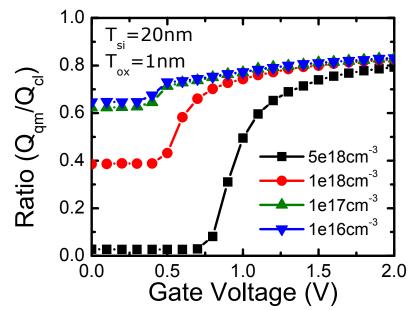

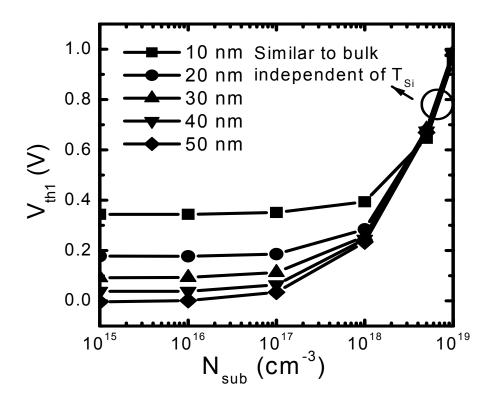

Fig. 2.2 shows the simulation results of the ratio of QM-corrected and classical charge density over different substrate doping concentrations for n-type DG MOSFETs.

Fig. 2.2 The doping concentration dependence of QM effects. QM effects is very significant in heavily-doped device due to larger vertical E-field.

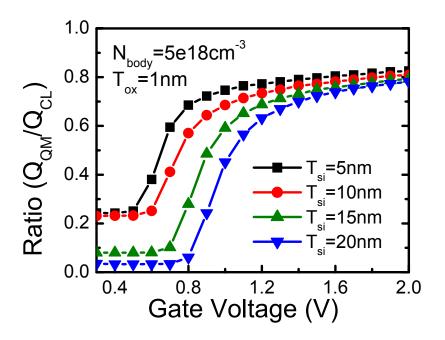

In the subthreshold region, the ratio of charge reflects the V<sub>th</sub> shift, while in the strong inversion region, the ratio of charge indicates the amount of the gate capacitance degradation. In the lightly doped or undoped DG MOSFETs, QM effect is less significant due to weaker EC (smaller E-field). The SC is weak in this structure due to relatively thick  $T_{si}$ . The dependence of body thickness on QM effect is shown in Fig. 2.3. The QM effect is less significant in the heavily doped thinner body device ( $T_{si}$ =5nm) due to weaker EC (electrical coupling from two gates).

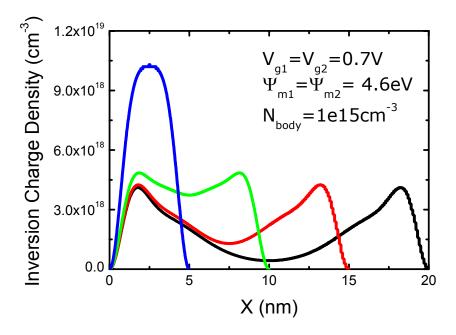

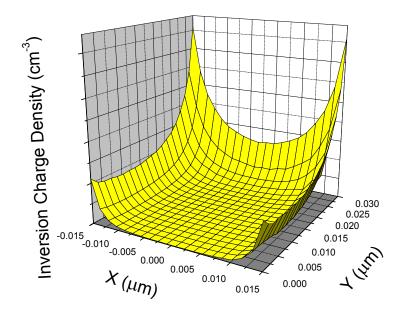

Fig. 2.4 shows the inversion carrier distribution vs. the body thickness at the strong inversion region in the symmetric DG MOSFETs. The body doping is  $10^{15}$ cm<sup>-3</sup> and the midgap workfunction is used in the simulation. The DG MOSFETs exhibit a more uniform inversion carrier density when the body thickness is scaling down (T<sub>si</sub>=5nm). The two finite charge centroids overlap so strongly that the maximum of the inversion carrier concentration is located in the middle of the body film. The inversion carriers travel away from the oxide/Si interface. Note that the mobility characteristics also change since there is less surface roughness scattering experienced by the inversion carriers. The effective mobility in the DG MOSFETs is affected by the average position of the inversion carrier can be expressed as

$$X_{dc} = \frac{\int_{0}^{T_{Si/2}} xn(x) \cdot dx}{\int_{0}^{T_{Si/2}} n(x) \cdot dx}$$

(2.1)

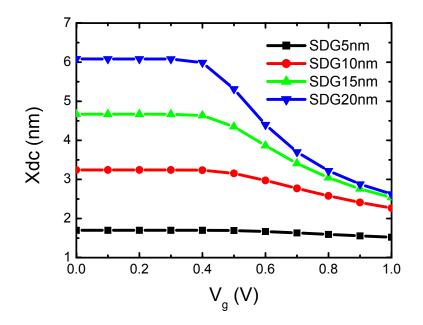

Fig. 2.5 shows the extracted  $X_{dc}$  vs. gate bias for the devices with different body thickness. The  $X_{dc}$  is clamped at ~1/3 body thickness in the subthreshold region due to the strong overlap of the two finite charge centroids. The  $X_{dc}$  decreases as the gate bias increases due to stronger vertical electric field.

Fig. 2.3 The body thickness dependence of QM effects. QM effects is weak in the heavily doped thinner body device due to smaller vertical E-field.

Fig. 2.4 Impact of the body thickness on the inversion carrier concentration distribution for a given fixed gate bias.

Fig. 2.5 The extracted charge centroids of the symmetric DG-MOSFETs with different body thickness.

Conventional compact models handle QM correction by introducing the effective oxide thickness for a bias-dependent reduction of the gate capacitance, and bias-independent correction for the  $V_{th}$  shift, separately [2.1]. The charge centroid theory gives the universal bias-dependent reduction of the gate capacitance and has been verified by the self-consistent Schrödinger solver.

We have developed a surface-potential based multiple-gate MOSFET compact model, where the surface potential is solved by Poisson's equation and Gauss's law [2.7]. A bias-dependent ground-state subband energy in the unprimed valley ( $E_0$ ) is added in the surface potential calculation. Trivedi et al. have calculated the  $E_0$  using the vibrational approach to include both structural and electrical confinement in DG MOSFETs [2.4]. However, the model only considers the threshold voltage shift in intrinsic undoped body device. A modification was made for  $E_0$  calculation to extend the model to strong inversion region with the finite doped body. Drift-diffusion equation is then employed to obtain a model for drain current in terms of surface potential. The V<sub>th</sub> shift and gate capacitance degradation are inherently captured without the need of any explicit individual modifications as long as the surface potential is modeled correctly.

In the new surface potential calculation, a QM correction term ( $\Delta \psi_{QM}$ ) is added in the inversion carrier term when solving Poisson's equation.

$$V_{g} = V_{fb} + \phi_{s} + \frac{\varepsilon_{si}}{C_{ox}}$$

$$\cdot \sqrt{\frac{2qn_{i}}{\varepsilon_{si}} \cdot \left(\frac{e^{\frac{q(\phi_{s} - \Delta\psi_{QM})}{kT}} - e^{\frac{q(\phi_{0} - \Delta\psi_{QM})}{kT}}}{q/kT} \cdot e^{\frac{-q\varphi_{B}}{kT}} \cdot e^{\frac{-q\varphi_{B}}{kT}} + e^{\frac{q\varphi_{B}}{kT}} \cdot \left(\phi_{s} - \phi_{0}\right)\right)}$$

(2.2)

where  $\Delta \psi_{QM} = E_0/q$ .  $E_0$  is the ground state subband energy obtained by solving Schrödinger equation via the vibrational approach [2.4]

$$E_0 \approx \frac{\hbar^2}{2m_x} \left[ \left(\frac{\pi}{T_{si}}\right)^2 + b_0^2 \left(3 - \frac{4}{3} \frac{1}{\left[\left(\frac{b_0 T_{si}}{\pi}\right)^2 + 1\right]}\right) \right]$$

(2.3)

$b_0$  represents the vertical electric field dependence. Both structural and electrical confinements are included in the ground state subband energy. The first term of the right hand side represents the structural confinement. The thinner the body thickness is, the higher ground state subband energy. The second term of the right hand side represents the structural confinement. The boy the structural electrical electrical field, which is expressed as

$$b_0 \approx \sqrt[3]{\frac{3}{4} \frac{2m_x qE_x}{\hbar^2}}$$

(2.4)

where  $E_x$  is the vertical field calculated from the surface potential. Note that the vertical field is accurate from subthreshold region to strong inversion region, consequently the QM correction is accurate for all regions of the operations

$$E_x = \frac{V_{gs} - V_{fb} - \phi_s}{\varepsilon_{Si} / \varepsilon_{ox} \cdot T_{ox}}.$$

(2.5)

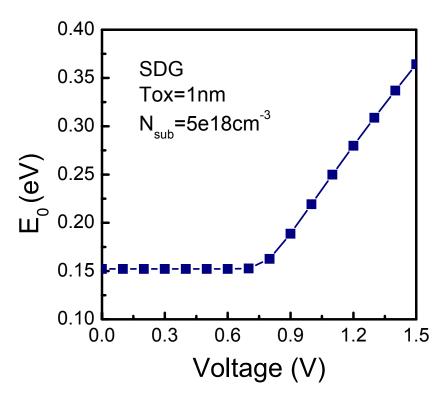

Fig. 2.6 shows the ground state subband energy vs. gate bias in the symmetric/ common double-gate MOSFET obtained from Eq. (2.3). The ground state subband energy is constant in the subthreshold region due the constant  $E_x$  in the subthreshold region in SDG. However, the ground state subband energy increases as gate bias increases in the strong inversion region. The bias-dependent correction of ground state subband energy accurately predicts the constant  $V_{th}$  shift in the subthreshold region and bias-dependent  $V_{th}$  shift (gate capacitance degradation) in the strong inversion region.

Fig. 2.6 The predicted ground state subband energy in the SDG MOSFET. The  $E_0$  is constant in the subthreshold region and increases as gate bias increases.

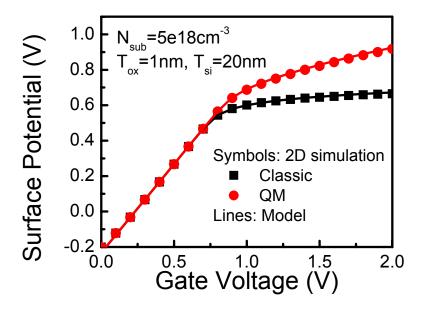

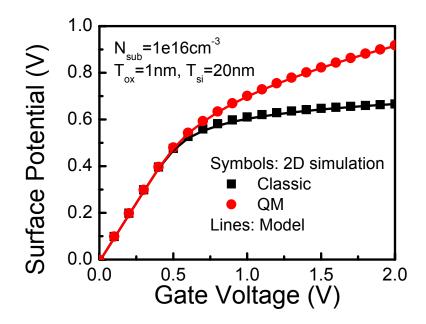

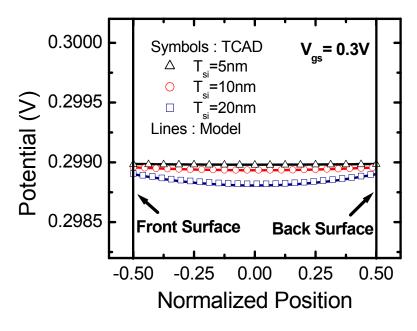

Fig. 2.7 shows the surface potential versus  $V_g$  for a long channel n-type DG MOSFET where source/drain is grounded. A uniformly doped body (5×10<sup>18</sup>cm<sup>-3</sup>) is assumed. The model matches 2-D device simulation very well from subthreshold region to strong inversion region. The increase of the surface potential due to the QM effect is well predicted by the model. Larger surface potential is needed to achieve the same level of inversion. The model can accurately predict surface potential over a wide range of body doping concentration as shown in Fig. 2.8 (10<sup>16</sup>cm<sup>-3</sup>).

Fig. 2.7 QM-corrected surface potential solution matches 2-D simulation well. The QM-induced  $V_{th}$  shift in subthreshold region and  $C_{ox}$  degradation in strong inversion region are simultaneously predicted as long as QM-corrected surface potential is accurate

Fig. 2.8 Surface potential vs. gate voltage for undoped body device. Model can accurately predict the doping dependence.

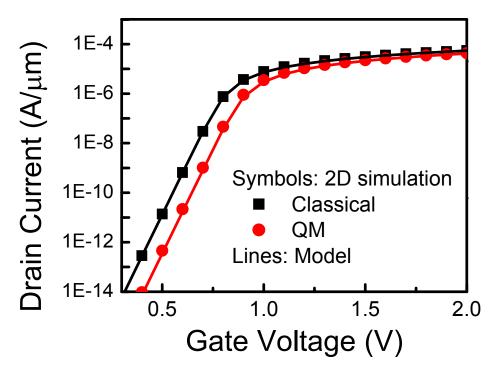

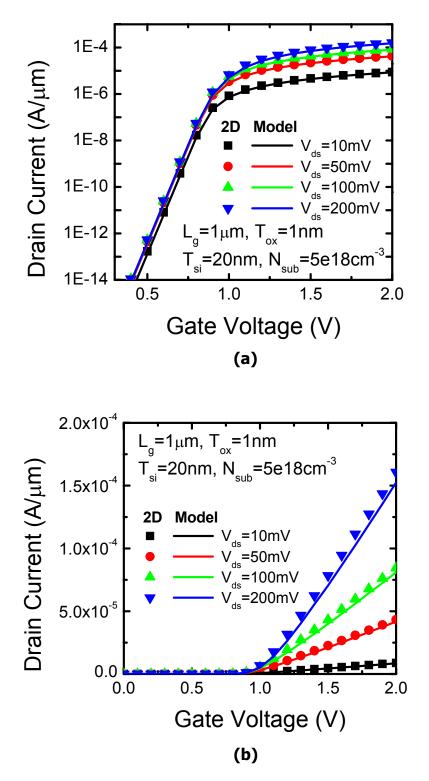

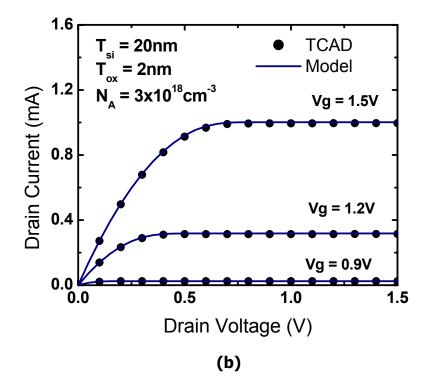

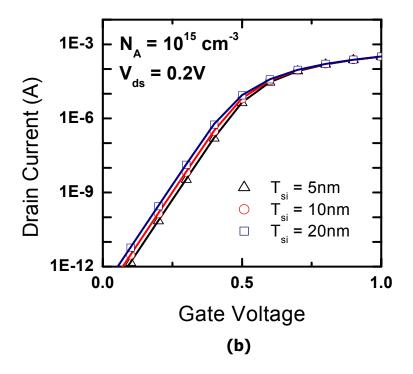

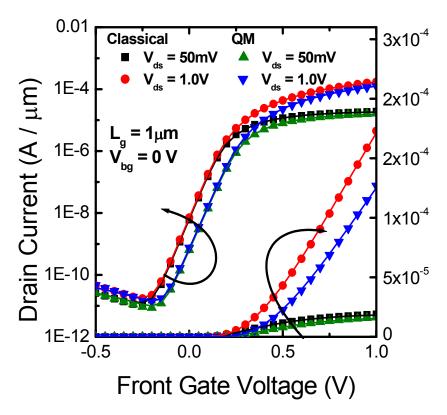

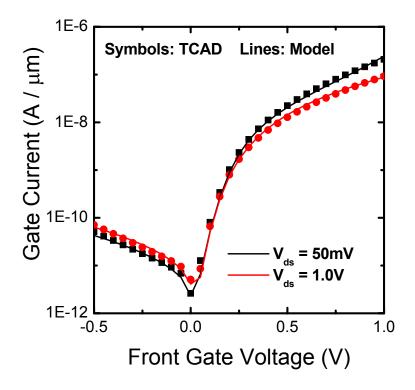

The Drift-diffusion equation is then employed to obtain a model for drain current in terms of QM-corrected surface potential. TAURUS 2-D device simulations are used to verify the QM model. Fig. 2.9 shows the I<sub>d</sub>-V<sub>g</sub> characteristics of the n-type symmetrical/common-gate DG MOSFET for both classical and QM models. The drain is biased in linear region (V<sub>ds</sub>=50mV). The oxide thickness of 1nm and midgap work-function gate material are used in simulation. The substrate doping is  $5 \times 10^{18}$  cm<sup>-3</sup>. The QM model predicts the V<sub>th</sub> shift accurately compared to the 2-D device simulation results. The model can predict V<sub>ds</sub> dependence accurately as shown in Fig. 2.10.

Fig. 2.9 The classical and QM-corrected  $I_d$ -V<sub>g</sub> characteristics for n-typed symmetrical/common-gate DG MOSFET.

Fig. 2.10 The QM-corrected drain current model predicts  $V_{ds}$  dependence of  $I_d$ - $V_g$  characteristics well, shown in (a) log scale and (b) linear scale.

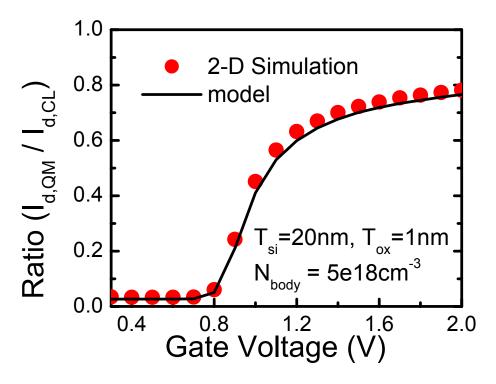

The ratio of QM-corrected and classical drain current is shown in Fig. 2.11. The ratio in the subthreshold region reflects the effect of the  $V_{th}$  shift. The ratio in the strong inversion region is mainly caused by the gate capacitance degradation due to finite charge centroid. It clearly shows that the QM model predicts both the  $V_{th}$  shift and gate capacitance degradation without introducing the definition of an effective oxide thickness. The model predicts QM effects accurately in all regimes of operation since the QM-corrected surface potential is modeled accurately against the QM simulation.

Fig. 2.11 The ratio of QM-corrected and classical drain current. The model captures the threshold voltage shift and gate capacitance degradation simultaneously through accurate surface potential calculation.

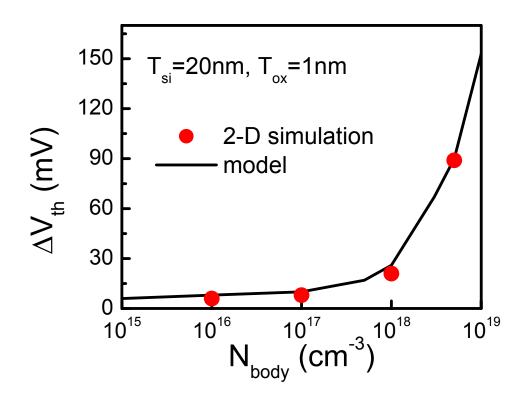

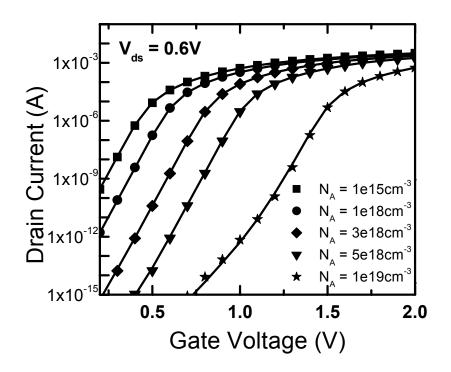

The predictivity of model is important for MG technology and circuits development since less Si data is available compared to single-gate MOSFETs. The QM model can predict the complicated QM effect dependences on various device parameters, such as  $N_{body}$ ,  $T_{si}$ ,  $T_{ox}$ , etc. Fig. 2.12 shows that the predicted  $V_{th}$  shift over a wide range of body doping concentration matches the 2-D simulation results very well. EC dominates in higher doping concentration region, while SC dominates in lower doping concentration region.

Fig. 2.12  $V_{th}$  shift can be modeled accurately over a wide range of body doping. EC dominates in higher doping region, while SC dominates in lower doping region.

### **2.3 Short Channel Effects**

Short channel effects (SCE) such as drain-induced barrier lowering (DIBL), threshold voltage ( $V_{th}$ ) roll-off and sub-threshold slope degradation are modeled. SCE are essentially 2-D effects where the drain significantly affects the potential barrier at the source due to its close proximity to the source region in a short channel transistor. A good SCE must be scalable over a wide range of the device parameters such as gate length L, gate insulator thickness  $T_{ox}$ , fin thickness  $T_{fin}$ , fin height H<sub>fin</sub> and channel doping N<sub>A</sub>.

There have been numerous efforts in the past to model the SCE in DG-FETs. Invariably all the methods to model SCE solve the 2-D Poisson's equation in sub-threshold region inside the silicon body with varying degree of simplifying assumptions [2.8-2.11]. In [2.8] the authors solve the complete 2-D boundary value problem by expressing the potential through a infinite sum of sin functions. The solution is numerically complex and will be hard to extend to the case of multi-gate FETs with triple or quadruple gates. In [2.9] the authors first solve a 1-D Poisson equation in the channel length direction and then solve the 2-D Poisson equation. The solution in this case is independent of  $V_{ds}$  and hence modeling DIBL is a challenge in this approach. Another approach assumes a parabolic potential function perpendicular to the silicon-insulator interface and solves the 2-D Poisson's equation [2.10-2.11]. This

approach maintains a balance between the model accuracy and model computation time and hence is used to develop a SCE model for DG-FETs.

The SCE is determined by minimum potential barrier ( $\psi_{c(min)}$ ) seen by the carrier entering at the source end. In the DG-FET, the minimum potential barrier height is located at the center plane of the body. By using the parabolic potential assumption [2.12], the  $\psi_{c(min)}$  is derived as

$$\psi_{c}\left(\min\right) = V_{SL} - \frac{V_{ds}^{2} \cdot e^{-L/2\lambda}}{\left(e^{L/\lambda} - e^{-L/\lambda}\right)\sqrt{Z_{0}Z_{L}}} + 2\sqrt{Z_{0}Z_{L}} \frac{\sinh\left(L/2\lambda\right)}{\sinh\left(L/\lambda\right)}$$

(2.6)

where  $V_{SL}$  is equivalent to the center potential for a long channel transistor

$$V_{SL} = V_{gs} - V_{fb} - \frac{qN_A}{\varepsilon_{Si}} \lambda^2$$

(2.7)

where  $\lambda$  is a characteristic field penetration length defined as

$$\lambda = \sqrt{\frac{\varepsilon_{Si}}{2\varepsilon_{ox}}} \cdot \left(1 + \frac{\varepsilon_{ox}T_{si}}{4\varepsilon_{Si}T_{ox}}\right) \cdot T_{si} \cdot T_{ox}}$$

(2.8)

where  $Z_0 = V_{bi} - V_{SL}$ ,  $Z_L = V_{bi} - V_{SL} + V_{ds}$  and  $V_{bi}$  the built-in potential at the source end. For a long channel transistor,  $\psi_{c(min)} \sim V_{SL}$ .

The compact model is traditionally developed in a long channel framework. To obtain the correct minimum barrier height for a short channel DG-FET at a certain  $V_{gs}$  using the long channel surface potential model, one can use the long channel surface potential model with an effective  $V'_{gs}$  where

$$V'_{gs} = V_{gs} + \psi_{c(\min)} - V_{SL}$$

(2.9)

This method can be easily implemented into any compact model by replacing  $V_{gs}$  with effective  $\dot{V_{gs}}$ . Note that the SCE model in Eq. (2.9) not only captures the  $V_{th}$  roll-off and DIBL but also captures the degradation of subthreshold slope simultaneously since the correction term is a function of gate voltage.

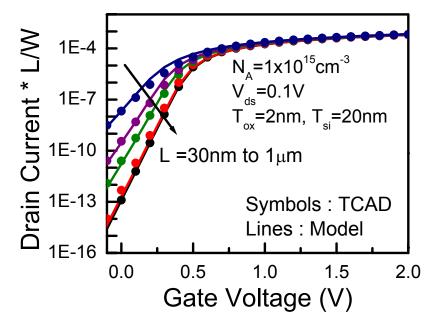

The SCE model is verified against 2-D TCAD simulations. Drain current is calculated using the SCE and I-V model for a wide range of channel lengths ranging from a long channel L = 1 $\mu$ m DG-FET to a short channel DG-FET of L = 30nm. Fig. 2.13 shows the normalized I<sub>ds</sub> (I<sub>ds</sub>×L/W) calculated from the model against the current obtained from 2-D TCAD simulations. Good agreement in the SCE behavior such as V<sub>th</sub> roll-off and subthreshold slope degradation is observed between the model and 2-D TCAD.

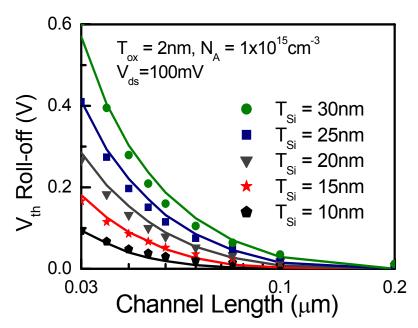

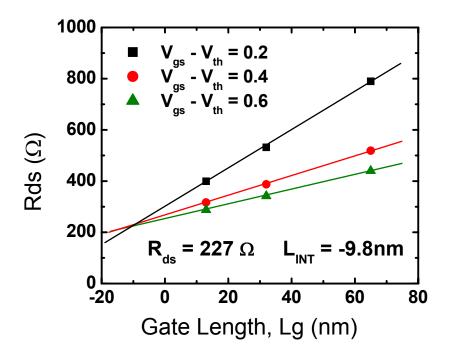

Good scalability of the SCE model is highly desirable. A scalable model allows one to stretch the limited available silicon data to perform technology projections. The scalability of the SCE model is examined extensively with respect to physical parameters such as L,  $T_{Si}$  and  $T_{ox}$ . Fig. 2.14 shows the  $V_{th}$  roll-off extracted from the model and 2-D TCAD for different  $T_{Si}$ . As expected, DG-FETs with smaller  $T_{Si}$  have smaller drain field penetration and hence the model predicts smaller  $V_{th}$  roll-off for thinner  $T_{Si}$ .

Fig. 2.13 Normalized drain current for DG-FETs with different channel lengths, from  $L = 1\mu m$  down to L = 30nm. All the important SCE are captured by the model and agree well with 2-D TCAD simulations.

Fig. 2.14 Threshold voltage roll-off of DG-FETs for different  $T_{Si}$ . Model (lines) demonstrates excellent scalability when compared against 2-D TCAD simulations (symbols).

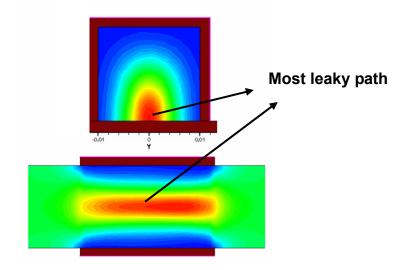

Thus far, only DG-FETs, i.e. multi-gate FETs with gate electrodes only on two opposite sides of Si body, have been analyzed. Multi-gate FETs can have three or four gate electrodes to further improve the electrostatic control. In multi-gate FETs with three or more gates, the physical location of the minimum potential barrier (or the path for maximum drain leakage current) is different from DG-FET. The extra electrostatic control from vertical ends (top gate or bottom gate) reduces the short channel effect. The V<sub>th</sub> roll-off decreases as fin height (H<sub>fin</sub>) decreases. The most leaky channel path is located at the center bottom of the fin where the electrostatic control from the gate is the weakest as shown in Fig. 2.15. The potential barrier at this most leaky path decreases as fin height increases, resulting in an H<sub>fin</sub> dependence of short channel effects.

Fig. 2.15 Leakage current path is different in triple-gate FETs due to 3D effects. The most leaky path located at the bottom center of the fin.

Pei et al. has proposed a 3-D analytical electrostatic potential based on the solution of 3-D Laplace's equation in subthreshold region to predict the short channel behavior of FinFET [2.13]. In Eq. (2.9), the DG-FET short channel effects are modeled by a characteristic field penetration length. To model the fin height dependence on short channel effects, a new characteristic field penetration length  $\lambda_{Hfin}$  is introduced.

$$\lambda_{Hfin} = \sqrt{\frac{\varepsilon_{Si}}{4\varepsilon_{ox}} \cdot \left(1 + \frac{\varepsilon_{ox}H_{fin}}{2\varepsilon_{Si}T_{ox}}\right) \cdot H_{fin} \cdot T_{ox}}$$

(2.10)

The new effective characteristic length used in the short channel model is defined to include the effect of fin height

$$\lambda_{eff} = \frac{1}{\sqrt{\left(\frac{1}{\lambda}\right)^2 + \left(\frac{a}{\lambda_{Hfin}}\right)^2}}$$

(2.11)

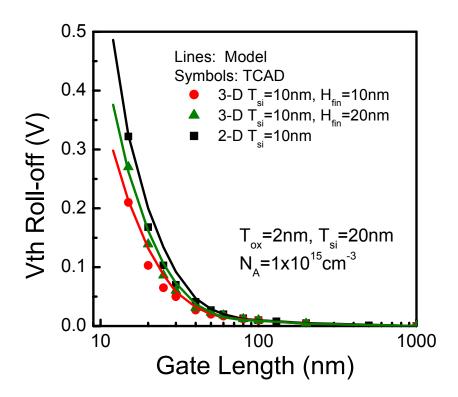

where a = 0 for DG-FET, a = 0.5 for triple-gate FinFET, a = 1 for surrounding-gate FinFET. Note that in the case of triple-gate FET, one can also use different oxide thickness in  $\lambda$  and  $\lambda_{Hfin}$  to model the thick SiO<sub>2</sub> layer (hard mask) on top of the fin. Fig. 2.16 shows the comparison of predicted V<sub>th</sub> roll-off between compact model and the TCAD simulations. Fin height dependence for the short channel effect is verified using 3-D TCAD simulation. The V<sub>th</sub> roll-off increases as fin height increases for a given fin thickness. The model agrees with the TCAD simulation results very well.

Fig. 2.16 SCE model exhibits fin height scalability for triple-gate FinFETs (symbols: 3-D TCAD, lines: model)

### 2.4 Corner Effects

In the multi-gate MOSFET, the triple-gate device exerts superior electrostatic control over the channel due to the presence of the top gate. However, the subthreshold swing and threshold behavior are different in the triple-gate device at the top corners. According to 3-D device simulations, the corner conduction (at top portion) will dominate the subthreshold leakage current if the channel doping is high. The corner effect can be suppressed with rounded corners, thin gate oxides, and lower channel doping [2.14-2.16]. To address the corner effect in the model, a new corner effect model is needed for the inversion charge calculation with threshold voltage modification.

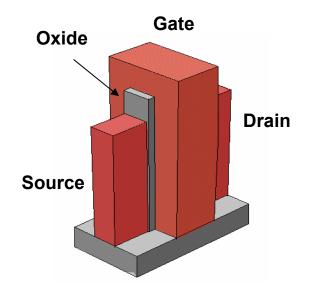

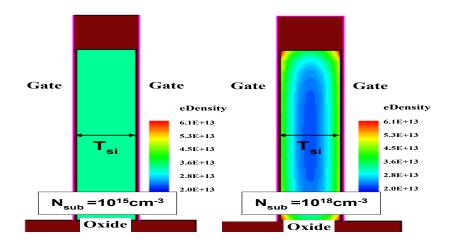

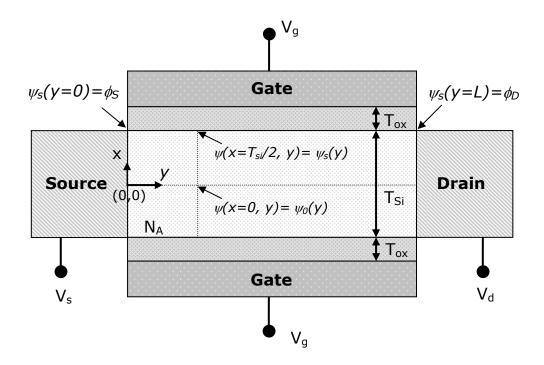

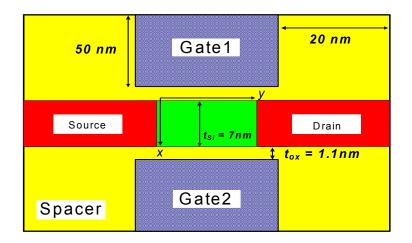

In order to calculate the inversion charge densities and potential in the silicon fin, the 3-D device simulation was carried out using DESSIS [2.17]. The simulation structure is shown in the Fig. 2.17. A set of devices with physical gate length 100 nm, various substrate doping levels ranging from  $10^{16}$  cm<sup>-3</sup> to  $10^{18}$  cm<sup>-3</sup>, a 1.1 nm thick gate oxide, 30 nm fin width, 30 nm and 60 nm fin height. We assume the mid-gap metal gate material. To study the corner effect, we investigate the 2-D cross section of the device in the center of the channel.

Fig. 2.17 3-D FinFET structure used for TCAD simulations

Fig. 2.18 shows the 2-D charge distribution in the 30nm×30nm fin cross section bias at subthreshold region. The substrate doping is 10<sup>18</sup>cm<sup>-3</sup>. Note that the inversion charge is built up significantly at the top corners of the silicon fin, which corresponds to a smaller threshold voltage of the top corner portion. Similar results are observed in the device with taller fin (60nm). To suppress the corner effect, lower substrate doping or rounded corner shape is required. Fig. 2.19 shows 2-D charge distribution of the FinFET with hard mask on top of the Si fin. The corner effect is suppressed in the device with lightly doped substrate. Note that even though there is hard mask on top of the channel, there is still significant inversion charge built in the top corner portion of the heavily doped device.

Fig. 2.18 2-D inversion charge distribution in the Si fin biased at subthreshold region.

Fig. 2.19 The electron density distribution from the 3-D ISE device simulator of  $L_g$ =100nm nFinFETs. Corner effect is suppressed in the lightly doped channel device (left).

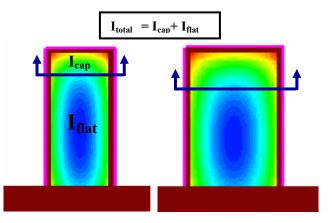

In order to model the corner effect, a "cap" transistor model is introduced. The height of cap transistor is half of the fin width independent of fin height, which can be explained by the charge sharing concept as shown in Fig. 2.20.

Fig. 2.20 2-D inversion charge distribution of three triple-gate MG-FETs with different fin thickness (same fin height). The height of cap transistor equals to half of fin width independent of fin height due to charge sharing by vertical and sidewall gates.

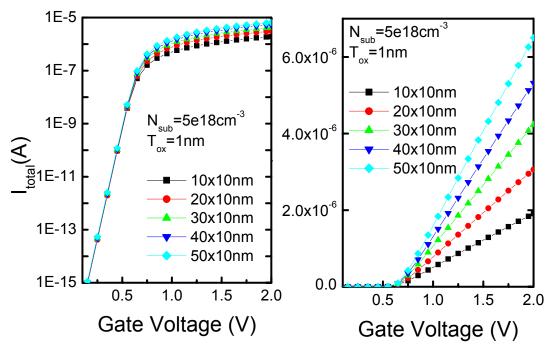

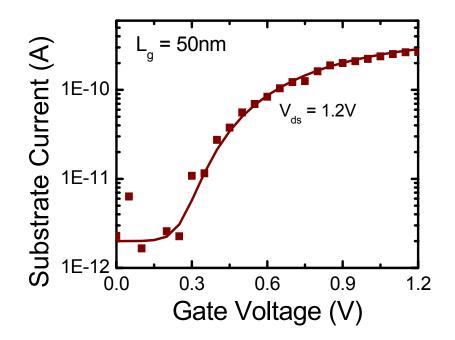

Therefore, the "cap" transistor can be extracted by test MG structures with different fin heights, but identical fin width. The lower threshold voltage, stronger level of inversion and process induced corner shape variations can be modeled by effective flat-band voltage shift, effective thinner oxide, and effective width using the same core DG model. Fig. 2.21 shows the I<sub>d</sub>-V<sub>g</sub> characteristics of test MG structures with different fin heights (10 to 50nm), but identical fin width (10nm). Note that the identical drain current in the subthreshold region indicates the "cap" transistor dominates the conduction current due to smaller threshold voltage (stronger electric field).

Fig. 2.21 The  $I_d$ -V<sub>g</sub> characteristics of different MG structures, shown in (a) log scale, (b) linear scale.

The "cap" transistor current is extracted by subtracting the current flow in the flat region from the total conduction current,

$$I_{cap} = I_{total} - 2 \times I_{flat} \cdot \left( H_{fin} - \frac{1}{2} T_{fin} \right).$$

(2.12)

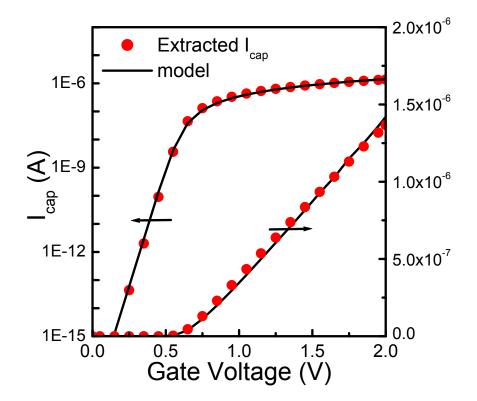

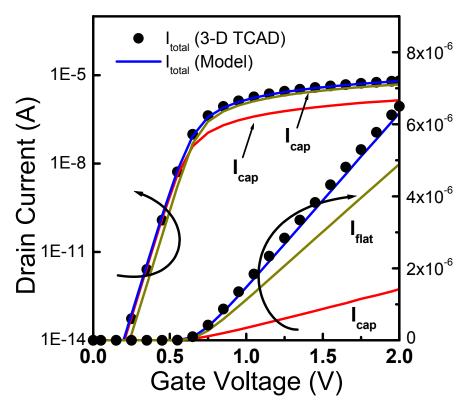

The I<sub>cap</sub> can be fitted by the flat core DG model with different parameters as shown in Fig. 2.22. The net drain current (cap + flat) of multi-gate FET (H<sub>fin</sub>=50nm and T<sub>fin</sub>=10nm) matches the 3-D simulation results well (Fig. 2.23). In the subthreshold region, the cap transistor dominates the drain current, while the current is determined by both the cap and flat transistors in the strong inversion region.

Fig. 2.22 Extracted Icap can be modeled by core DG equation with  $V_{fb}$  shift, thinner oxide thickness, and effective width.

Fig. 2.23 Net current of Icap and Iflat matches 3-D simulation well. The cap transistor dominates the subthreshold region due to lower  $V_{th}$ .

## 2.5 Summary

A bias-dependent QM correction for the surface potential of DG MOSFETs is developed for all regimes of operation. The QM-corrected surface potential agrees with the 2-D simulation results well. Both  $V_{th}$  shift in the subthreshold and strong inversion regions and gate capacitance degradation in the strong inversion region due to QM are corrected simultaneously. The model can predict the complicated QM effect dependence on various device parameters.

The degree of SCE (V<sub>th</sub> roll-off, drain-induced-barrier-lowering (DIBL), and subthreshold slope degradation) depends on strength of gate control which is modeled by a characteristic field penetration length ( $\lambda = f(T_{ox}, T_{si})$ ) derived from quasi 2-D Poisson's equation. The SCE model shows excellent agreements with 2-D TCAD simulation results without the use of any fitting parameters. Good scalability over  $T_{ox}$  and  $T_{si}$  down to 30nm channel length ( $L_g$ ) is clearly visible. The SCE model is extended for considering the triple or more gates structures by making  $\lambda = f(T_{ox}, T_{si}, H_{fin})$ . The SCE model implementation captures V<sub>th</sub> roll-off, DIBL and subthreshold slope degradation for short channel multi-gate FETs simultaneously.

According to 3-D device simulations, the corner conduction (at top portion) dominates the subthreshold leakage current if the channel doping is high. The corner effect can be suppressed with rounded corners, thin gate oxides, and lower channel doping. In order to model the corner effect, a cap transistor model is introduced. The height of cap transistor is half of the fin width independent of fin height, which can be explained by the charge sharing concept.

### **2.6 References**

- [2.1] Y. King, H. Fujioka, S. Kamohara, K. Chen, and C. Hu, "DC Electrical Oxide Thickness model for Quantization of the inversion layer in MOSFETs," Semicond. Sci. Technol., 13, p. 963 (1998).

- [2.2] B. Majkusiak, T. Janik, and J. Walczak, "Semiconductor Thickness Effects in the Double-Gate SOI MOSFET," Tran. Electron Devices, 45, p.1127 (1998).

- [2.3] L. Ge, and J. Fossum, "Analytical modeling of quantization and volume inversion in thinSi-film DG MOSFETs," Tran. Electron Devices, 49, p.287 (2002).

- [2.4] V. Trivedi, and J. Fossum, "Quantum-Mechanical Effects on the Threshold Voltage of Undoped Double-Gate MOSFETs," Electron Devices Lett., 26, p.579 (2005).

- [2.5] Y. Li and S.-M. Yu, "A unified quantum correction model for nanoscale singleand double-gate MOSFETs under inversion conditions," Nanotechnology, 15, p. 1009 (2004).

- [2.6] D. Vasileska and Z. Ren, SCHRED-2.1 Manual (2000).

- [2.7] M. V. Dunga, C.-H. Lin, D. D. Lu, W. Xiong, C. R. Cleavelin, P. Patruno, J.-R. Hwang, F.-L. Yang, A. M. Niknejad and C. Hu, "BSIM-MG: A Versatile Multi-Gate FET Model for Mixed-Signal Design," Proceedings of the VLSI

Technology Symposium, pp.. 80-81, 2007.

- [2.8] X. Liang and Y. Taur, "A 2-D Analytical Solution for SCEs in DG MOSFETs," IEEE Trans. Electron Devices, vol. 51, no. 9, pp. 1385-1391, 2004.

- [2.9] Q. Chen, E. M. Harrell, and J. D. Meindl, "A Physical Short-channel Threshold Voltage Model for Uundoped Symmetric Double-Gate MOSFETs," IEEE Trans. Electron Devices, vol. 50, no. 7, pp. 1631-1637, 2003.

- [2.10] K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie, and Y. Arimoto, "Scaling Theory for Double-Gate SOI MOSFETs," IEEE Trans. Electron Devices, vol. 40, no. 12, pp. 2326-2329, 1993.

- [2.11] K. Suzuki, Y. Tosaka, and T. Sugii, "Analytical Threshold Voltage Model for Short Channel n+/p+ Double-Gate SOI MOSFETs,," IEEE Trans. Electron Devices, vol. 43, no. 5, pp. 732-738, 1996.

- [2.12] K. K. Young, "Short-Channel Effect in Fully Depleted SOI MOSFET's," IEEE Trans. Electron Devices, vol. 36, no. 2, pp. 399-402, 1989.

- [2.13] G. Pei, J. Kedzierski, P. Oldiges, M. Ieong, and E. Kan, "FinFET Design Considerations Based on 3-D Simulation and Analytical Modeling," IEEE Trans. Electron Devices, vol. 48, no. 8, pp. 1441-1419, 2002.

- [2.14] B. Doyle, B. Boyanov, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R.

Rios, and R. Chau, "Tri-Gate Fully-Depleted CMOS Transistors: Fabrication, Design and Layout," in Proc. on VLSI Tech. Symp., 2003, pp. 133-134.

- [2.15] M. Stadele, R. J. Luyken, M. Roosz, M. Specht, W. Rosner, L. Dreeskornfeld, J. Hartwich, F. Hofmann, J. Kretz, E. Landgraf, and L. Risch, "A comprehensive study of corner effects in tri-gate transistors," in Proc. ESSDERC, 2004, pp. 165-168.

- [2.16] J. G. Fossum, J.-W. Yang, V. P. Trivedi, "Suppression of corner effects in triple-gate MOSFETs," IEEE EDL Vol. 24, pp. 745-747, 2003.

- [2.17] "DESSIS", TCAD release 9.0 Manual, Synopsys Inc., Mountain View, CA

# Chapter 3

# BSIM-CMG: A Compact Model for Symmetric/ Common-Gate Multi-Gate MOSFETs

#### 3.1 Introduction

The scaling of conventional planar CMOS is expected to become increasingly difficult due to increasing gate leakage and subthreshold leakage [3.1-3.2]. Multi-gate FETs such as FinFETs have emerged as the most promising candidates to extend the CMOS scaling into the sub-25nm regime [3.3-3.4]. The strong electrostatic control over the channel originating from the use of multiple gates reduces the coupling between source and drain in the subthreshold region and it enables the multi-gate transistor to be scaled beyond bulk planar CMOS for a given dielectric thickness. Numerous efforts are underway to enable large scale manufacturing of multi-gate FETs. At the same time, circuit designers are beginning to design and evaluate multi-gate FET circuits.

A compact model serves as a link between process technology and circuit design. It is a concise mathematical description of the complex device physics in the transistor. A compact model maintains a fine balance between accuracy and simplicity. An accurate model based on physics basis allows the process engineer and circuit designer to make projections beyond the available silicon data (scalability) for scaled dimensions and also enables fast circuit/device co-optimization. The simplifications in the physics enable very fast analysis of device/circuit behavior when compared to the much slower numerical based TCAD simulations. It is thus necessary to develop a compact model of multi-gate FETs for technology/circuit development in the short term and for product design in the longer term.

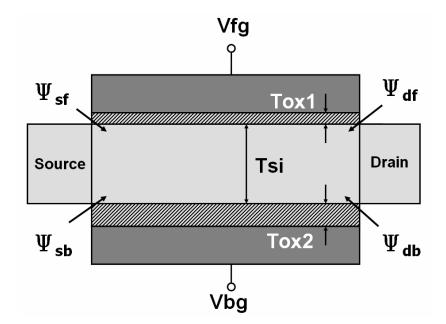

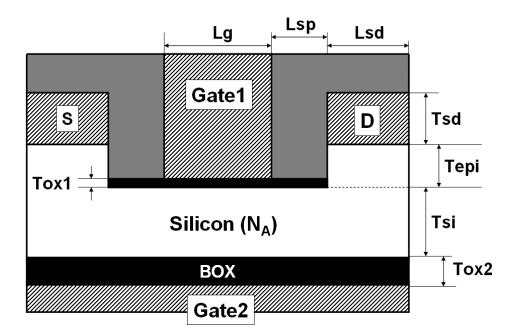

One of the biggest challenges in modeling multi-gate FETs is the need to model several flavors of multi-gate FETs. The silicon body can be controlled by either two gates or three gates or four gates. The gates can all be electrically interconnected or they can be biased independently. Multi-gate FETs can be built on SOI or bulk silicon. Fig. 3.1

illustrates some of the different architectures of multi-gate FETs which need to be accounted in the compact model. It is important to obtain a versatile model which can model all the different types of multi-gate FETs without making the model computationally intensive. One possible technique to handle the different multi-gate FET architectures is to classify them into two categories and introduce a separate model for each category: a symmetric/common gate model and an asymmetric/independent gate model. The term "common-gate" means that all the gates in the multi-gate FET (double-gate or triple-gate or quadruple-gate FinFET) are electrically interconnected and are biased at the same electrical gate voltage. The common-gate model further assumes that the gate work-functions and the dielectric thicknesses on the two, three or four active sides of the fin are the same. However, the carrier mobilities in the inversion layers on the horizontal and vertical active sides of the fin can be different due to different crystal orientations and/or strain. The asymmetric/independent gate model allows different work-functions and dielectric thicknesses on the two sides of the fin. The asymmetric/independent gate model also permits that the two gates can be biased independently.

The existing modeling efforts for the multi-gate FETs are limited to undoped or lightly doped silicon body for double-gate (DG) FETs [3.5-3.7]. A multiple threshold voltage

Fig. 3.1 Different possible architectures of multi-gate FET

technology based on symmetric/common-gate multi-gate FETs will likely require a significant concentration of body dopant for threshold voltage tuning. As a result, we have developed a core model considering the effect of finite body doping on the electrical characteristics of a multi-gate FET in the Poisson's equation [3.8]. Combining with numerous physical effects, such as quantum mechanical effect, short channel effects, mobility degradation, and carrier velocity saturation, BSIM-CMG (Berkeley

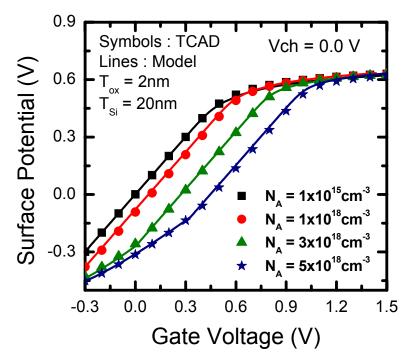

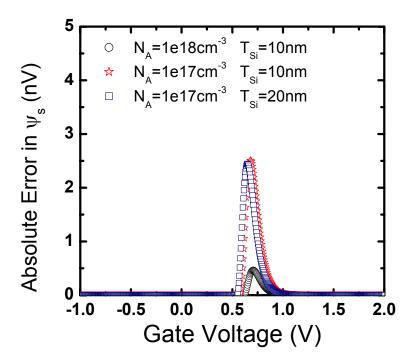

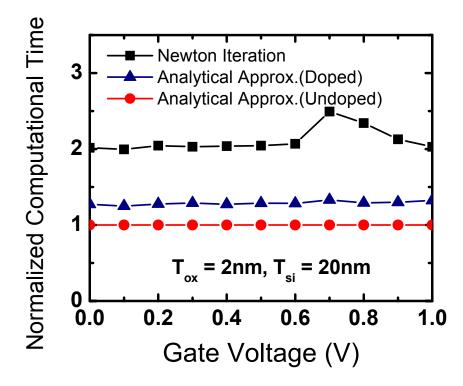

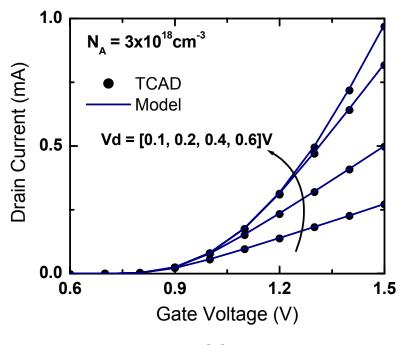

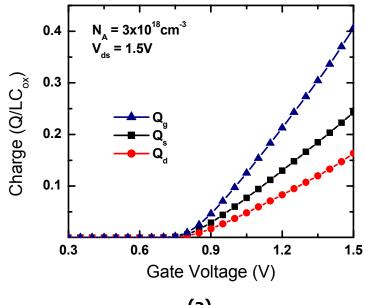

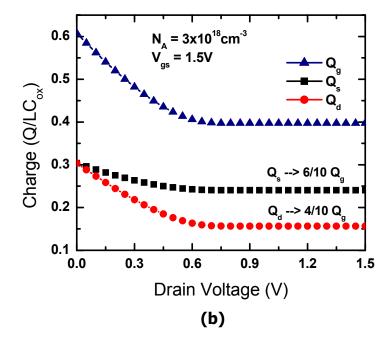

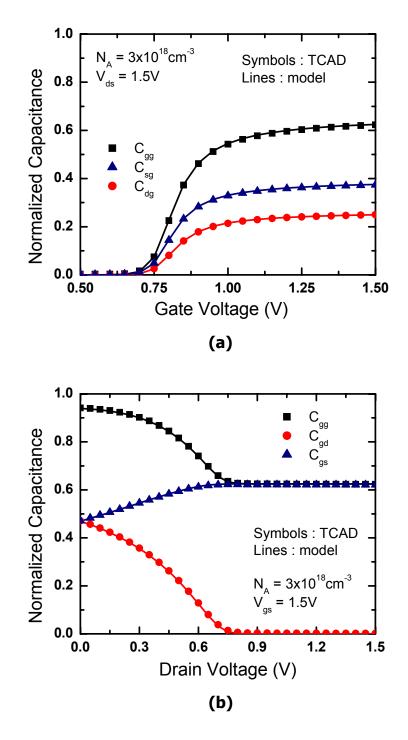

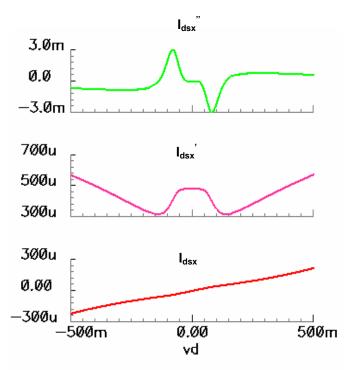

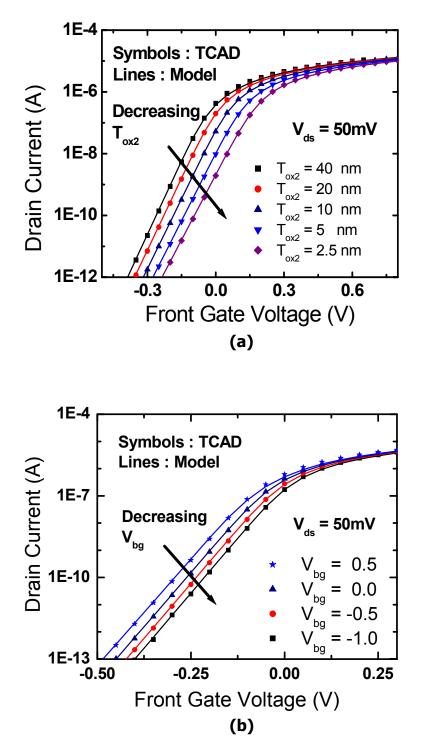

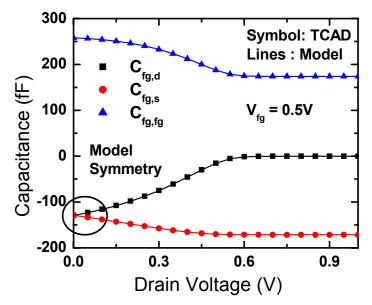

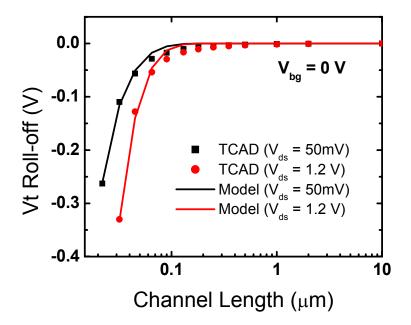

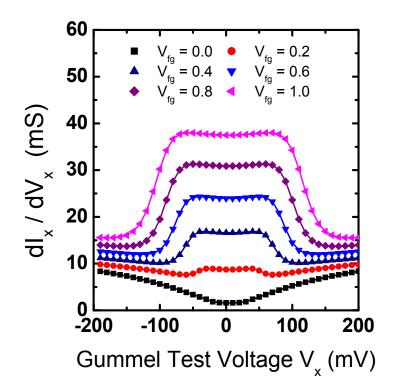

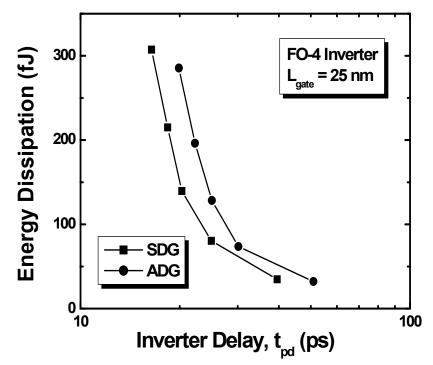

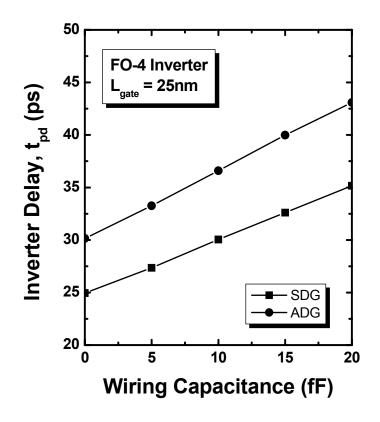

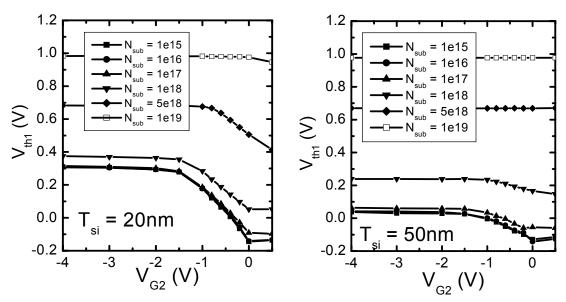

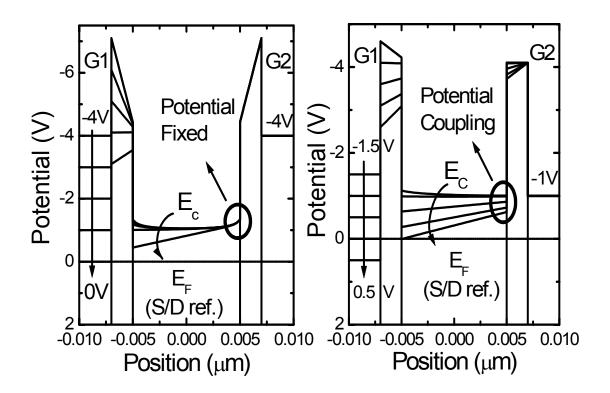

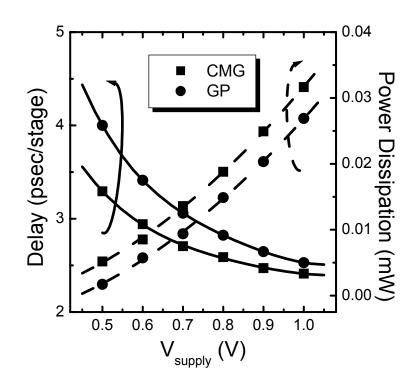

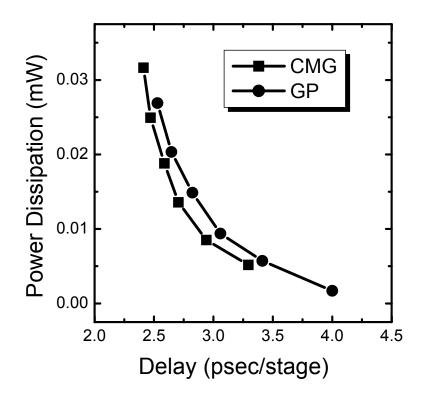

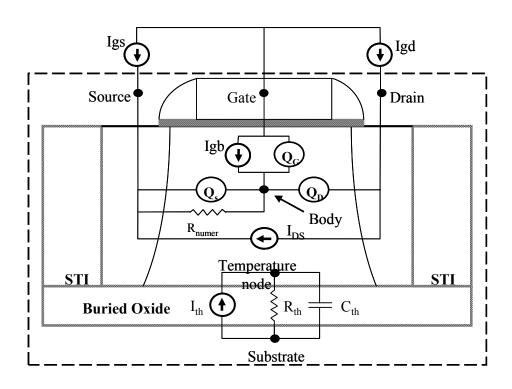

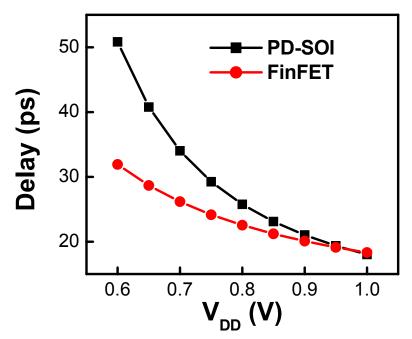

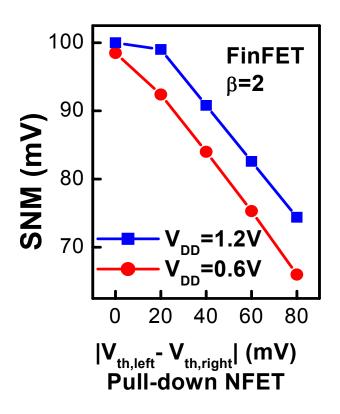

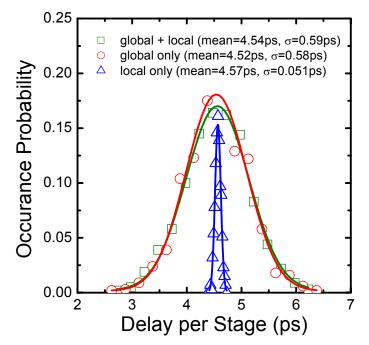

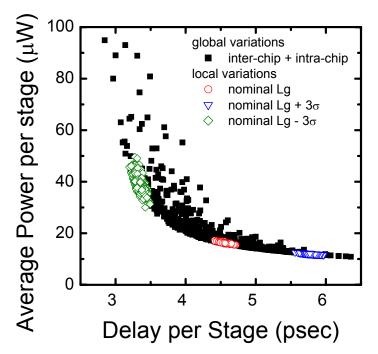

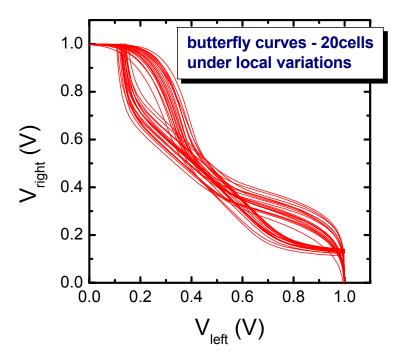

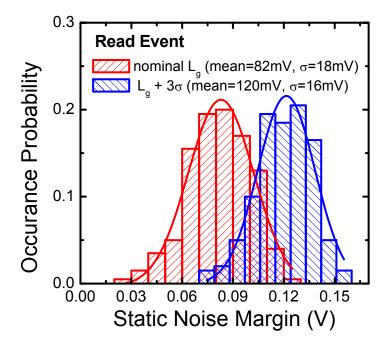

Short-channel IGFET Model – Common Multi-Gate) has been verified with the measured electrical characteristics of FinFETs [3.9]. BSIM-IMG (Berkeley Short-channel IGFET Model – Independent Multi-Gate) has been developed and verified with TCAD simulation results [3.10].