### Optimizing Partitioned Global Address Space Programs for Cluster Architectures

Wei-Yu Chen

#### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2007-140 http://www.eecs.berkeley.edu/Pubs/TechRpts/2007/EECS-2007-140.html

December 4, 2007

Copyright © 2007, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Optimizing Partitioned Global Address Space Programs for Cluster Architectures

by

Wei-Yu Chen

B.S. (University of California, Berkeley) 2000 M.S. (University of California, Berkeley) 2004

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

**Computer Science**

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Katherine A. Yelick, Chair Professor Rastislav Bodik Professor Gregory Fenves

Fall 2007

The dissertation of Wei-Yu Chen is approved:

Chair Date

Date

Date

University of California, Berkeley

Fall 2007

### Optimizing Partitioned Global Address Space Programs for Cluster Architectures

Copyright 2007

by

Wei-Yu Chen

Abstract

Optimizing Partitioned Global Address Space Programs for Cluster Architectures

by

Wei-Yu Chen

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Katherine A. Yelick, Chair

Unified Parallel C (UPC) is an example of a *partitioned global address space* language for high performance parallel computing. This programming model enables application to be written in a shared memory style, but still allows the programmer to control data layout and the assignment of work to processors. An open question is whether programs written in simple style, with fine-grained accesses and blocking communication, can achieve performance approaching that of hand-optimized code, especially for cluster environments with high network latencies.

This dissertation proposes an optimization framework for UPC that automates the transformations currently performed manually by programmers. The goals of the optimizations are twofold: not only do we seek to aggregate fine-grained remote accesses to reduce the number and volume of message traffic, but we also want to overlap communication with computation to hide network latency. The framework first applies communication vectorization and strip-mining to optimize regular array accesses in loops. For irregular finegrained accesses, we apply a partial redundancy elimination framework that also generates split-phase communication. The last phase targets the blocking bulk transfers in the program by utilizing runtime support to automatically schedule them and achieve overlap. Message aggregation is performed as part of the scheduling to further reduce the communication overhead. Finally, we present several techniques for optimizing the serial performance of a UPC program, in order to reduce both the overhead of UPC-specific constructs and our source-to-source translation.

The optimization framework has been implemented in the Berkeley UPC compiler, and has been tested on a number of supercomputer clusters. The optimizations are validated on a variety of benchmarks exhibiting different communication patterns, from bulk synchronous benchmarks to dynamic shared data structure code. Experimental results reveal that our framework offers comparable performance to aggressive manual optimization, and can achieve significant speedup compared to the fine-grained and blocking communication code that programmers find much easier to implement. Our framework is completely transparent to the user, and therefore improves productivity by freeing programmers from the details of communication management.

Chair

Date

# Contents

| 1 Introduction |      | oduction                                     | 1  |

|----------------|------|----------------------------------------------|----|

|                | 1.1  | An Optimizations Framework for PGAS Programs | 4  |

|                | 1.2  | Overview of the Optimizations                | 6  |

| 2              | Bac  | kground                                      | 11 |

|                | 2.1  | Unified Parallel C                           | 11 |

|                | 2.2  | The Berkeley UPC Compiler                    | 14 |

|                | 2.3  | Translation Framework Overview               | 16 |

|                | 2.4  | Memory Consistency Models                    | 21 |

| 3              | Exp  | erimental Setup                              | 25 |

| 4              | Sing | le-Node Performance                          | 30 |

|                | 4.1  | Standard C Code Performance                  | 31 |

|   | 4.2  | Performance of Pointer-to-shared Operations            |  |  |

|---|------|--------------------------------------------------------|--|--|

|   | 4.3  | Optimizing UPC Forall Parallel Loop                    |  |  |

|   |      | .3.1 Affinity Test Removal                             |  |  |

|   |      | .3.2 Privatizing Shared Local Accesses in Forall Loops |  |  |

|   |      | .3.3 Experimental Results                              |  |  |

| 5 | Opti | izing Fine-grained Array Accesses 48                   |  |  |

|   | 5.1  | Optimizing Regular Communication in Loops              |  |  |

|   | 5.2  | Practical Considerations for Message Strip-Mining      |  |  |

|   | 5.3  | An Empirical Study for Strip-mining                    |  |  |

|   |      | .3.1 Overall Benefit of Strip-mining                   |  |  |

|   |      | .3.2 Effects of Loop Computation Overhead              |  |  |

|   |      | .3.3 Selecting the Strip Size                          |  |  |

|   |      | .3.4 Effects of Unrolling                              |  |  |

|   | 5.4  | mplementation                                          |  |  |

|   | 5.5  | Experimental Results                                   |  |  |

| 6 | Opti | izing Fine-grained Irregular Accesses 70               |  |  |

|   | 6.1  | Algorithm Overview                                     |  |  |

|   | 6.2  | Optimizing Shared Pointer Arithmetic    73             |  |  |

|   | 6.3  | Split-phase Communication for Reads                              |  |  |  |

|---|------|------------------------------------------------------------------|--|--|--|

|   | 6.4  | Split-phase Communication for Writes                             |  |  |  |

|   | 6.5  | Coalescing Communication Calls                                   |  |  |  |

|   | 6.6  | Example                                                          |  |  |  |

|   | 6.7  | Experimental Results                                             |  |  |  |

|   | 6.8  | Application Study                                                |  |  |  |

| 7 | Opti | nizing Bulk Communication 88                                     |  |  |  |

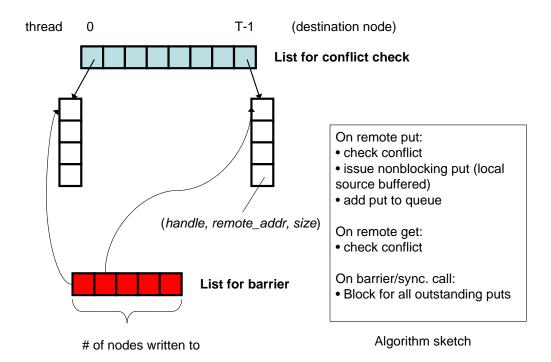

|   | 7.1  | Design and Implementation                                        |  |  |  |

|   |      | 7.1.1 Optimizing Puts                                            |  |  |  |

|   |      | 7.1.2 Optimizing Gets                                            |  |  |  |

|   |      | 7.1.3 Automatic Communication Aggregation                        |  |  |  |

|   | 7.2  | Performance Analysis                                             |  |  |  |

|   |      | 7.2.1 Buffering Overhead                                         |  |  |  |

|   |      | 7.2.2 Communication-Related Overhead of Speculative Prefetch 102 |  |  |  |

|   |      | 7.2.3 Effectiveness of Communication Aggregation                 |  |  |  |

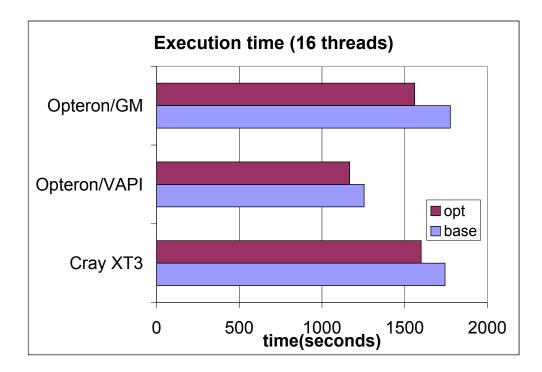

|   | 7.3  | Experimental Results                                             |  |  |  |

|   | 7.4  | Breakdown of Benchmark Performance                               |  |  |  |

|   |      |                                                                  |  |  |  |

### 8 Related Work

| Bi | Bibliography |                                     |                                                |     |

|----|--------------|-------------------------------------|------------------------------------------------|-----|

| 9  | Con          | clusions                            |                                                | 124 |

|    |              | 8.2.3                               | Optimizing Bulk Communication                  | 122 |

|    |              | 8.2.2                               | Optimizing for Fine-grained Irregular Accesses | 120 |

|    |              | 8.2.1                               | Optimizing for Fine-grained Regular Accesses   | 119 |

|    | 8.2          | Optimizations for Parallel Programs |                                                | 116 |

|    | 8.1          | Parallel Programming Models         |                                                | 113 |

# **List of Figures**

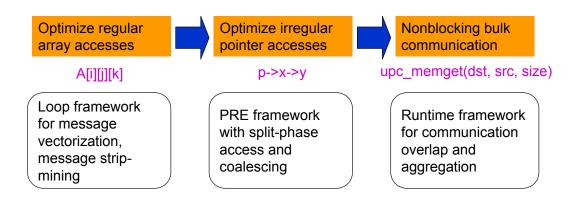

| 1.1 | Summary of communication optimizations in our framework                    | 8  |

|-----|----------------------------------------------------------------------------|----|

| 2.1 | UPC memory model with sample variable declarations                         | 12 |

| 2.2 | Vector addition benchmark in UPC                                           | 14 |

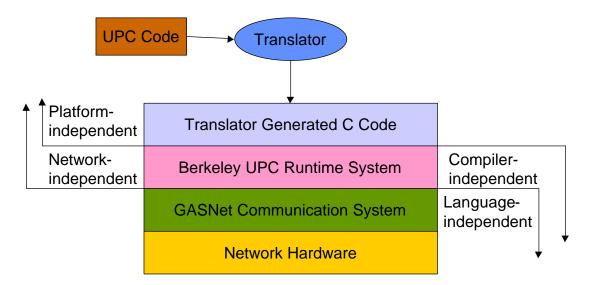

| 2.3 | The Berkeley UPC compiler                                                  | 15 |

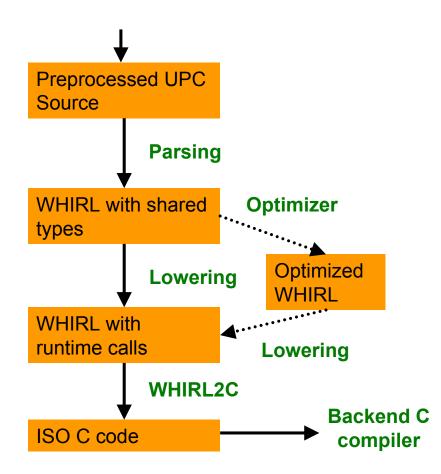

| 2.4 | UPC-to-C translation process                                               | 17 |

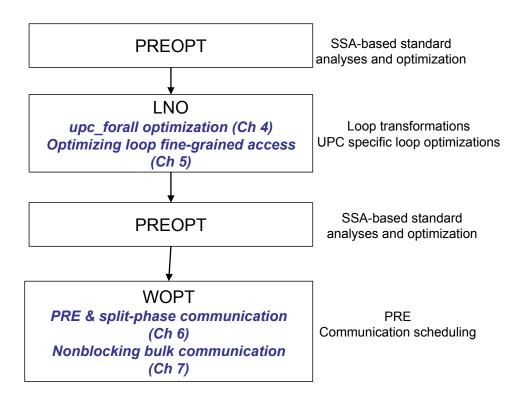

| 2.5 | Optimization framework for the translator.                                 | 20 |

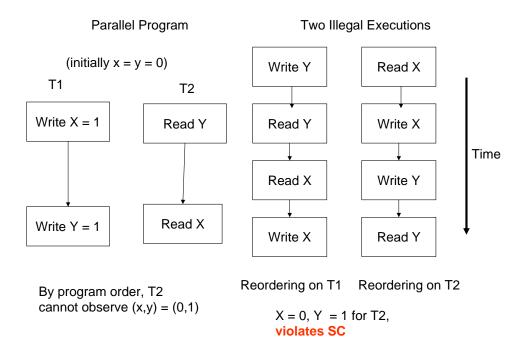

| 2.6 | Example of reordering that violates the strict memory model                | 23 |

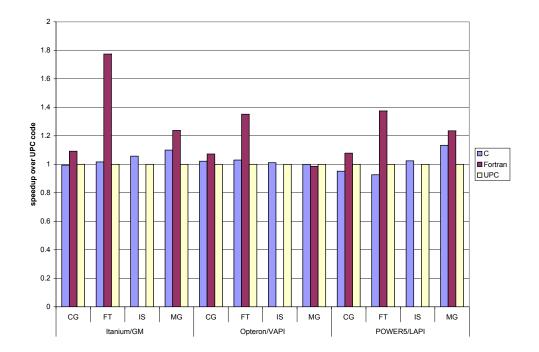

| 4.1 | Serial performance comparison: UPC v. C v. Fortran. Class A input is used. | 34 |

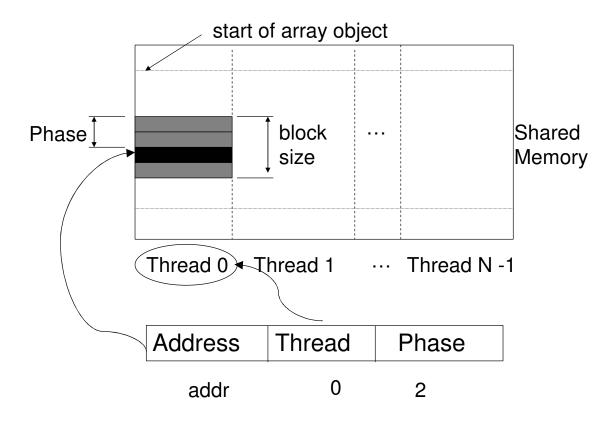

| 4.2 | UPC pointer-to-shared components.                                          | 35 |

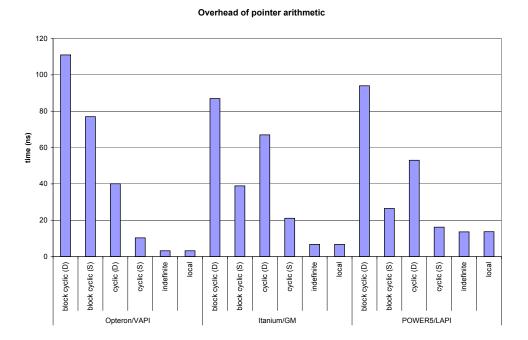

| 4.3 | Performance of UPC pointer arithmetic. (D) denotes dynamic threads, (S)    |    |

|     | static threads.                                                            | 37 |

| 4.4 | Performance for UPC shared local access                                    | 39 |

| 4.5 | upc_forall loop affinity test removal.                                     | 41 |

| 4.6 | Examples of forall loop iteration to thread mapping. The original forall   |    |  |

|-----|----------------------------------------------------------------------------|----|--|

|     | loop appears at the top, while the result C code is at bottom.             | 42 |  |

| 4.7 | Privatization of shared local accesses in forall loops                     | 45 |  |

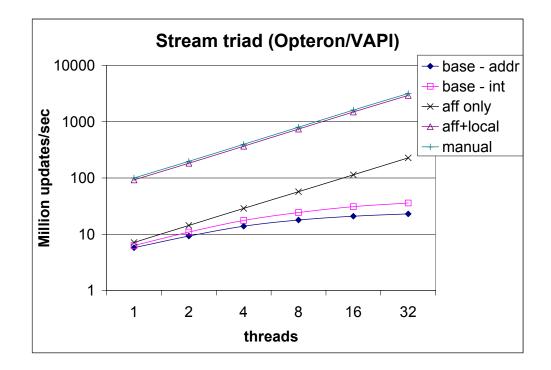

| 4.8 | Stream triad benchmark on the Opteron/VAPI system                          | 46 |  |

| 5.1 | Unoptimized loop, where r is remote.                                       | 51 |  |

| 5.2 | Vectorized loop                                                            | 51 |  |

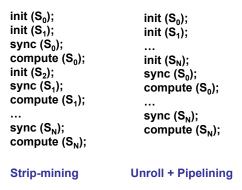

| 5.3 | Message strip-mining.                                                      | 51 |  |

| 5.4 | Unrolling a strip-mined loop.                                              | 51 |  |

| 5.5 | Traditional LogP model for sending a point-to-point message                | 52 |  |

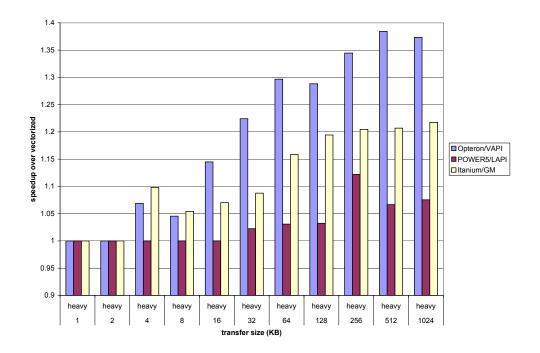

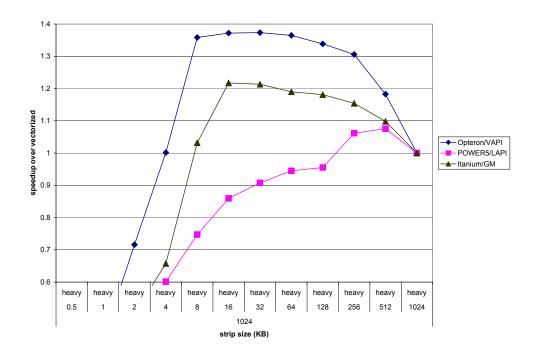

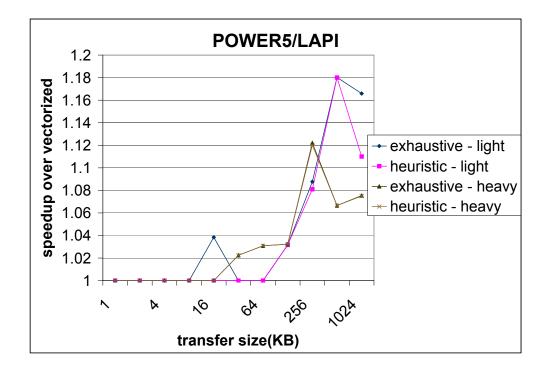

| 5.6 | Maximum speedup achieved by message strip-mining, for transfer size        |    |  |

|     | from 1KB to 1MB.                                                           | 55 |  |

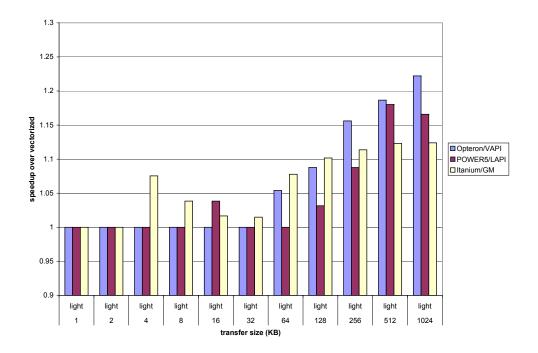

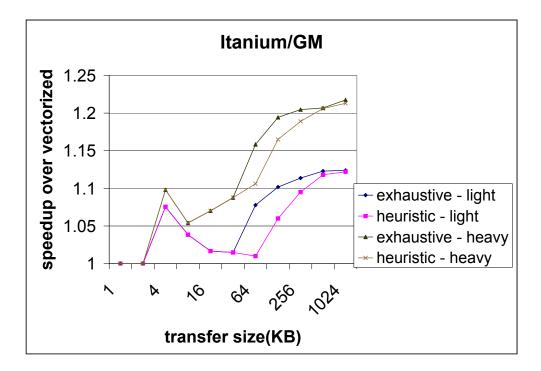

| 5.7 | Maximum speedup achieved by message strip-mining, with light computa-      |    |  |

|     | tion                                                                       | 57 |  |

| 5.8 | Speedup achieved by various strip sizes for a 1MB transfer, heavy compu-   |    |  |

|     | tation.                                                                    | 58 |  |

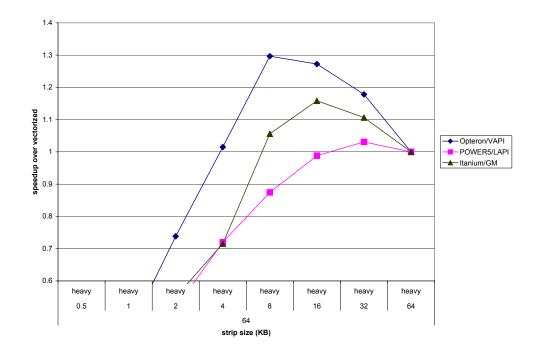

| 5.9 | Speedup achieved by various strip sizes for a 64KB transfers, heavy com-   |    |  |

|     | putation                                                                   | 59 |  |

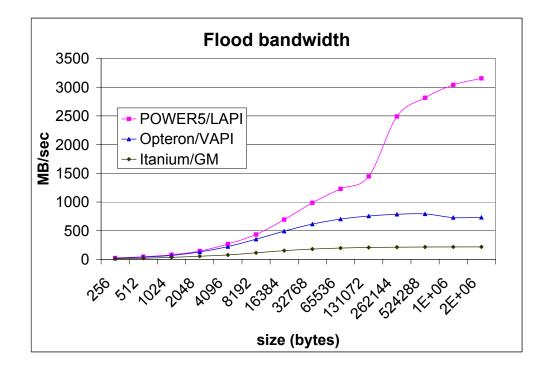

| 5.1 | 0 Flood bandwidth for blocking gets                                        | 60 |  |

| 5.1 | 1 Accuracy of strip-mining performance model for the Opteron/VAPI cluster. | 62 |  |

| 5.12 | 2 Accuracy of strip-mining performance model for the POWER5/LAPI cluster. 63    |     |  |  |

|------|---------------------------------------------------------------------------------|-----|--|--|

| 5.13 | Accuracy of strip-mining performance model for the Itanium/GM cluster 6         |     |  |  |

| 5.14 | Communication schedule for strip-mining and unrolling                           | 65  |  |  |

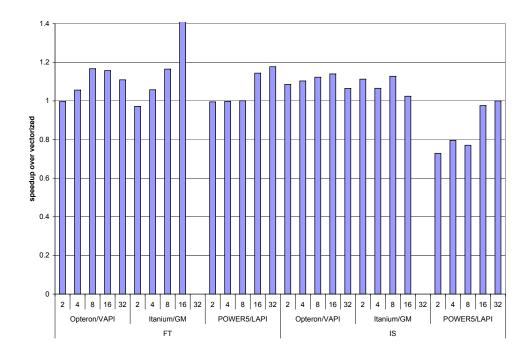

| 5.15 | Speedup for message strip-mining on two NAS benchmarks                          | 68  |  |  |

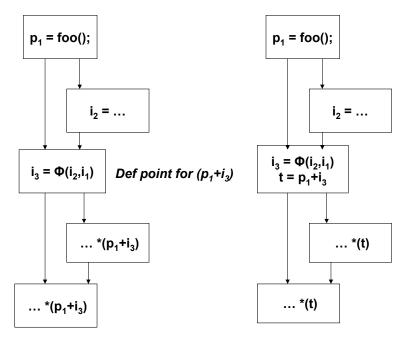

| 6.1  | Redundancy elimination for shared pointer arithmetic.                           | 74  |  |  |

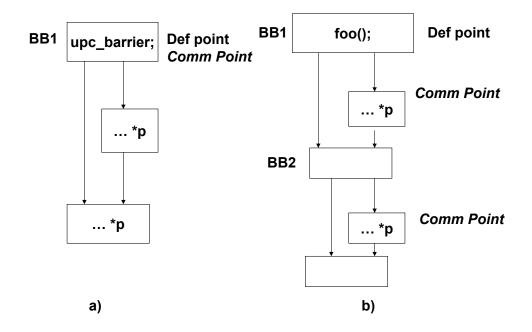

| 6.2  | Split-phase analysis for reads. Communication points correspond to gets,        |     |  |  |

|      | actual use syncs                                                                | 76  |  |  |

| 6.3  | Split-phase analysis for writes.                                                | 79  |  |  |

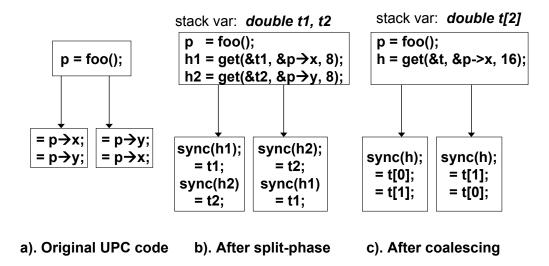

| 6.4  | Compiler directed coalescing.                                                   | 80  |  |  |

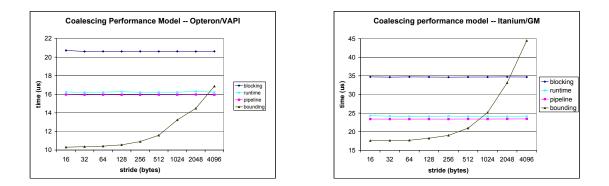

| 6.5  | Performance model for fine-grained coalescing                                   | 82  |  |  |

| 6.6  | Sample code from optimized programs.                                            | 83  |  |  |

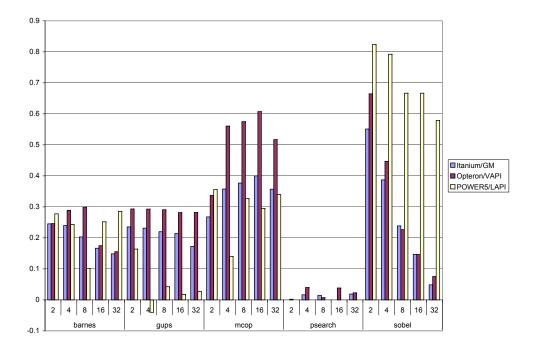

| 6.7  | Optimization speedup, measured as fraction over unoptimized version             | 84  |  |  |

| 6.8  | Performance on a CFD application                                                | 87  |  |  |

| 7.1  | Candidates for our nonblocking optimization.                                    | 90  |  |  |

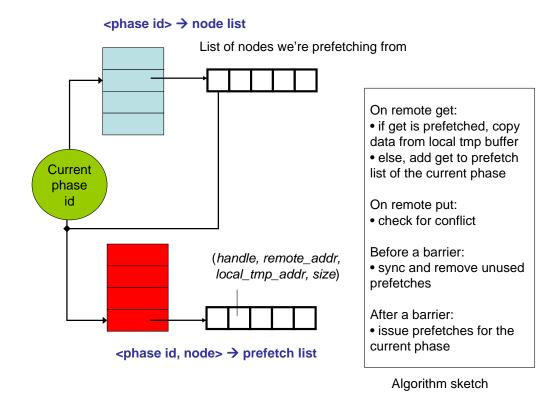

| 7.2  | Runtime structure for nonblocking puts                                          | 93  |  |  |

| 7.3  | Runtime structure for get prefetching                                           | 97  |  |  |

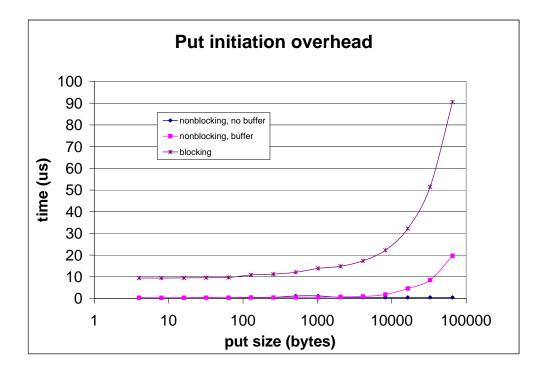

| 7.4  | Put initiation overhead.                                                        | 101 |  |  |

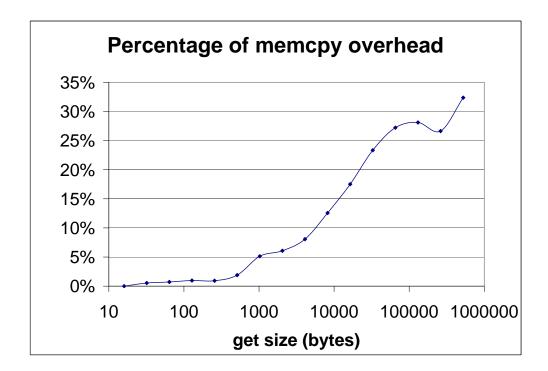

| 7.5  | Memory copy overhead for prefetched gets, measured as $T_{memcpy}/T_{memget}$ . | 102 |  |  |

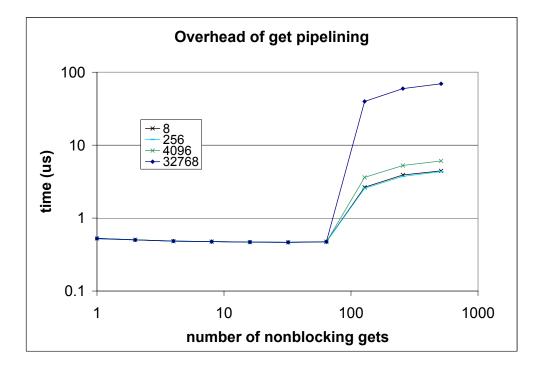

| 7.6  | Prefetch initiation overhead, for each individual get |

|------|-------------------------------------------------------|

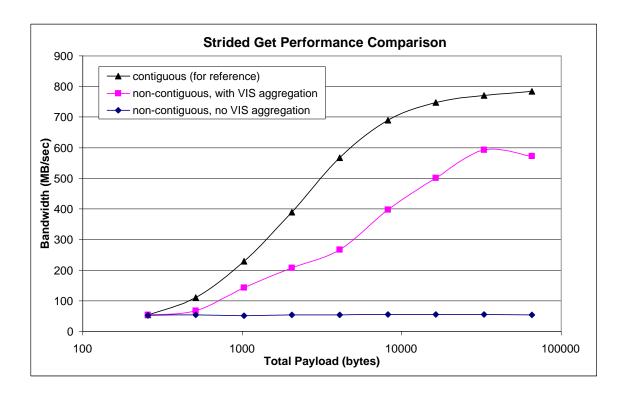

| 7.7  | Strided get performance micro-benchmark               |

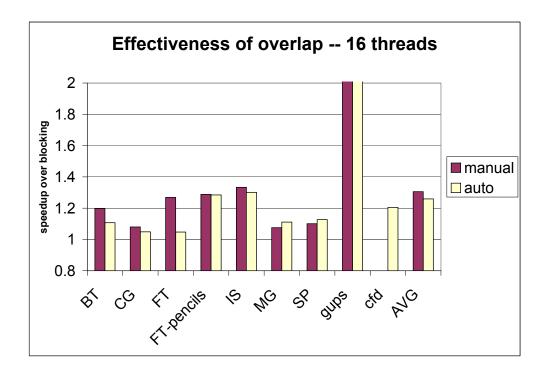

| 7.8  | Optimization speedup for 16 threads                   |

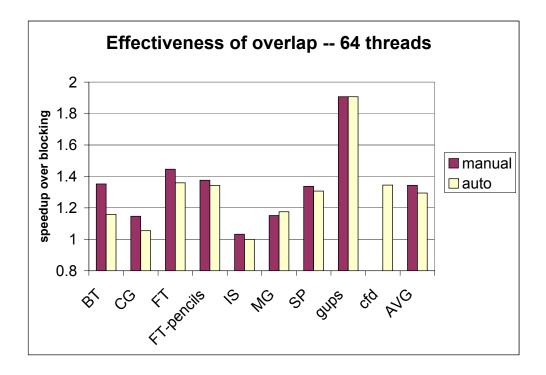

| 7.9  | Optimization speedup for 64 threads                   |

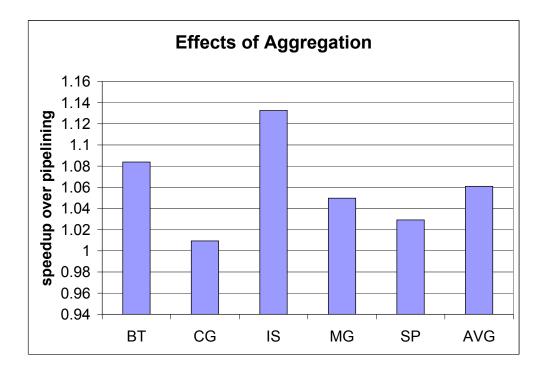

| 7.10 | Performance comparison with and without aggregation   |

## **List of Tables**

| 3.1 | Machine summary                                                       | 26  |

|-----|-----------------------------------------------------------------------|-----|

| 3.2 | Benchmark summary. Results for the last two columns were collected on |     |

|     | 16-thread runs, using data from thread zero                           | 27  |

|     |                                                                       |     |

| 7.1 | Breakdown of nonblocking put time (16 threads). All values are in mi- |     |

|     | croseconds.                                                           | 109 |

| 7.2 | Breakdown of nonblocking get time (16 threads). All values are in mi- |     |

|     | croseconds.                                                           | 110 |

#### Acknowledgments

First and foremost, I am deeply grateful to my advisor Kathy Yelick, as this dissertation would not have been completed without her guidance for the past five years. She introduced me to the area of parallel computing, taught me how to write papers and do research, and always managed to find time in her busy schedule to guide and mentor my work.

I am also thankful for the interactions with other members of my dissertation committee. Ras Bodik was kind enough to read both my Master's thesis and later this dissertation, and provided many valuable suggestions from the PL angle. Greg Fenves offered big-picture insights on how my optimizations could be applicable to read world scientific applications.

I would also like to thank my colleagues in the Berkeley UPC group, including Christian Bell, Dan Bonachea, Jason Duell, Paul Hargrove, Parry Husbands, Costin Iancu, Rajesh Nishtala, and Mike Welcome. My research has benefited tremendously from their work, and they have been important co-authors on several papers that form the basis of this dissertation. Costin Iancu deserves special thanks for his crucial contributions on the Berkeley UPC translator. I really enjoyed the friendship of my office mates over the years (Christian Bell, Dan Bonachea, Kaushik Datta, Rajesh Nishtala, and Jimmy Su), and I can always count on them to answer my questions and read paper drafts.

Last but definitely not least, I would like to thank my family and friends for their continuous support. My parents gave me the opportunity to come to the United States, and their love and encouragements were the fuel that propelled me through six years of graduate school. Finally thanks go to my sister Irene, who despite having endured years of my whining is still someone that I can tell anything and everything to.

## Chapter 1

## Introduction

Today clusters are the dominant architecture in high performance computing arena due to their excellent cost/performance ratio. Clusters represent 75% of the systems in the most recent (June 2007) ranking on the world's top 500 fastest computers [101], with several boasting a processor count of more than 10,000. In the meantime, chip multiprocessors (CMP) have become part of mainstream computing, with Intel and AMD both transitioning their product line to quad-core processors. The prevailing hardware trends indicate that tomorrow's applications must embrace parallelism in order to leverage the power of the massively parallel computer systems in the future.

Writing parallel software is a notoriously difficult task, however, due to the correctness issues that arise from nondeterminism and the subtle performance characteristics of locality and parallelism. Today, most parallel software is written in one of two programming models: Two-sided message passing (i.e., MPI [79]) is used on large-scale machines and clusters, while shared memory programming (often with dynamically created threads or OpenMP [85]) is used on smaller machines with hardware support for shared memory. Both models have their problems. Message passing gives programmers control over performance-critical features, such as locality and load balance, but the need to pack and unpack messages and coordinate between senders and receivers is tedious and sometimes awkward. Traditional shared memory programming offers flexible communication by allowing one thread to directly read and write into shared data structures, but lacks control over data layout or other forms of locality management that are essential to performance. The contrast between the two models reflects the challenges of finding the appropriate levels of abstraction for the underlying hardware. Exposing low level details about the architecture delivers performance, but hurts productivity by requiring programmers to make explicit decisions about communication management and data decomposition. On the other hand, a high level abstraction simplifies the task of parallel programming, but makes it more difficult for programmers to overcome the abstraction and achieve performance.

In this dissertation, we will examine a relatively new class of languages called Partitioned Global Address Space (PGAS) languages that offer some advantages of both models. The global address space abstraction supports shared data structures, but the space is partitioned into processor domains so that programmers can control data layout for performance. Each of the current PGAS languages is based on a popular sequential programming language, so that their syntax will appear familiar to many programmers. Unified Parallel C (UPC) [100] is an extension of ISO C, Co-Array Fortran [83] is an extension of Fortran 90, and Titanium [51, 111] is primarily an extension of Java, but with Java's thread features omitted.

Previous work has demonstrated that these languages offer significant advantages in

both programmability and performance relative to MPI [25, 31, 40, 43]. The programmability advantages come primarily from the global address space, as the communication code is much simpler when implemented as memory accesses. Additional advantages accrue from high level language support, such as distributed array abstractions. More surprising is the performance advantage of PGAS languages for some applications, which comes from their use of a *one-sided* communication model [12]. In one-sided communication, data transfers are decoupled from inter-thread synchronization, and this allows for more efficient use of cluster network hardware. For small and medium size messages, one-sided communication can outperform two-sided message passing by 20%-80% on networks with remote direct memory access (RDMA) support. PGAS languages thus offer a more convenient and productive programming style than explicit message passing, and good performance can still be achieved because programmers retain explicit control of data placement and load balancing. Another virtue of PGAS languages is their versatility, since they can run well on both shared and distributed memory machines.

In spite of the positive performance and programmability results for the PGAS languages, these studies have confirmed the need for hand-tuning of code. Programs that perform single-word remote reads and writes, while very simple to program, are not always practical on machines with high communication latency. Due to the loose coupling of the network interconnects and the microprocessors, fine-grained remote accesses are inherently expensive operations on cluster architectures; the cost of sending an eight-byte message is typically between 4 - 20us on today's high-performance networks [11]. Consequently, PGAS programmers sometimes need to invest substantial efforts to make their applications performance portable, by manually scheduling and combining remote accesses to reduce communication overhead. Such manual transformations can often be tedious and error-prone, and negate some of the productivity advantages offered by PGAS languages.

### **1.1 An Optimizations Framework for PGAS Programs**

The premise of this dissertation is that using sophisticated program analyses and optimizations, UPC programs written in a straightforward manner can attain performance approaching that of hand-optimized code. Our approach is to look at the optimizations that have been the most successful in hand-optimized code and devise techniques for automating them in the UPC compiler and runtime system. While some of these optimizations have enormous performance impacts, this work remains a significant departure from automatic parallelization, which is widely viewed as intractable for large-scale machines. In our setting, the application programmer is responsible for identifying parallelism and distributing data structures, while the compiler is responsible for selecting communication mechanisms and optimizing single node performance for UPC constructs.

This research in PGAS language analysis and optimizations uses the UPC language and the Berkeley UPC compiler as the vehicle for study, although many of the results are applicable to the other languages and compilers. The Berkeley UPC Project is a joint Lawrence Berkeley National Laboratory and UC Berkeley research effort aimed at increasing the portability of UPC programs by building a portable, open source compiler framework that also offers comparable performance to commercial UPC implementations. To achieve portability and high performance, the Berkeley UPC compiler uses a layered design, which can be tailored to adapt to the communication primitives and processor architectures offered by different platforms. Specifically, the compiler generates C code that contains calls to a UPC runtime interface [13], which is implemented atop a languageindependent communication layer called GASNet [16].

The cost of a message transfer on a cluster interconnect can be divided into two components: a per-message cost influenced by the latency of the network, and a per-byte cost influenced by the communication bandwidth of the network. This suggests that aggregating small messages into large ones can be an effective optimization, since it amortizes the fixed per-message costs and utilizes the high bandwidth provided by the network for large messages. Making the transfers nonblocking and overlapping them is another common optimization that is especially useful for PGAS programs, as the software overheads for one-sided accesses tend to be considerably lower compared to MPI messages. Our framework uses a combination of compiler and runtime support to implement both approaches for optimizing communication:

- *Communication aggregation*: Our framework primarily targets programs with finegrained accesses and transforms them into coarser-grained transfers, but bulk communication calls to non-contiguous memory regions on the same processor can also benefit from our optimizations. This optimization reduces the number of remote accesses and amortizes communication latency.

- *Communication overlapping*: Our framework automatically transforms blocking remote accesses (either fine-grained or bulk) into nonblocking communication to overlap communication with computation and with other communication events. This optimization enables the processor to perform useful computation work instead of sitting idle while waiting for the remote transfer to complete. Overlap with computation may also reduce the effects of network contention by spreading communication

over a longer period of time.

The two principles of communication optimizations, aggregation and overlapping, may be incompatible in some situations. For example, aggregating small accesses into a single bulk transfer achieves better bandwidth, but could decrease the amount of communication and computation overlap available. Similarly, separating the initiation of a nonblocking access as far as possible from its completion maximizes the amount of overlap, but could reduce the opportunities for communication aggregation. The tradeoffs between the two approaches can be highly dependent on the particular system (e.g., send overhead, bandwidth, queue depth) and application (e.g., communication pattern, message size) in question. Balancing the two optimization goals is thus a challenge for our optimizations, as there is no complete solution that can guarantee optimal performance. Instead, we apply heuristics based on performance models to ensure that our framework can achieve performance that approaches and sometimes exceeds that of hand optimized code.

### **1.2** Overview of the Optimizations

Our framework consists of three communication optimization phases, plus miscellaneous optimizations that improve uniprocessor performance. The correctness of these optimizations relies on the relaxed UPC memory consistency model, as they change the order of shared memory operations, which may be visible to other threads.

• *Serial optimizations:* Although communication overhead tends to receive more attention when optimizing parallel programs, uniprocessor performance is equally important for achieving good overall performance, since scalable applications will spend most of their execution time in local computation code. To achieve good serial performance, we carefully tune the compiler framework to generate good quality C output that can be optimized by the backend compiler. We also develop several optimization techniques to reduce the overhead of UPC specific constructs, including shared pointer manipulation functions and the **upc\_forall** parallel loop. Chapter 4 summarizes these optimizations.

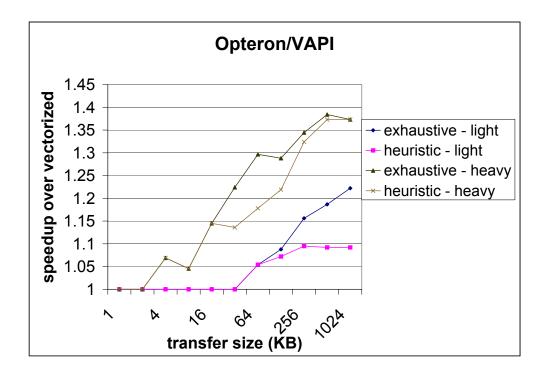

- *Optimizing fine-grained regular accesses:* In the first phase of our framework, we apply *message vectorization* to hoist individual array accesses out of loops and aggregate them into a single transfer. Message vectorization has been studied extensively in the context of data parallel languages, and traditional techniques try to aggregate as much as possible to reduce the number of messages. While minimizing message count is an important optimization goal, it can lead to missed opportunities for overlap. Our approach applies a transformation called *message strip-mining* that is more effective for PGAS programs. Message strip-mining attempts to reduce the overall communication costs by breaking up large message transfers into smaller ones that can be overlapped with computation. By deriving a performance model using synthetic benchmarks, we develop heuristics that enable strip-mining to significantly outperform the vectorized loop. The optimizations are described in Chapter 5.

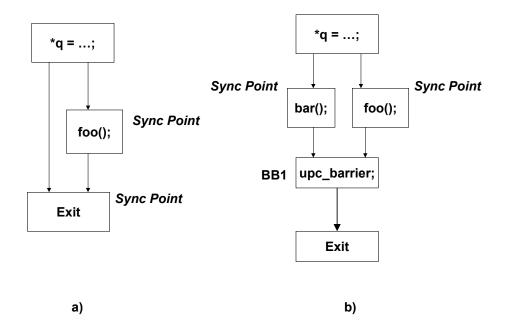

- *Optimizing fine-grained irregular accesses:* For irregular pointer-based accesses that are not amenable to our array-based optimizations, we develop a separate static analysis framework that performs partial redundancy elimination (PRE) to both shared fine-grained accesses as well as shared pointer arithmetic. Code motion is applied as part of the framework to automatically generate split-phase communication, by sep-

arating the initiation of a remote access from its completion. During communication scheduling, small reads and writes that exhibit spatial locality (i.e., they belong to the same array or struct) may also be coalesced into a single transfer. Chapter 6 presents these optimizations.

• *Optimizing bulk memory transfers:* While our PRE framework is effective for finegrained irregular accesses, it can have difficulties optimizing bulk communication routines due to the limitations in static array range and shape analysis, especially for C-based languages. Therefore, in the third phase of the framework, we develop runtime techniques to automatically transform blocking bulk transfers into nonblocking communication calls. Correctness is preserved via runtime conflict checks and double buffering, and the system also recognizes special access patterns and aggregates them to further improve performance. Chapter 7 presents our optimizations.

Figure 1.1: Summary of communication optimizations in our framework

Figure 1.1 summarizes the communication optimizations applied by our framework. Together the framework covers a wide range of communication patterns, from fine-grained accesses to bulk synchronous transfers. All three phases combine the use of communication aggregation with communication and computation overlap in order to achieve the best performance. Each of the optimization phases operates independently, so that programmers can selectively enable the individual phases based on their application needs. More importantly, all of the optimizations are transparent to the user. Thus, while our optimization framework is not always as effective as aggressive manual transformations, it can improve productivity by freeing programmers from the details of communication management, which is also one of the major design goals for PGAS languages.

The optimizations are evaluated on a variety of benchmarks, ranging from the bulk synchronous benchmarks to dynamic shared data structure code with irregular accesses. Several supercomputer clusters were used in the experiments, covering the most popular system architectures and network interconnects. Experimental results suggest that all of the optimization phases are needed to maximize the framework's effectiveness. In terms of serial performance, despite the source-to-source code generation, the Berkeley UPC compiler suffers a less than 2.5% performance loss compared to sequential C code. Our optimizations are also effective at reducing the serial overhead associated with UPC-specific constructs such as shared pointer arithmetic and forall parallel loops.

In terms of communication optimizations, the message strip-mining transformation in Chapter 5 can bring up to a 40% speedup on micro-benchmarks and a 10-20% speedup on two of the NAS benchmarks compared to the reference implementation that uses blocking communication. The static optimization framework in Chapter 6 can achieve significant performance improvement for common fine-grained communication patterns, offering speedup as high as 80%. On a full computational fluid dynamics (CFD) application with a lot of irregular accesses, our framework achieves a 10% speedup overall and a 30% speedup on the communication phase of the application. Finally, our runtime-based non-blocking transformation of bulk transfers delivers a near 30% performance improvement over the original blocking code, and is only slightly worse than manual optimizations.

## Chapter 2

## Background

In this chapter, we present a high level overview of the UPC language and the Berkeley UPC compiler, focusing on aspects relevant to the optimizations described in this dissertation. More details on the compiler can be found in [25] and [27], and the language specification provides a comprehensive definition of the UPC language [100].

### 2.1 Unified Parallel C

UPC is a parallel extension of the ISO C programming language aimed at supporting high performance scientific applications. The language adopts the Single-Program-Multiple-Data (SPMD) programming model, so that every thread runs the same program but keeps its own private local data. Each thread has a unique integer identity expressed as the MYTHREAD variable, and the THREADS variable represents the total number of threads, which can either be a compile-time constant or specified at runtime.

In addition to each thread's private address space, UPC provides a shared memory area to facilitate communication among threads, and programmers can declare a shared object by specifying the shared type qualifier. While a private object may only be accessed by its owner thread, all threads can read or write data in the shared address space. The shared memory space is logically divided among all threads, so from a thread's perspective the shared space can be further divided into a local shared memory and remote one. Data located in a thread's local shared space are said to have "affinity" with the thread. Figure 2.1 illustrates UPC's Partitioned Global Address Space model. While a thread can only access its own copy of the private variable mine, a single copy of the shared variable ours exists on thread zero and can be used by all threads.

| Thread <sub>0</sub>             | Thread <sub>1</sub>      |                          | Thread <sub>n-1</sub>             |

|---------------------------------|--------------------------|--------------------------|-----------------------------------|

| ours:<br>x[0],x[n]<br>y[0],y[1] | x[1],x[n+1]<br>y[2],y[3] | Shared                   | x[n-1],x[2n-1]                    |

| loc:<br>glob:<br>mine:          | loc:<br>glob:<br>mine:   | Remote access<br>Private | loc: Local shared access<br>glob: |

#define n THREADS

shared int ours;

int mine;

shared double x[2\*n]; //cyclic array

shared [2] double y[2\*n]; //block cyclic array

double \*loc; //local pointer

shared double \*glob; //gobal pointer (pointer-to-shared)

Figure 2.1: UPC memory model with sample variable declarations.

Figure 2.1 also shows how the pointers in UPC can be classified based on the locations of the pointers and of the objects they point to. A local pointer such as loc may only reference local data (i.e., the pointer and the pointed object belong to the same thread), but the data may live in either the private or the shared space of the thread. A global pointer glob may only used to reference data in the shared address space, which may be either local (a shared local access) or remote (a shared remote access). A global pointer is therefore also named a pointer-to-shared. Dereferencing local shared data with a global pointer is slower than using a local pointer due to the extra overhead in determining affinity, and shared remote accesses in turn are typically significantly slower because of the network overhead. Communication in UPC can be either implicit through pointer dereferences and shared array accesses, or explicit through the **upc\_memget**, **upc\_memput**, and **upc\_memcpy** calls.

UPC gives the user direct control over data placement through shared memory allocation and distributed arrays. When declaring a shared array, programmers specify a block size in addition to the dimension and element type, and the system uses this value to distribute the array elements block by block in a round-robin fashion over all threads. Revisiting Figure 2.1, the y array is declared with a block size of two, which means that the compiler should allocate the first two elements of y on thread 0, the next two on thread 1, and so on. If the block size is omitted the value defaults to one (cyclic layout like the array x), while a layout of [] or [0] indicates indefinite block size, i.e., that the entire array should be allocated on a single thread. As is the case with C pointers and arrays, a point-to-shared can be used to access elements in a shared array.

Figure 2.2 presents a simple parallel vector addition benchmark in UPC. The three shared arrays are distributed cyclically, and each thread follows the owner-computes rule

Figure 2.2: Vector addition benchmark in UPC

and processes its own local shared data. Other notable features of UPC language include dynamic allocation functions, synchronization constructs, and a builtin **upc\_forall** parallel loop.

### 2.2 The Berkeley UPC Compiler

Figure 2.3 shows the overall structure of the Berkeley UPC compiler, which is divided into three components: the UPC-to-C translator, the UPC runtime system, and the GASNet communication system [16]. During the first phase of compilation, the Berkeley UPC compiler translates UPC programs into C code in a platform-independent manner, with UPC-related parallel features converted into runtime library calls. The translated C code is next compiled using the target system's C compiler and linked to the runtime system, which performs initialization tasks such as thread generation and shared data allocation.

Figure 2.3: The Berkeley UPC compiler

The Berkeley UPC runtime delegates communication operations such as remote memory accesses to the GASNet communication layer, which provides a uniform interface for low-level communication primitives on all networks. GASNet also provides high level non-contiguous remote access methods called the VIS (vector/indexed/strided) functions [17]. The VIS calls accept a list of non-contiguous put/get as arguments, and the communication algorithm is selected at runtime based on network characteristics and transfer parameters. The VIS calls perform message aggregation using GASNet Active Messages, packing non-contiguous data at the source into large packets and unpacking it at the destination.

This three-layer design has several advantages. Because of the choice of C as our intermediate representation, our compiler will be available on most commonly used hardware platforms that have an ISO-compliant C compiler. In addition to the portability benefits, the layered design also means that each component can be implemented and performancetuned individually. The backend C compiler is free to aggressively optimize the intermediate C output, and the UPC-to-C translator can utilize its UPC-specific knowledge to perform communication optimizations. High performance is achieved in the GASNet system by directly targeting the low-level communication interfaces, while still abstracting away the network specific features from the UPC runtime. Finally, most runtime and GAS-Net operations are implemented using macros or inline functions to minimize the overhead introduced by the layered design.

### 2.3 Translation Framework Overview

The analyses and optimizations in this dissertation are primarily implemented in the Berkeley UPC translator [27]. The translator is derived from the Open64 compiler suite [84], an open source collection of optimizing compiler tools. Major components in Open64 include front ends for C/C++/FORTRAN, a loop-nest optimizer (LNO), a global scalar optimizer (WOPT), and an interprocedural analysis framework. Figure 2.4 describes the UPC-to-C translation process applied by the translator. The basic translation process consists of front end processing, backend lowering, and whirl2c transformation:

- Front end: Upon receiving a preprocessed UPC file, the translator's front end parses and type checks the input, and generates a high level WHIRL (Open64's intermediate representation [107]) file. UPC-specific information such as shared types and block size for distributed arrays is preserved in the symbol table, so that the later translator phases can utilize the information in performing optimization and code generation.

- Back end: The primary functionality of the backend is to convert expressions involving a pointer-to-shared into the appropriate runtime library calls. Specifically,

Figure 2.4: UPC-to-C translation process

pointer arithmetic on a shared address is converted into function calls based on the block size of the pointer-to-shared. Similarly, loads and stores of shared variables may require communication and are also transformed into runtime calls. The actual runtime function invoked again depends on a number of factors such as the type being loaded.

• Whirl2c: The final component's job is to convert the WHIRL intermediate representation into ISO-compliant C code, with shared pointers declared as opaque UPC pointer-to-shared types that are defined internally in the runtime system. This enables us to experiment with different pointer-to-shared representations in the runtime system without having to modify the translator. As Section 4.1 shows, whirl2c generates high-level C language constructs when possible (e.g., using struct field accesses rather than pointer arithmetic), so that its output will bear sufficient resemblance to the source code. This stage also provides special support for static and global shared variables, whose storage can not be allocated until runtime to ensure that they are addressable by the network. These variables are instead dynamically allocated and initialized during program startup [41]. Finally, an indirect access scheme is adopted for applications running with POSIX threads so that each pthread gets its own private copy of thread-local variables [42]; whirl2c is responsible for generating the address translation macros when accessing such variables in the program.

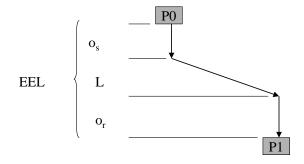

When compiling for clusters, conceptually the translator targets the following one-sided communication interface:

```

sync_t get(void *dest, shared void *s, size_t n);

sync_t put(shared void *dest, void *s, size_t n);

void sync(sync_t handle);

```

Both get and put are nonblocking memory-to-memory operations, transferring n bytes of data and returning an explicit synchronization handle. The sync function blocks until the operation corresponding to the supplied handle completes. Synchronization of a get operation implies the local *dest* (usually a stack temporary) now contains the value of the remote address; synchronization of a put means that the remote *dest* has been updated with the content of the local source. This generic interface can be implemented on top of any

of today's high-performance networks, but also means that compiler has the responsibility of managing handles and issuing synchronization calls at the right place. In particular, messages are not guaranteed to be delivered in order; if two puts are made to overlapping memory locations without a sync in between, the resulting value is undefined.

When the "-opt" flag is passed to the Berkeley UPC compiler, the translator invokes the optimization phase, which includes both the LNO and the WOPT, before the backend lowering of shared expressions. The goal of LNO is to improve the memory performance of a program's loop nests; it includes an extensive data dependence analysis framework and supports well-known loop transformations such as loop fission/fusion, unroll and jam, loop tiling, and vector data prefetching [108]. WOPT operates on individual functions and performs a number of standard optimizations such as copy propagation, partial redundancy elimination, and dead code elimination. At the heart of WOPT is its Hashed Static Single Assignment (HSSA) representation [30], which extends SSA to support pointer aliases and indirect memory operations. The HSSA form is used to implement most of the optimizations, including a partial redundancy elimination framework (SSAPRE) [29, 66].

For our source-to-source transformation, several of Open64's optimizations are not directly applicable, since they produce outputs that are too low-level to be expressed in C (e.g., register promotion [75] and automatic parallelization). Such optimizations are therefore disabled by the Berkeley UPC translator, with the hope that they can be performed equally well by the backend compiler. In addition to employing many of Open64's large repertoire of optimizations in the compilation process, we have also supplied several optimizations that require UPC specific knowledge and could not be performed by a C compiler.

Figure 2.5: Optimization framework for the translator.

Figure 2.5 summarizes the overall structure of the Berkeley UPC translator's optimization framework. At the end of the LNO phase, we add an optimization for the **upc\_forall** parallel loop that helps remove the overhead of distributing the iterations to the executing threads (Section 4.3). Also in the LNO is a loop communication optimization framework, described in Chapter 5, that hoists fine-grained remote accesses out of a loop nest and combines and schedules them to significantly reduce communication overhead. Both optimizations utilize LNO's analysis information, and operate on loops that have the semantics of Fortran DO Loops. Specifically, a DO loop contains a single index variable, and the condition expression is a comparison on the value of the index variable; the lower bound, upper bound, and stride of the loop are all loop-invariant.

A separate optimization at the end of the WOPT phase is designed for fine-grained accesses that do not benefit from our loop optimization framework (e.g., they do not appear inside loops, or have dynamic access patterns). The optimizer performs PRE on both shared pointer arithmetic and shared memory accesses, applies split-phase communication to separate the initiation of an access from its completion, and coalesces individual accesses when appropriate. For the bulk communication routines that are not amenable to static analysis, Chapter 7 presents a runtime-based optimization framework that automatically converts them into nonblocking transfers. The candidates for this optimization (**upc\_memget** and **upc\_memput** calls) are also identified at the end of WOPT.

### **2.4 Memory Consistency Models**

All of the optimizations presented in this dissertation require the ability to reorder remote accesses in a program, either through aggregation or nonblocking communication. In a uniprocessor environment, such compiler transformations must adhere to a simple data dependency constraint: the orders of all pairs of conflicting accesses (accesses to the same memory location, with at least one a write) must be preserved. The execution model for parallel programs is considerably more complicated, since each thread executes its own portion of the program asynchronously, and there is no predetermined ordering among accesses issued by different threads to shared memory locations. A memory consistency model defines the memory semantics and restricts the possible execution orders of mem-

ory operations. More precisely, it determines whether accesses from one thread may be observed to be out of order by another thread, and whether such reordering is legal.

An interesting UPC feature is its support for both a strict and a relaxed memory consistency model. Every shared variable access in UPC is type qualified as "strict" or "relaxed" either explicitly or inferred from pragmas. The relaxed model permits reordering of memory accesses as long as local data dependency is preserved, while the strict model further requires that the effects of reordering can not be observed by other threads. The strict memory model is analogous to sequential consistency in that it requires the actual execution of the accesses on each thread to be consistent with program order, while relaxed accesses only need to preserve local data dependencies. The difference between the two models is visible only in a program with a *data race*, which occurs when two threads access the same memory location with no ordering constraints between them, and at least one of the accesses is a write [81]. For example, reordering on either thread in Figure 2.6 is forbidden if either variable x or y is declared strict, since doing so may produce results that would not happen if execution follows the original program order. If both variables are declared relaxed, however, the compiler can freely reorder the memory operations due to the absence of local data dependencies.

The goal of the UPC memory model is to exploit the tradeoff between programmability and performance; relaxed accesses offer better performance since they can be aggressively optimized by compilers as long as local data dependency on each thread is still preserved, but programmers are left with the burden of ensuring that their code is free of race conditions. While race conditions are likely to be programming errors even in a strict memory model, debugging them in a relaxed model is more difficult due to potential reordering

Figure 2.6: Example of reordering that violates the strict memory model.

performed by the compiler. Optimizations described in this dissertation take advantage of UPC's relaxed model to aggressively reorder and combine shared accesses. Synchronization operations such as barriers and lock/unlock operations are treated as code motion barriers. In a static setting, they are represented as black box function calls that could modify every shared memory location, and in a dynamic setting we simply stop the optimization when encountering a synchronization event. Strict accesses are also modeled as synchronization operations to prevent illegal reordering caused by our optimizations. This is conservative, and more sophisticated parallel analysis techniques could be applied to enable high-level optimizations for strict accesses [26]. We have found our strategy to be sufficient for UPC programs in practice, however, since they rarely contain strict accesses other than the built-in synchronization primitives.

## Chapter 3

# **Experimental Setup**

Portability is an important goal for the Berkeley UPC compiler; since the compiler translates UPC program into C code, it runs on any networking architectures that GASNet communication interface supports, which includes most of today's popular interconnects<sup>1</sup>. Our optimizations should thus be evaluated on different cluster platforms to ensure that they are performance portable. Performance results in this dissertation are collected on the supercomputer clusters listed in Table 3.1, covering a variety of network interconnects and processor architectures. The *Get* and *Put* times in Table 3.1 refer to the cost of executing an eight byte blocking remote access in our runtime, i.e., the roundtrip latency.

We use a number of benchmarks to evaluate the effectiveness of our optimization framework. Most of the benchmarks are written by researchers outside our group, and reflect the kind of UPC programs that our compiler is likely to encounter in the real world. Since each phase of our optimization concentrates on different communication patterns, we also

<sup>&</sup>lt;sup>1</sup>The full list of supported platforms may be found at http://upc.lbl.gov/download/.

| System       | Processor Network |                | Software      | Get(us) | Put(us) |

|--------------|-------------------|----------------|---------------|---------|---------|

| POWER5/LAPI  | 8-way 1.9GHz      | IBM Federa-    | AIX 5.3, IBM  | 9.2     | 8.2     |

| (Bassi)      | POWER5 (111       | tion           | LAPI 2.3.3.3, |         |         |

|              | nodes)            |                | IBM xlc v7.0  |         |         |

| Itanium/GM   | Dual 1.3GHz       | Myricom        | Linux 2.6.18, | 23.3    | 19.7    |

| (Citris)     | Itanium2 (42      | Myrinet        | icc v9.0      |         |         |

|              | nodes)            | LANai XP       |               |         |         |

|              |                   | PCI-X          |               |         |         |

| Opteron/VAPI | Dual 2.2GHz       | Mellanox       | Linux 2.6.5,  | 11.6    | 8.4     |

| (Jacquard)   | Opteron (320      | Cougar Infini- | Pathscale cc  |         |         |

|              | nodes)            | Band 4X        | 2.4           |         |         |

Table 3.1: Machine summary

use different benchmarks to evaluate them. For the framework in Chapter 6, we use benchmarks containing fine-grained irregular accesses that can not be readily vectorized with our loop optimization. Examples include distributed hashtables and dynamic work stealing algorithms. For the automatic nonblocking communication optimization in Chapter 7, we choose programs that use bulk memory copies for communication.

Table 3.2 summarizes the benchmarks used in this dissertation. The Get/Put column refers to the dominant communication type in the program, and LOC represents the number of lines of UPC source code (including comments) for each benchmark. The Get/Put count column refers to the dynamic count of the remote accesses, while the last column reports the average size of each access. The first five benchmarks are communication intensive application kernels with irregular fine-grained accesses.

**Gups:** Gups is a benchmark that performs random read/modify/write accesses to a large distributed array, a common operation in parallel hash table construction. Communication in the benchmark takes the form a[b[i]].

Mcop: The Mcop benchmark solves the matrix chain ordering problem using clas-

| Name       | Get or Put | LOC(1000s) | Get/Put Count(1000s) | Avg. Size(KB) |

|------------|------------|------------|----------------------|---------------|

| Gups       | both       | 0.3        | 490                  | 0.01          |

| Мсор       | get        | 0.4        | 178                  | 0.004         |

| Sobel      | get        | 0.6        | 153                  | 0.001         |

| Psearch    | get        | 0.8        | 2.1                  | 0.05          |

| Barnes Hut | get        | 2.2        | 223                  | 0.004         |

| BT         | both       | 6.7        | 2100                 | 0.15          |

| CG         | get        | 1.5        | 34                   | 33            |

| FT         | put        | 2.5        | 5                    | 131           |

| FT-pencils | put        | 2.5        | 164                  | 4             |

| IS         | get        | 1.1        | 0.352                | 239           |

| MG         | put        | 2          | 19                   | 2.6           |

| SP         | put        | 6.1        | 636                  | 1.7           |

| Gups-bulk  | put        | 0.6        | 8                    | 0.5           |

| CFD        | get        | 14.1       | 123                  | 0.1           |

Table 3.2: Benchmark summary. Results for the last two columns were collected on 16-thread runs, using data from thread zero.

sic dynamic programming algorithms [35]. The shared matrix is distributed cyclically by columns, and communication occurs as part of solving the recurrence relations over all subproblems.

**Sobel:** The Sobel benchmark, whose implementation is described in [43], performs edge detection with Sobel operators (3X3 filters). The image is divided into equal contiguous slices of rows and distributed among the threads, so that communication occurs only when processing the last row of data.

**Psearch:** The Psearch benchmark performs parallel unbalanced tree search [89]. The benchmark is designed to be used as an evaluation tool for dynamic load balancing strategies. Communication takes place when a thread attempts to steal work from another thread.

**Barnes Hut:** The Barnes Hut benchmark [109], ported into UPC from the SPLASH2 benchmark suite, simulates the interaction of a system of bodies (e.g. galaxies or particles)

in three dimensions.

The rest of the benchmarks use bulk memory copies for communication and thus have relatively large message size. Most of them come from the NAS Parallel Benchmarks suite [7], and a brief description is given below.

**BT:** The NAS BT (Block Tri-diagonal) benchmark simulates a CFD application by solving a system of equations for a three dimensional array of points. In this benchmark, a thread issues a large number of strided remote accesses to its neighbor threads.

**CG:** The NAS CG (Conjugate Gradient) kernel is a sparse iterative solver in which a sparse matrix-vector multiplication dominates the execution of the benchmark. The benchmark's implementation is described in [14].

**FT:** The NAS FT kernel solves a partial differential equation on a 3-D mesh using the Fast Fourier Transforms (FFT). The hand-tuned UPC implementation aggressively overlaps communication with computation, by decomposing the FFT computation and communication into smaller pieces instead of performing a global exchange [12]. **FT-pencils** is a variant of the benchmark that further reduces the granularity of the overlap.

**IS:** The NAS IS (Integer Sort) kernel performs a parallel bucket sort on integer keys. Communication is implemented as a global exchange.

**MG:** The NAS MG (Multigrid) kernel uses the Multigrid method on hierarchical regular 3-D meshes. At each level of the grid, communication occurs due to the periodic updates of ghost cell regions.

**SP:** The NAS SP (Scalar Penta-diagonal) benchmark shares a similar structure to the BT benchmark. The benchmark performs a large number of strided remote puts.

**Gups-bulk:** Gups-bulk is a version of the HPCS RandomAccess benchmark that uses bulk communication [77]. Unlike the fine-grained Gups, in this benchmark a thread "looks ahead" the random address stream and pushes them to the remote threads to perform the updates.

**CFD:** CFD is a computational fluid dynamics application that solves the time dependent Euler equations for computational fluid flow in a rectangular computational domain, with the high level data structures and algorithms implemented in UPC.

The UPC versions of BT, IS, MG, and SP are derived from the MPI NAS parallel benchmarks, and their implementations are described in [33, 43].

## Chapter 4

## **Single-Node Performance**

Most optimizations for PGAS programs attempt to reduce their communication time in order to combat the high network latencies on clusters. An equally important yet sometimes overlooked performance metric for parallel programs is the uniprocessor execution time, as most scalable applications will spend substantially more time doing computation instead of communication. Since UPC is designed as a parallel extension of C, serial performance of UPC programs can be further divided into two components: performance on ordinary C code, and performance on UPC-specific features such as access to shared local data and shared pointer arithmetic. For the former, it is important to ensure that the source-to-source translation strategy adopted by our compiler does not cause a performance slowdown by generating less efficient code. In Section 4.1, we examine the code generation quality of our translator in more detail on a number of architectures. The subsequent sections focus on the serial performance of the unique language features in UPC. In Section 4.2, we describe techniques for lowering the overhead of the UPC shared pointer manipulation functions.

In Section 4.3, we present an optimization framework that could eliminate most of the sequential overhead introduced by the **upc\_forall** parallel loop.

### 4.1 Standard C Code Performance

Since the Berkeley UPC compiler adopts a source-to-source translation strategy, serial performance for UPC programs is largely dependent on the quality of the C compiler used to compile the generated C code. On most supercomputers, the vendor supplied compiler typically delivers much better serial performance than gcc, and our translator is carefully implemented so that the generated code can be compiled by a wide variety of compiler and hardware combinations.

While the quality of the backend C compiler is beyond our control, it is still important to ensure that the source-to-source translation does not cause a performance slowdown due to semantically equivalent but less efficient code being produced. Due to the large number of systems supported, our translator does not apply platform-specific tunings in its code generation. Instead, it aims to keep the translated output as syntactically similar as possible to the original source, to minimize the potential performance perturbation introduced by the translation. For example, control structures such as loops and switch statements are preserved in their original form. Due to optimizations performed by the translator and the lack of a one-to-one mapping between its intermediate representation and the C language, it is generally impossible for the translated output to be syntactically identical to the program source. In these cases, our translator produces high-level C code, in the hope that they will most closely resemble the original code in both appearance and performance. For example, pointer arithmetic expressions that are represented as byte offsets internally are converted into symbolic field and array accesses whenever possible, so that the generated code is human-readable and likely similar to the original user code. Multi-dimensional array accesses are reconstructed instead of being flattened into one-dimensional array accesses. The translator also reduces the number of unnecessary casts in its output, to avoid confusing the backend C compiler.

Restrict-qualified pointers and pragma directives are the two most common optimization hints for C code, and they are fully supported by the Berkeley UPC compiler. Our translator utilizes information from restrict pointers to make its alias analysis more accurate, and passes the restrict qualifier in the translated code so that the backend compiler could also benefit from them. All Berkeley UPC specific pragmas share the prefix "#pragma bupc", and any pragma directives not matching this form appear unchanged in the same relative location in the generated C code.

We use four of the NAS parallel benchmarks (CG, FT, IS, MG) from Table 3.2 to evaluate the potential overhead of our source-to-source translation. From the parallel UPC code a purely sequential C version is generated by stripping away the UPC features. All references to the *shared* qualifier and the block size are removed, and the THREADS variable is defined to one while the MYTHREAD variable is defined to zero. Synchronization calls such as **upc\_barrier** are removed, and memory allocation as well as string copy functions are converted into their C equivalents (e.g., **upc\_alloc** becomes **malloc**, and **upc\_memget** becomes **memcpy**). Similarly, a **upc\_forall** loop is directly translated into a for loop.

The PathScale compiler v2.4 [87] is used for the Opteron cluster, Intel compiler v9.0 [57] for the Itanium cluster, and IBM XL C v7.0 [110] for the POWER5 cluster. The standard

-03 flag is used on all three platforms.

For reference, we also include the NPB3.2 Fortran/MPI implementation of the benchmarks, compiled with the Fortran compiler from the above compiler suites using the -O3 flag. Compared to C, Fortran employs much stricter aliasing rules (e.g., arguments to function calls may not be aliased), which makes it more amenable to compiler optimizations. To allow for a fair performance comparison between the two languages, we judiciously apply the restrict qualifiers in both the C and UPC version to assist the compiler's pointer analysis. Since the uniprocessor execution time of the four benchmarks, like many scientific applications, is dominated by a few computation loops, software pipelining [68] is very important to the overall performance. As dependence analysis for C is generally less precise than that for Fortran, we also assist the optimizer by supplying the ivdep pragma to loops so that they can be effectively pipelined.

Figure 4.1 presents the results for our experimental configurations. The figure reports normalized performance, by dividing the MFLOP rate of the C/Fortran run over the MFLOP rate of the UPC run on a given platform; a value greater than one thus indicates performance superior to UPC. There are no Fortran results for IS because the benchmark is implemented in C in the standard NAS benchmark release. As the graph shows, the uniprocessor performance of C and UPC is very close, with the C code outperforming the UPC version by approximately 2.5% on average. Since the UPC code contains additional parallel constructs that may incur superfluous overhead in serial execution, this suggests that our compilation framework suffers very little performance loss from the source-to-source translation. The Fortran code outperforms the C and UPC versions in general, owing to the fact that Fortran is designed to be more amenable to high degrees of optimization, espe-

Figure 4.1: Serial performance comparison: UPC v. C v. Fortran. Class A input is used.

cially for scientific code. The largest performance gap occurs on the FT benchmark, where the Fortran version outperforms the UPC code by an average of about 50%. This large gap can be attributed to the different implementation of complex arithmetic. In the Fortran code, complex numbers are implemented using the builtin complex type, with addition and multiplication of two complex numbers directly expressed using the language-supplied operators. In the C version on the other hand, the complex number is implemented as a struct of two doubles, and complex arithmetic operates on the two fields explicitly. Even though the two versions perform semantically equivalent operations on the complex numbers, the compilers we have tested are much more effective at optimizing the Fortran code.

### 4.2 Performance of Pointer-to-shared Operations

A pointer-to-shared in UPC needs three logical fields to fully represent the address of a shared object: thread\_id, address, and phase. The thread\_id indicates the thread that the object has affinity to, the address field stores the object's *local* address on the thread, while the phase field gives the offset of the object within its block. Figure 4.2 demonstrates how the fields in a pointer-to-shared are used to access a shared value.

Figure 4.2: UPC pointer-to-shared components.

When dereferencing a pointer-to-shared, the compiler needs to first determine whether the shared object is local or remote. A local shared access is thus generally slower than accessing it through a local pointer, due to the extra branch involved in determining an object's locality. Address arithmetic on pointers-to-shared will also be inevitably slower compared to their counterparts on local pointers, since a pointer-to-shared contains three fields, all of which may be updated during pointer manipulations. Experienced programmers typically avoid this overhead by casting the pointer-to-shared into a local pointer first before accessing it. From a productivity standpoint, however, it is important to keep the overhead of these pointer-to-shared operations low, so that programmers would not be forced to keep two pointers (one local and one global) for the same data. In Chapter 6, we will show that such overhead can be amortized through compiler partial redundancy elimination; here we present runtime techniques that reduce the individual overhead of these operations.

By default the Berkeley UPC compiler uses a packed eight byte integer to represent a pointer-to-shared; this allows pointer-to-shared operations to be more efficiently compiled since the pointer-to-shared format will fit in the registers of most modern high-performance computing platforms. Only when an application needs either a large amount of shared memory (> 4GB per thread) or more than a few thousand threads does a programmer need to switch to a struct-based representation.

Another important runtime optimization for pointer-to-shared is the "phaseless pointer" representation. A UPC pointer-to-shared can be classified into three categories based on its declared block size: *block cyclic* for block size > 1, *cyclic* for block size = 1, and *indefinite* for block size = 0. For the frequently used cyclic pointers, which have block size one, the

phase field can be eliminated since its value is always zero. Similarly, indefinite pointers can omit their phase since all elements reside in a single block. Cyclic and indefinite pointers are therefore named *phaseless*, and our compiler exploits this knowledge to enable more efficient operations for them. For cyclic pointers, shared pointer arithmetic can be implemented with a modulo (for updating the thread id) and a divide (for updating the address) operation, while for indefinite pointers it can be implemented directly as a regular pointer addition, as the thread id never changes.

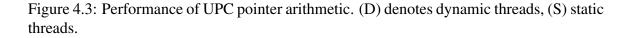

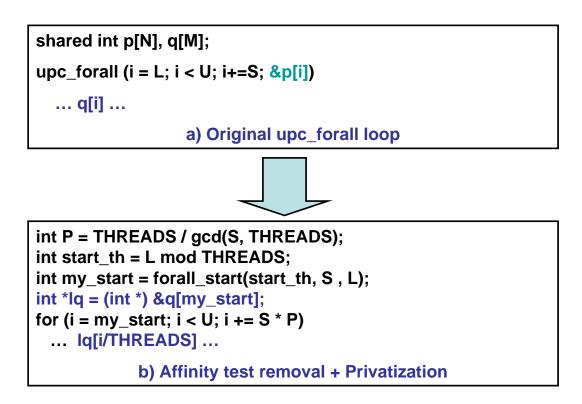

Figure 4.3 presents UPC shared pointer arithmetic performance (ptr + int) on three

platforms from Table 3.1, using the same compilation environment as described earlier in Section 4.1. Two threads were used in the experiments. The variables in the benchmark are declared to be volatile so that the C compiler will not attempt to optimize away the operations. Due to the phaseless pointer representation, pointer arithmetic for cyclic pointers is significantly faster than that for the generic block cyclic pointers on all platforms. Furthermore, pointer addition for indefinite pointers is as fast as regular C pointer arithmetic since they use the same sequence of instructions. For the block cyclic and cyclic pointer we observe a significant performance improvement moving from the *dynamic THREADS* environment to the *static THREADS* environment. The reason is that both types of pointers perform modular arithmetic, which can be more efficiently optimized by the C compiler if the number of threads is a compile time constant (e.g., strength reduced into shift operators when THREADS is a power-of-two). Thus, for programs that perform a non-trivial amount of (block) cyclic pointer-to-shared arithmetic, the number of threads should be specified at compile time. Indefinite pointers, however, are not affected by the dynamic versus static thread setting.

Figure 4.4 presents the cost of a UPC shared local access (\*p) to an eight-byte double. It is clear from the figure that accessing local data through a pointer-to-shared incurs substantial overhead due to the extra branch needed to determine the pointer's affinity. The optimization framework described in Chapter 6 can help lower this performance penalty by eliminating some of the redundant locality checks, and an analysis that statically determines which accesses are guaranteed to be local can also be very profitable. In earlier work, we have also compared the performance of shared local accesses between the Berkeley UPC compiler and the HP UPC compiler, and found that the Berkeley compiler is slightly slower due to the source-to-source translation [25].

#### Overhead of shared local access

Figure 4.4: Performance for UPC shared local access

### 4.3 Optimizing UPC Forall Parallel Loop

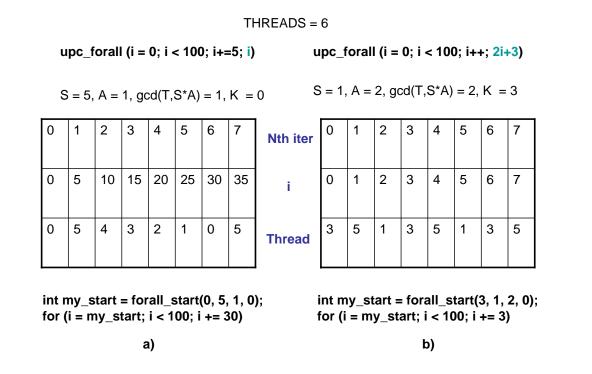

To simplify the task of parallel programming, UPC includes a builtin **upc\_forall** loop that distributes iterations among the threads. The **upc\_forall** loop behaves like a C *for* loop, except that the programmer can specify an *affinity* expression whose value is examined before every iteration of the loop. The affinity expression can be of two different types: if it is an integer, the affinity test checks if its value modulo THREADS is the same as the id of the executing thread; otherwise, the expression must be of pointer-to-shared type, and the affinity

test checks if the running thread has affinity to this address (i.e., upc\_threadof(aff exp) is equal to MYTHREAD.). The affinity expression can also be the continue keyword or simply omitted, in which case the affinity test is vacuously true and the loop behaves as if it is a C for loop. A thread executes an iteration only if the affinity test succeeds. Figure 4.5 b gives the semantic definition of the forall loop in part a, where the loop body is executed only if the affinity test succeeds. The forall loop is a collective operation, which means that all threads will execute the loop. Its controlling and affinity expressions must also be *single valued* [1], meaning that all threads agree on which threads execute each iteration.

UPC forall loops provide a convenient syntactic sugar for thread coordination and the prevention of inadvertent remote accesses, but its primary drawback is the runtime overhead incurred by executing the affinity tests in all loop iterations. In a straightforward translation shown in part b of Figure 4.5, the affinity tests have to be executed on each iteration by all threads, and the presence of the branches in the loop can also inhibit many useful loop optimizations. The *mod* operation in the figure performs modular arithmetic. Fortunately, while their values naturally change from iteration to iteration, affinity expressions can often be derived directly from loop induction variables; for such common special cases, we can eliminate the runtime affinity tests by incorporating their thread-iteration mapping constraints into the loop's bound and stride.

#### 4.3.1 Affinity Test Removal

The goal of the optimization is to transform the forall loop into an equivalent for loop with the affinity test eliminated. Our optimization operates on forall loops, and by definition their lower bound (L), upper bound (U), and step (S) must all be loop invariant. We first upc\_forall (i = L; i < U; i+=S; A\*i + B)

loop body;

a) Original upc\_forall loop

for (i = L; i < U; i+=S)

if (((A\*i + B) mod THREADS) == MYTHREAD) {

loop body;

}

b) Straightforward translation</pre>

```

int P = THREADS / gcd(S*A, THREADS);

int start_th = (A*L + B) mod THREADS;

int my_start = forall_start(start_th, S, A, L);

for (i = my_start; i < U; i += S * P)

loop body;

```

c) Optimized translation

Figure 4.5: upc\_forall loop affinity test removal.

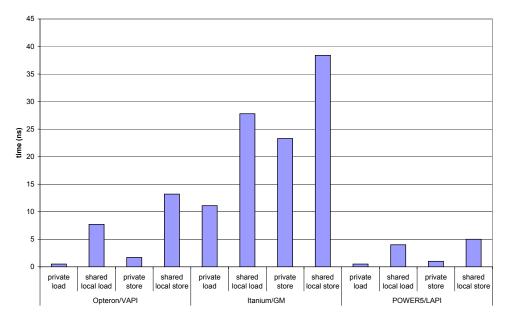

consider the case when the affinity is an integer expression linear to the loop induction variable; in other words, it is of the form Ai + B, where *i* is the induction variable and both *A* and *B* are loop invariant constants. For notational convenience, let K = AL + B, or the thread that executes the very first iteration of the forall loop, and let T = THREADS. The sequence of the threads executing the iterations of the forall loop is then  $\{K, K + S *$  $A, K + 2 * S * A, ...\}$  (mod *T*), since the affinity expression is incremented by S \* A in each iteration. Following the rules of modular arithmetic, the sequence will repeat every  $P = T/\gcd(T, S * A)$  iterations, where gcd is the greatest common divisor function. Furthermore, a thread M will be in the sequence if and only if (M - K) | gcd(T, S \* A). Figure 4.6 illustrates how the formula can help discover the distribution of the forall loop iterations among the threads. In a), gcd(T, S \* A) is 1, so each thread executes every T iteration of the forall loop. In b), the gcd is no longer 1, and thus only thread 3, 5, and 1 participate in the forall loop, with the sequence repeating every three iterations.

Figure 4.6: Examples of forall loop iteration to thread mapping. The original forall loop appears at the top, while the result C code is at bottom.

Once the mapping of thread id to iteration is statically determined, the affinity test can be eliminated as shown in part c) of Figure 4.5. In the figure, start\_th stores the id of the thread executing the first iteration, or the K variable in the previous paragraph. The

function forall\_start computes for a thread the value of i at the first iteration that it will execute. This can be computed by scanning through the sequence K + S \* A until we find an element equal to MYTHREAD. For threads that do not execute the forall loop at all, the function returns a value larger than U, so that the thread will never enter the transformed loop. The step of the new loop is changed to S \* P, to reflect the fact a thread is executing the body of the original forall loop every P iterations.